Gas Wilson

-

Постов

141 -

Зарегистрирован

-

Посещение

-

Победитель дней

9

Сообщения, опубликованные Gas Wilson

-

-

On 7/22/2024 at 12:49 AM, 1891ВМ12Я said:

Подскажите пожалуйста, где можно увидеть документацию на EQ6HL45 - это китайские клоны, они совместимы с ISE? Документации на клон AD9245 тоже не вижу, может не загрузилось по какой то причине? Где это всё купить можно?

Добрый день. EQ6HL45 совместима по пинам с Spartan, внутренняя структура - своя. Своё ПО для разработки (eLinx). Клонов Spartan (поддерживаемых ISE) насколько мне известно - нет. По АЦП/ЦАПам - если интересно, могу поискать документацию. Купить можно напрямую у китайцев, либо в Микротерре ([email protected])

-

-

Новая версия PDS - 2023.2.SP3

Spoiler2 SP2 features

ü Fix the problem of excessive runtime size in the Compile stage caused by Multi-assignment pattern

ü Fix the problem of false compile error when the actual parameter is left vacant during instantiation of unpacked port

ü Fix the problem of incorrect relative placement of DFF and LUT6CARRY PACK with position constraints during layout, which leads to constraint check error

ü Fix the problem of post-simulation and design golden inconsistency caused by DRM post-simulation mapping error (PG3T500, PG3T600, PG3K1000P involved)

ü Support the use of DVIO when debugcore is waiting for trigger

ü Fix the problem that PDS cannot connect to License Server after setting proxy server

ü Fix the problem of poor timing caused by too long synthesis level under strict timing constraints

ü Add Timing-4120 and Timing-4121 Critical warning for the scenario where create_clock is used to create constraints and source objects are not ports

ü Fix the disconnection of GTP_APM_E4 in the Map stage CEY1 and RSTY1 cause the output of the board to be 0 (involved in PG3T600P and PG3K1000P)

ü Fix the problem that the output of GTP_APB is deleted in the sim.v netlist when there is no connection logic

ü Fix the problem that the clock power consumption reported by PPC is too small (involved in Komos2, Logos2, and Titan2 series)

ü Support the configuration that the 0x425 bit[5] of the corresponding channel in the HSST register is 0 before scanning (involved in PG3T500)

ü Fix the problem of crash when APM absorbs registers with initial values

ü Supports adding genblk flags to generate signals through parameter control. Fixed the issue that the floating port of GTP_HPIO_PHY_SEQUENCER is grounded during the synthesis phase, causing routing failure (involving PG3T500)

ü Fixed the abnormal result of monitor board loading (involving PG2T70H)

ü Optimize timing power consumption data (PG3T500 involved)

ü IP update:

DRM/HRM IP (Titan3)

(1) Update the HRM288K cascade algorithm of dpram, sdpram, and fifo sub-IPs, and support mixed data bit width function.

(2) Optimize the clock polarity reversal, output register enable signal, and output register configuration item linkage logic in the parameter configuration interface.

(3) Modify the incorrect synchronous FIFO read and write threshold level timing diagram in the UG document.

(4) UG update.

3 SP3 Features

1) BUG fixes

ü The detailed routing stage supports multi-level logic hold violation repair function

ü Fixes the problem that a pop-up window warning will appear when switching process and tempgrade when there is an IP module in PPP (involved in PG3T500)

ü Fixes the problem that when differential IO is used as the clock input source, the layout only considers the single-ended position in the clock planning stage, resulting in layout failure

ü Optimizes the clock skew of PG3T600P and PG3K1000P

ü Fixes the problem that the include_generated_clock parameter added in set_clock_groups does not take effect on the generated clocks of all levels under the same source clock

ü Support Compile error Verilog-4146 interception when there are modules with the same name in different design files and the configuration option "Allow Duplicate Modules" is not checked

ü Fixed the issue that after the asynchronous FIFO IP comes with sdc constraints and the same IP is instantiated repeatedly, some of the instantiated IP constraints do not take effect

ü Supports projects with unconstrained or partially constrained IO, and reports an error and exits during the bitstream generation phase

ü Fixed the issue that the SVF file generated by the Configuration tool is incorrect when the Flatten mode is selected when generating a cascaded bitstream

ü Fixed the problem that the delay function does not take effect due to the unprocessed idly_dis, odly_dis and tdly_dis ports of the IDELAY/ODELAY model (involving PG3K1000P and PG3T600P devices)

ü Add fan-out restrictions to the ZGM[0]/[1] reflection ports of SRB. If the number of nodes passing through ZGM exceeds 20, Critical Warning: Route-2045 will be reported during the Route Optimize stage (involving Logos2, Titan2, and Kosmo2 series)

ü Update the timing data of some archs of IOLHR (involving Logos2, Titan2, and Kosmo2 series)

ü Narrow the scope of the check for create_clock constraints on non-clock ports to reduce redundant alarms

ü Fixed the problem that the power consumption is abnormally 0 when the DRM mode is SDP and the A\B bit width is 32 in PPP (involving PG3T500)

ü Fix the Compile crash caused by using genvar variables without initial values

ü Fixed the issue of falsely reporting critical warning STA-3004 when clocks from the same source are propagated to the location where a generate clock exists

ü The default value of the Place&Route configuration option PnR Timeout(min) in Project Setting is changed from 720 to 0

ü Fix the inconsistency between the BUS_KEEPER settings in the PDS report and UCE

ü Added HSLVCMOS33/HSLVTTL33 level standards and updated the IO power consumption model (involving PG2T390H)

ü Fix the problem of not taking the positive and negative of the expression when adjusting the expression order during expression optimization

ü Fix the abnormal flashing of the Done light on the upper board after checking the Over Temperature Shut Off function of PG2K400

ü Fixed the Synthesize phase crash caused by not correctly identifying the syn_direct_reset attribute on net

ü Optimize the alarm scenario of C:SDC-2032. When the create_clock constraint and uncertainty constraint exist on the clk pin of FF/APM/DRM at the same time, a serious alarm C:SDC-2032 will be generated, and the uncertainty constraint will not take effect

ü Update the HRM timing model (PG3T500 involved)

ü Enhance the readability of parameter values in compile run.log

ü Delete the IO standard "TMDS" (Logos2, Titan2, Kosmo2 involved)

2) GTP changes

ü Add support for GTP_MONITOR (PG3T500 involved)

-

2

2

-

-

Коллеги, делюсь документацией на модули на базе eHiway EQ6HL45 (аналог Spartan 6) + клоны АЦП AD9245 и ЦАП AD9764

TTP013 Three-axis Fiber Optic Gyroscope Universal Signal Processing SIP Circuit Product Manual 250625-eh.pdf TTP014 Single-axis Fiber Optic Gyroscope Universal Signal Processing SIP Circuit Product Manual 240625-eh.pdf

-

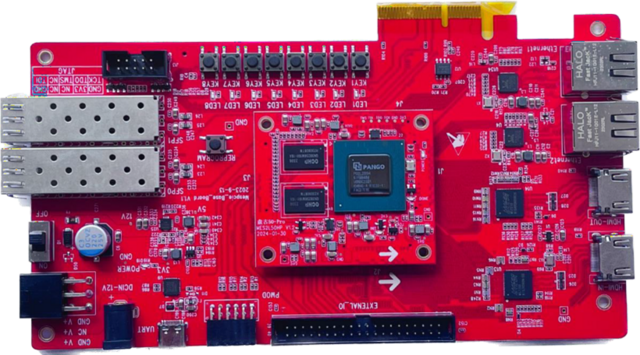

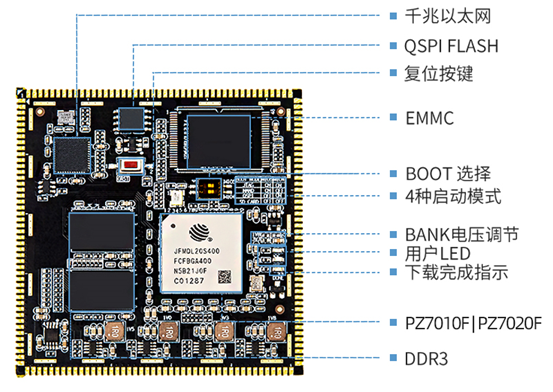

Вышла отладка и Som модуль на базе PG2L200H

MES2L484 Series Development Board Hardware User Manual V1 (microterra.ru).pdf

-

1

1

-

-

On 5/16/2024 at 1:00 PM, makc said:

Как дела с errata на эти чипы? Или она как обычно недоступна?

Уточнил с производителем - у них нет errata отдельно. Максимум что есть - список багов которые публикуются в описании релиза PDS

Даташит на Titan 2 версии 1.5. Изменения не критичные.

DS05001 Titan2 Series FPGA Device Data Sheet 1.5_microterra.ru.pdf

-

2

2

-

-

Вышла в серию отладка + SoM на базе Kosmo2 PG2K400. Сами чипы Kosmo 2 так же стали доступны к заказу.

-

1

1

-

-

PG2T390H-FFBG900 power consumption test report

PG2T390H-FFBG900 device power consumption test report V1.1_microterra.pdf

-

2

2

-

-

23 hours ago, IlyaKw said:

Доброго времени суток, уважаемые.

Не мог бы кто-нибудь помочь с BSDL файлами для PangoMicro FPGA?

Прочел на страницах этого форума, что они есть в составе пакета, но искать, качать пакет софта для разработки смысла большого не вижу, не нужно оно.Ситуация следующая: есть плата с FPGA этой компании, идентифицировать тип FPGA по маркировке не представляется возможным, поскольку на корпусе всего две надписи

- MBG324 (тип корпуса)

- CCA60-С 2017 (ID FPGA какой-то и дата производства, наверное)

Через JTAG удалось установить принадлежность данной FPGA к Pangomicro

Info : JTAG tap: gw1n.tap tap/device found: 0x20303899 (mfg: 0x44c (Shenzhen Pango Microsystems Co Ltd), part: 0x0303, ver: 0x2)

Хотелось бы идентифицировать тип, это ради того, чтобы понять, можно вместо нее поставить какой-нибудь Xilinx в том же корпусе.Заранее спасибо!

А если не cекрет - зачем ставить Xilinx в том же корпусе?

-

UG042003 HMIC_S IP User Guide V1.13b

UG042003_HMIC_S_IP_1.13_microterra.pdf

Список доступных IP core и их версии

Версии IP coreLogos2

ADC 1.9

HMIC_S 1.13b

FFT 1.2

FIR 1.2

HSST 1.10

LVDS 1.3a

PCIe_Gen2 1.7

QSGMII 1.3

SDI 1.3

SEU 1.6

SGMII 1.4

SGMII_LVDS 1.1

XAUI 1.4Logos

HMIC_H 1.2

HMIC_S 1.6

HSST 1.5

PCIe 1.4

QSGMII 1.0

SEU 1.2b

SGMII 1.2

XAUI 1.1b

Titan2

10G MAC 1.4

12G-SDI 1.2

ADC 1.4

HMIC_S 1.10

FFT 1.2

FIR 1.2

HSSTHP 1.11

iScan 1.7

LVDS 1.3a

PCIe 1.6

QSGMI 1.0

SEU 1.5a

SGMII 1.2

XAUI 1.2

-

Новая версия PDS - появилась поддержка VHDL в ADS

-

1

1

-

1

1

-

-

34 minutes ago, Xagen said:

а как этот проект моделировать? У меня вообще серьезные проблемы с моделированием. Ни одно IP ядро не моделируется. Все падают с ошибками на этапе компилирования в modelsim или questasim. Судя по логам какая-то проблема с зашифрованными исходниками. Ругается на синтаксис в зашифрованном регионе. При этом в самом PDS синтезируется.

Пришлите лог

-

Вот ещё проект с RGMII для PG2L100H. Тут используют ip core от Titan

PG2L100H Gigabit Ethernet Application Guide_innek.pdf pgr_pg2l100h_ethernet_eval_v2.0.rar

-

1

1

-

1

1

-

-

On 2/28/2024 at 6:42 PM, cdg said:

А нет ли случайно UG052008_Titan2_10G MAC+PCS_IP_UserGuide.pdf на английском?

-

2

2

-

-

2 hours ago, cdg said:

Благодарю, способ то известный, на английский гуглом можно инепосредственно pdf переводить - теряется оглавление и т.д., но уже можно работать. Я обратился к @Gas Wilson как к источнику уже оттранслированых/переведенных файлов, возможно он сможет помочь в решении этого вопроса.

В процессе перевода. Постараюсь закончить на этой неделе. Приехало много документации по Kosmo2 - занят пока ею.

Не помню, выкладывал ли тут эти файлы.

10G Ethernet MAC Application Guide_v1.1_innek.pdf 10GBase-R Application Guide_v1.0_innek.pdf

-

2

2

-

-

Документация по отладчику

-

1

1

-

1

1

-

-

13 minutes ago, makc said:

Перенёс в /pub/FPGA/_Astrong_

Как-то неуловимо напоминает Fudan... Подход тот же, номенклатура тоже похожа.

Да все они в итоге CETC58 🙂

-

On 1/10/2024 at 9:59 AM, makc said:

Кто автор этого клона? Где брать патчи и остальную документацию? Какие сроки/цены?

Патчи залил на /upload/FPGA/_Astrong_

Автор похоже тот же - Wuxi Esiontech Co Ltd совместно с CETS 58

По ценам - это к менеджерам 🙂

-

Вариант клона Xilinx XC7VX690T. Из-за техпроцесса - отличия по питанию (Vccint 0.85V,Vmgtavcc 0.95V), отличия по таймингам (заменить spd файл), нужен патч на DDR3, нужен патч на GTX

-

-

-

1

1

-

-

On 11/17/2023 at 1:22 PM, aledo2100 said:

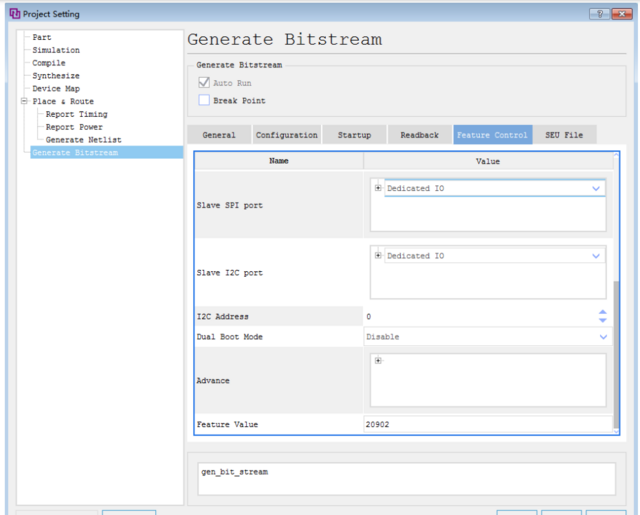

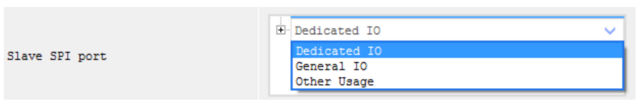

Добрый день всем

Использую CPLD PangoMicro серии Compact

Подскажите, пожалуйста, возможно ли использовать внутренний SPI ("integrated SPI (hard core)") для работы PCG2KG6 как slave и обмениваться данными с микроконтроллером по SPI постоянно ? Никак не пойму, Как это сделать. Использую пины DIFFI_B2_21P/CFG_CLK, DIFFI_B2_21N/MISO_SO, DIFFI_B2_1N/MOSI_SI, DIFFI_B2_1P/FCSI_N, соответственно. Подошел бы вариант использовать эти пины как стандартные входы, так как регистр сдвига внутри реализовать удалось. Но интересно использовать или встроенный SPI или хотябы те же пины. (вариант использовать другие пины удался и не подходит)

ЗЫ: Я начинающий - мог чтото не предусмотреть.

буду рад любой информации на эту тему.COMPACT series CPLD SPI hard core reference design instructions_innek.pdf SPI_HARDCORE_DEMO.zip

-

1

1

-

-

On 11/17/2023 at 1:22 PM, aledo2100 said:

Использую CPLD PangoMicro серии Compact

Подскажите, пожалуйста, возможно ли использовать внутренний SPI ("integrated SPI (hard core)") для работы PCG2KG6 как slave и обмениваться данными с микроконтроллером по SPI постоянно ? Никак не пойму, Как это сделать. Использую пины DIFFI_B2_21P/CFG_CLK, DIFFI_B2_21N/MISO_SO, DIFFI_B2_1N/MOSI_SI, DIFFI_B2_1P/FCSI_N, соответственно. Подошел бы вариант использовать эти пины как стандартные входы, так как регистр сдвига внутри реализовать удалось. Но интересно использовать или встроенный SPI или хотябы те же пины. (вариант использовать другие пины удался и не подходит)

по умолчанию проект не размещается на этапе Place and route с ошибкой "E: Place-0084: CASCADED_GLOBAL_CLOCK: the driver SPI_CLK_ibuf/opit_1 fixed at IOL_94_49 is unreasonable. Sub-optimal placement for a clock source and a clock buffer."

это решается добавлением constraint'а "define_attribute {n:SPI_CLK} {PAP_CLOCK_DEDICATED_ROUTE} {FALSE}" ,

однако тогда пины не работают и варнинги:Добрый день, а тут настройки меняли?

-

Питание ПЛИС

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Копии LTMок

AST4644, four outputs

AST4622, dual output, small size

AST4613, single output, high current 8A

AST4650, dual output, high current

AST4700, dual output, high current, with digital function

AST8056, lift product, wide input and output range

AST8027, step-down product, wide input voltage range up to 60v

AST4613I Data Sheet-V2.3.pdf

AST4700I Data Sheet-V2.3.pdf

AST8055I Data Sheet-V2.2.pdf