-

Постов

169 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Goofy

-

-

-

Удивляет то, что фотоплоттер воспринимает адекватно плату, которая выведена в гербер напрямую, когда там Solid. Без копипаста в технологичесий файл.

Насколько понимаю компоновка нескольких плат в народе зовётся мультиплицирование.

Мультиплицирование, в случае с альтиумом, коллегами обычно делается CAM программой или тем же копипастом ?

-

Впервые для себя вникаю в процесс изготовления МПП.

Та контора где всё происхоит всегда работала с пикад2002 и не имела проблем с фотопечатью и сверловкой.

Я же свой проект заложил сразу в АД.

Возникают проблемы при печати фотошаблона ( копии требуемой платы + технологиечкая рамка и реперы ).

Причём, CAM350 не отображает еденичные небольшие полигоны. Камтастик альтиума всё отображает корректно.

Фотоплоттер RP-212, если не ошибаюсь. Так вот, даже при препросмотре софт этого фотоплоттера полигоны не прорисовывает вообще, соответственно и не печатает.

Тогда как гербер без рамок и реперов (еденичная плата в чистом виде) - читается адекватно.

Каким образом коллеги решают проблему?

Как вообще идёт адекватная компоновка плат на заготовку? Тут всегда копипастом. И похоже собака в этом зарыта

-

Тогда в качестве dummy передачи использую PCS = 1110 и SPI_CSR3 сконфиругированный на бодрейт, например, в 4 раза больше дежурного, получаю паузу в 2 такта.

Только из примеров по ссылке роль LASTXFER не уловил. В формуле приводят, в примере буффера нет. По логике то он вообще не нужен в данном случае. Или ошибаюсь ?

-

LASTXFER в этом плане не поможет ?

-

Самый очевидный и гарантированно рабочий вариант - повесить CS всех десяти на ногодрыгание.

Однако хотелось бы поизящнее, с DMA, чтобы не отвлекаться по пустякам.

Планирую поставить на NCS0-NCS3 декодер вроде 74HC154.

SPI Устройства как раз можно разбить на 4 группы, с специальной конфигурацией для кажой.

Интересует опыт работы с SPI AT91SAM9G20 или AT91SAM9260 с установленым флагом PCSDEC в SPI_MR и декодером на NCS0-NCS3

( название флага читается уже с подозрением :) )

На какие могу нарваться проблемы?

-

програмно второй UART ( нормальный не получить) это с ограничениями, компромисами и всеравно криво.

у нас норально не получилось, по понятным причинам. Пришлось перейти на 162_ой.

А полноценный не нужно. Нужно медленно писать, редко и медленно читать

-

Контроллер Mega8, нужет 2й UART

Везде где приходилось встречать упоминание о софтовом УАРТе, старт бит ловят компаратором.

Может потому что этот переферийный модуль более распостранён?

Мне бы удобнее было ловить от внешнего прерывания: INT0, INT1.

В чём я при этом буду неправ ?

-

По первой ссылке. Вариант дебильный, конечно, но вполне работоспособен. Используйте на здоровье.

Ничуть не дибильный, на 60кгц работал без особых затей. Я разве что подогнул обработку очереди чётотам_poll за один вызов

-

Запустил давно, забыл отписать

Устройство с разводкой памяти выше полностью работоспособно. Частота 100Мгц.

-

Заказывал в Элитане, пока что под опытный образец - 2шт. (второй прозапас)

Чип маркирован как KENDIN ..

Проблем никаких не замечено, пока что подпаяны и проверены 1й и 4й порты. В остальных пока небыло нужды, но на досуге и их протестирую.

( Все внешние 4 порта заведены в отдельный DHR-26 разъём )

-

WE и RE на схеме были перепутаны.

Разворот в противоположную сторону параллельных проводников на схеме сбил с толку.

Сейчас всё работает

-

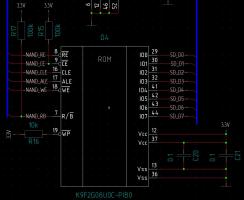

Пускаю устройство с K9F2G080A NANDом на борту

Не sam-ba (2.6, 2.9), ни u-boot 1.3.4 чип не видят.

Самба 2.6 выдаёт

-I- ReadId

-I- NandFlash ID : 0x58580458

-E- NandFlash not supported...

u-boot

DRAM: 64 MB

NAND: No NAND device found!!!

Схема подключения, как я понимаю, типовая (NAND_CE - PC14, NAND_RB - PC13), соответствует пинам инициализируемым u-boot для at91sam9260ek.

К сожалению банальные причины вроде непропая или замыкания между ножками - отпадают. Всё проверил

По осциллограммам кроме наличия присутствия (каких то) сигналов на управляющих линиях (CE RE ALE CLE) ничего не разглядишь.

На R\B тишина, что для чтения ID, как я понима, норма

Плата на 6ти слоях, полигон под всеми линиями имеется. (SDRAM работает на 100МГц)

Однако до NAND у меня длина управляющих линий больше длин линий данных сантиметров на 4.

Грубо говоря 0.5нс задержки, но ведь и тайминги это растягивает в +, а в датащите минимальный указан

Как NAND чипы переносят запайку феном? Есть вероятность погубить? Температура 240*

За что посоветуете подёргать, чтобы нащупать проблему?

JTAG на плате выведен площадками, как раз для такого рода затыков...

Осцилограф только с1-65а, придёться снижать частоту мегагерц до 10

-

Спасибо за совет!

u-boot теперь видит сеть

-

И на Link is down, тоже можно внимание не обращать?

-

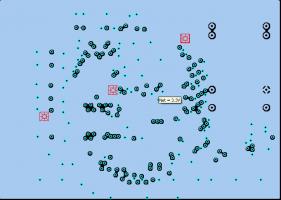

Запускаю u-boot под связку AT91SAM9260 и KSZ8995.

Версия 1.3.4, патч от www.linux4sam.org

Закомментировал CONFIG_RMII

Поменял выставляемый PHYADDR на 0x05, что соответствует пятому порту подключённому через MII

macb_eth_initialize(0, (void *)AT91_BASE_EMAC, 0x00);

Сам свич подключён аналогично схеме приведённой в начале ветки.

Дополнительно подключены MDC и MDIO

Для тестов выпаял подтяжку с PS1, чтобы свитч запустился автоматически.

Свич запускается, пинги через Port1 <-----> Port4 ходят, линки горят

u-boot же выдаёт:

Net: macb0 macb0: Starting autonegotiation... macb0: Autonegotiation timed out (status=0x7808) macb0: link down (status: 0x7808)

Возвращаемый статус есть дефолтные значения MII status, ни флага активности линка, ни флага окончаения работы авто-договаривалки не наблюдается.

Может есть какие то особенности работы через MII SW ?ведь фактически никакого физического слоя там нет, только MAC5 мост.

-

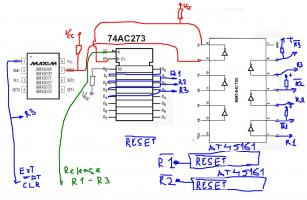

Прикладываю на критику художество задуманного

Выход сторожевого таймера через инвертер попадает на такт триггеров, чтобы смена R1-R3 происходила по спадающему фронту сигнала сброса.

Каждый последующий такт сброса будет на R1-R3 давать ноль, отключая от загрузки AT45-е. После 3го такта отключится сам WDT.

Система сброситься в исходное только от внешних сигналов, либо после снятия питания.

-

Обычно в элитане всё заказываю, а там как раз позиция за 2000р...

Заказывать всё в разных конторах неудобно...

Накрайняк для отладки куплю коммерческий.

-

в моём случае применение контроллеров с flash исключено

-

Используемый процессор SAM9260

Требуется в случае зависания программы загружаемой из датафлэш на NSC0 перезагрузить систему целиком, при этом опуская RESET на первом Dataflash в 0. В этом случае загрузка пойдёт по NSC1. Если снова срабатывает внешний сторожевой таймер, то требуется отключение обеих dataflash. А дальше задействуется NAND или происходит отключение сторожевого таймера и система готовится бутится через DBGU.

Существуют ли готовые решения?

В противном случае потребуется воспользоваться сборкой триггеров, инвертировать их сигналы (чтобы после сброса триггеров все RESET линии выставлялись в 1), как тактовый сигнал пользовть спадающий фронт RESETа процессора от сторожевого таймера

-

Чем можно объяснить разброс цен почти на порядок на чип K4S561632H-UI75 ?

В одном случае это порядка 2к р. в другом 300р, в рознице.

-

Система работает под QNX, софт для встроенного MAC контроллера имеется и функционирует в связке с KS8721BL. (На отладочной плате)

По простому в схемотехнику дополнительно к KS8721BL нужно заложить switch микросхему, подключить входы\выходы обеих через конденсаторы, пользоваться проверенными для KS8721BL драйверами. При этом опционально перемычками дать возможность подключаться KS8721BL к трансформатору или к свичу через конденсаторы.

В данном случае вся "простота", очевидно может привести к повышенному потреблению и к потере целостности сигналов в цепях конфигурационных перемычек.

Похорожему нужно подключиться к MII самого свича KS8995MA.

Однако при этом можно нарваться на проблемы с софтом.

Учитывая жёсткие сроки, не могу окончательно принять решение относительно того, какое решение лучше: гарантированно рабочее - уродливое или хорошее с мешком котов.

На данный момент нет опыта по разработке изернет устройств.

Хочу вас попросить подтвердить, опровергнуть и дополнить следующие мои соображения:

- Адреса основных управляющих регистров PHY стандартизованы, драйвер MAC контроллера сам разберётся с инициализацией PHY

- Всё что необходимо будет добавить - это включение свича. Это можно сделать как через MII, так и через SPI.

- Причём использование SPI позволит контролировать коммутатор независимо от драйвера Ethernet в системе

- Для того чтобы отлаживать систему нужно грузиться через TFTP клиент u-boot"а, то есть когда свич не запущен. Перемычками настраивая PS0 PS1 можно на момент отладки сконфигурировать свич на EEPROM, не увидя на шине такового свич сконфигурируется по умолчанию и включится

Плате через считанные дни в производство, а тут такая дилемма :)

-

К процессору земля подводиться как можно ближе к соответсвующим ножкам, к памяти аналогично. Слой земли в большинстве случаев прерывается только еденичными переходными отверстиями сигналов и питания.

У меня в бумаге Г. Джонсон М.Грэхем Конструирование высокоскоростных цифровых устройств.

Про барьеры, стенки, возвратные токи, перекрёстные наводки я прочёл.

То что написано в книжке и то что воспринимаешь сам становяться одним и тем же когда появляется опыт.

Чтобы не плодить лишнего я обратился ко всем читающим ветку.

-

at91sam9g20 проблемы с sam-ba

в ARM

Опубликовано · Пожаловаться

После подачи питания в окне терминала появляется заветное RomBOOT, идёт реакция на команды, записи чтения, принимает файлы в внутреннюю sram.

Если запустить Sam-ba (2.8, 2.9) она какое то время блокируется, а потом занимет 100% времени одного из ядер ПК. (при этом потребление устройством увеличиется на 30%).

Она инициализирует pll именно на старте? может там аппаратные проблемы стоит искать?

По УСБ при подаче питания появляется "Неизвестное устройство".

Чип ревизии "B" и питание 1в на ядро подаю после 3.3 на VddIO

Задержка подачи идёт через конденцатор на функции soft start LDO