Vitaliy_ARM

-

Постов

508 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Vitaliy_ARM

-

-

А кто мешает XP2 грузить как обычную FPGA не трогая флешь? Она может и так и эдак работать.

Наверное никто :rolleyes:, просто цена плис той же фирмы, но без флешь, меньше. Кстати попытался запросить

LFXP2-17E-6QN208C в одной из наших фирм, сказали, что их в Россию не поставляют. Думаю, что это бред.

Надо будет в Гамме узнать.

Пока макет собирается на альтере.

-

Выбор действительно невелик, Altera в PQFP240, да Lattice в 208.

Опытный образец решил все таки сделать на альтере в 240 ног. Кое как залезла на плату.

Определился с архитектурой. У меня система постоена по принципу ARM7 + FPGA. Связь с ПК по Ethernet.

Планирую прошивку заливать каждый раз при запуске программы с пк, через процессор в FPGA.

Получается, что прошивку можно обновлять в программе, это хороший плюс. XP2 с флешь, мне пока не подходит.

После обкатки опытника, переползу на Lattice без флешь.

-

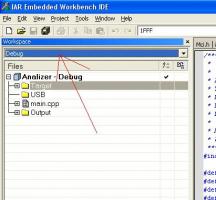

У них это называется Target. Да, можно. Project->Options->Compiler->Preprocessor->Predefined symbols для каждого Target вписать туда свой символ, например DEBUG, RELEASE. Дальше в тексте

Спасибо Сергей! Уже в который раз даете короткий и понятный ответ.

-

-

Так собственно говоря managed make ( т.е. сам пишет makefile ) и опции компилятора можно в среде (визуально) выставить.

Я не дождусь, когда же они разродятся и сделают отладку под эклипсом.

-

Я использую SDRAM для памяти программ. Внутреннюю EBR SRAM только для FIFO, кэша процессора (может еще куда), т.к. полагаю что для памяти программ внутреннего ОЗУ(EBR SRAM) не хватит. Откомпилил тестовую программку (130строк на Си) - заняло 7 KBytes, а в старших XP2 порядка 100 KBytes.

Да, получается, что связка CortexM3(100МГц)+Lattice эффективней, чем одит Lattice с Мико32. За исключением мудреных протоколов, например Gigabit ethernet, который в дешевые процессоры пока не встраивают.

-

Собираю проект на LFE2M20 (серия ECP2M) с процессором LatticeMico32. Проект занимает 63%. Шина Wishbone, до 20 устройств на ней (UARTs, DMA и т.д.). Процессор тактируется 60 MHz. Результаты тайминга после P&R:

Спасибо за информацию. Пока сильно не вникал в софтовые процессоры, всегода использовал обычные. Скажите, наличие внешней микросхемы ОЗУ обязательно? или можно использовать внутреннюю ОЗУ (и сколько)?

-

Наверное проще суппорт спросить... Или собрать самому и глянуть. Семейство довольно новое, а lattice у нас достаточно мало распространена, наверное, ввиду повышенной "религиозности" разработчиков. Я к тому, что очень сомневаюсь, что кто-то у нас пускал.

Семейство очень привлекательное, есть флешь, и защита прошивки. Только что-то их процессор медленно развивается. Попробую написать в поддержку.

-

XP2 точно. У него fMAX_IOE = 311 МГц для самого тормозного спидгрейда. Про ECP2 не в курсах.

Задам еще один глупый вопрос. Кто-нибудь использовал LatticeMico32 на этой платформе (XP2)?

Какая максимальная тактовая частота получается?

-

И когда ждать сиё чудо ??

Судя по всему, не раньше чем через 2 года :rolleyes:

-

Нет, так напрямую сделать нельзя.

Получается, что DMA с потром работает так же, как и у ST. Пора бы уже было и сделать. :maniac:

Очень помагает при изобретении на таких процессорах, например Camera Interface.

И еще кучу всего можно было бы сделать при помощи такой возможности.

На счет таймера, надо пробовать.

-

Не понял одного момента, можно ли запустить синхронизацию GPDMA от ноги PIO, например по нарастающему фронту DMA берет байт с порта и кладет в память?

-

-

-

код 4-х разных видов FIR выкладывал на форум, киньте в личку мыло вышлю доки и базовые коды CIC(System Verilog). NCO на этом форуме выкладывали на VHDL/Verilog, там работы минут на 5 %). Вышлю еще доки по NCO.

Спасибо!

mail бросил в ЛС.

-

это все что вам надо ? может я что то не понимаю, но CIC фильтр делается за пару минут, FIR минут за 5. И для этого нужно покупать дорогие тулзы типа SystemGenerator :unsure:

Поделитесь ссылками или доками пожалуйста, что такое FIR и с чем его едят знаю, про CIC не очень.

Коды этих фильтров на VHDL и Verilog с успехом умеет генерить Matlab (подробно пока еще не разбирался, чего он умеет, но что-то генерит).

Еще нужен NCO генератор, остальное не проблема.

Нет. Но вот в XP2 зато планирую использовать USB2.0 High Speed Device корку (без процессора в смысле проца общего назначения). Пока только собирал ее в целях того, чтобы понять, сколько места она съест.Неплохое семейство и цена давольно хорошая.

-

ЗЫ. И кстати, в вашей же таблице написано 13К, а вы говорите - вам надо 16К+-3К. А вдруг будет "+"?

Это я пока априорно прикидываю. Скорее всего будет в два раза меньше. Сейчас хочу взять плису пожирнее,

и сделать макет. Потом уже определюсь, какая точно нужна. Сейчас главное определить фирму. У альтеры что-то совсем плохо дела обстоят с LVDS.

XP2 точно. У него fMAX_IOE = 311 МГц для самого тормозного спидгрейда. Про ECP2 не в курсах.Отлично, надо посмотреть на их DSP библиотеку. Вы случаем не использовали процессор от них LatticeMico32?

-

Ха-ха. Я его попробовал один раз. После синтеза он мне сказал, что 80 мегагерц без вопросов. После PAR... Эта оценка упала до 34 МГц. После чего сразу пинка под зад. Синплифай же если говорит 54 МГЦ, то и после PAR 54 +-один-два, как правило +. (на том же проекте!)

Понятно. Значит не все потеряно :rolleyes:

Мне надо чтобы был обмен на ногах около 200МГц, лэтис такое позволит?

-

В даташите :) На спартан3 я вам ссылку дал. Смотрите раздел I/O Capabilities. Для тех мс, которые я указал - всего пользовательских ног - 97, диф пар - 46.

Если 1 макросел = 1лут+1триггер, то вам надо 2000 CLB (8 пар LUT+триггер на CLB). Тогда спартан3 вам уже не подходит (такой объем только в BGA). спартан3е - аналогично.

XC3S700A - видимо тоже не хватит (1472 CLB). Если только XC3S1400A. Но там опять же 256 ног.

В общем сейчас оцениваю спартан 3А по этой таблице:

Logic Cells для XC3S700A по нему 13K. Правда корпус BGA-й.

-

Приблизительно так. Для более точной информации загляните в

Посмотрю. Я так понимаю, предпочтение лучше отдать S3A?

Ну вот я работаю с LFXP и перехожу на LFXP2. Левер 7.2, синплифай 9.6.2 - проект забивает кристалл на 89% по слайсам, времянка довольно жесткая. Никаких проблем нет. Проект веду в синплифае. Не квартус, конечно, но в общем впечатления исключительно положительные. И выбор их ПЛИС у меня на равне с альтерой и ксилинксом, а где-то и впереди них.Главное - не использовать precision - а то и будет такое, что как чуть что, так не лезет, или по констрейнам мимо, или не собирает. Он, прецижн, слишком оптимистично оценки строит пре-раутовые.

Что касается левера - это не есть среда :) Это тулз для place/route. И он не умеет компилировать ни vhdl, ни verilog. Среда для лэтиса должен быть синплифай, и без вариантов.

Вот с прицижином мы и долбались :smile3009: . Это кашмар какой-то. Я в лэтисе не специалист, дайте пожалуйста ссылочку для ознакомления с синплифаем 9.6.2. И еще вопрос, как там обстоят дела с библиотеками для DSP, например реализации CIC, FIR фильтров у лэтиса есть?

-

LFXP2-17 есть в PQFP208 (28x28мм). И почему же в последнюю очередь-то связываться?? В некотором смысле эти серии "делают" всех. Например по защищенной флеши внутри и AES.

Программировали в нашей фирме MachXO LCMXO2280. Проект был большой. Кое как все в нее залезло.

Впечатления от среды ужасные. Плохо определяет ошибки, почему не может скомпилировать проект (это был Level 7.0, может сейчас все изменилось?).

Просто по сравнению с квартусом это ... Наблюдался пороговый эффект. После заполнения проектом больше 2/3 кристалла компилятор отказывался компилировать некоторые конструкции VHDL. Решалось это все танцами с бубном. Чего с квартусом и альтерами сроду не было. Было еще много чудес, всего уже не упомнишь. Конечно возможно с другими плис все совсем не так, но факты тянут на выбор плис этой фирмы в самую последнюю очередь.

-

Правда тут не все, но посмотрите...

http://altera.ru/cgi-bin/go?66

Удачи!

Спасибо, посмотрел. Жаль, что ЭФО не обновляла давно информацию,

даже CICLONE 3 нет в списке. С Lattice, конечно, хотелось бы связываться в последнюю очередь.

Вроде бы как Spartan-3 претендует на эту роль.

У Xilinx надо смотреть линейку Spartan3.http://www.xilinx.com/support/documentatio...heets/ds099.pdf

Наверное надо смотреть в сторону XC3S200TQ144,XC3S50TQ144.

К сожалению Макроселы не могу перевести в CLB :)

Насколько оно отличается по ценам - тоже к сожалению не скажу. Есть e-find.

Наверное XC3S700A больше подходит.

Появился еще вопрос, в чем радикальное отличие Spartan-3A и Spartan-3E?

В каком документе можно посмотреть количество LVDS ног у конкретной микросхемы?

-

Вибираю плисину для проекта.

Ориентировочно нужно:

- около (+/-3000) 16 000 макроячеек.

- 22 LVDS входа.

- Корпус не больше QFP-208 и не BGA.

- Как можно дешевле

Ориентируюсь только в Альтере и то слабовато.

Из всего подхдит циклон 3 EP3C16 в корпусе 240ног, но корпус большой.

Подскажите пожалуйста аналоги у Xilinx и Lattice, на что смотреть?

-

TFT advanced interface. 16 бит SDRAM

Что же там такого "advanced"? :)

Тут была дискуссия на тему разводки, необходимости резисторов и проч.

У нас разводка получилась "как получилась", все работает.

Та же история. Все работает, разводите, не бойтесь. На этих частотах проблем нет.

Winter и Polygons

в Altium Designer, DXP, Protel

Опубликовано · Пожаловаться

Развожу плату. На плате два полигона, TopPoly и BottomPoly.

Было два правила. На слое Bottоm полигон заливается сплошным. На слое Top все спролшным, кроме Pads,

Pads заливаются термальным подключением. С недавнего времени слой Top заливается сплошным вместе со

всеми дорожками, в общем получается квадрат Малевича :cranky: ,

Слой боттом заливается нормально. Что только не делал, даже снес все правила и создал одно на все полигоны,

все равно нижний слой заливается по правилам, а верхний - сплошным вместе с дорожками. Перезагруз альтиума не помогает.

Подскажите пожалуйста, в чем может быть дело?