adnega

Свой-

Постов

3 587 -

Зарегистрирован

-

Посещение

-

Победитель дней

3

Весь контент adnega

-

Application Jump ch32v003

adnega ответил Alexandr27 тема в RISC-V

Насколько я помню, WCH-Link, даже получив команду частичного взаимодействия в памятью, все равно стирает всю. Т.е. по USB, по протоколу приходит описание региона (смещение и размер), но он эти данные игнорирует. По-моему, ответ: никак невозможно. Однако, что-то могло поменяться. -

Application Jump ch32v003

adnega ответил Alexandr27 тема в RISC-V

WCH-Link не умеет стирать/дописывать частями. Всегда делает MassErase на любую просьбу. -

Application Jump ch32v003

adnega ответил Alexandr27 тема в RISC-V

А внутри HF есть возможность получить значения регистров mepc, mcause, mtval ? -

Application Jump ch32v003

adnega ответил Alexandr27 тема в RISC-V

По адресу 0x0 лежит не указатель на reset_handler, а инструкция j reset_handler - понимаете разницу? По адресу 0х4 нет ничего полезного. Не советую использовать адреса 0x800.. для адресации flash - попробуйте 0x000... -

Application Jump ch32v003

adnega ответил Alexandr27 тема в RISC-V

А где метка _vector_base ? Попробуйте так: la t0, _start ori t0, t0, 3 csrw mtvec, t0 -

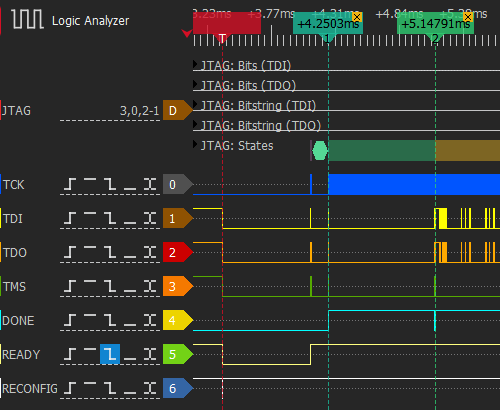

Сделал загрузку конфигурационной SRAM по JTAG. С учетом данной ветки все прошло гладко. Хочу сделать красиво, но для этого нужен сигнал DONE, который живет своей жизнью (или я чего-то не понимаю). После импульса сброса на RECONFIG, получаю READY (через 741 мкс). Затем делаю IR(0x11) [запрос DEVICE_ID], следом IR(0x15) и после этой команды DONE взводится в единицу. Почему? Ожидаю, что он взведется после перехода в User Mode (как на Figure 4-1 Configuration Flow Power). Я правильно понимаю "when configuring SRAM using JTAG circuit, it does not need to take DONE signal into account" в моем случае "не требуется учитывать" означает "не стоит учитывать"?

-

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

Конкретно мне он интересен: USB-HS со встроенной физикой на 480МГц. Ethernet 10/100/1000 со встроенной физикой на 10МГц. Восемь последовательных портов, SDIO, CAN (два), еще один USB, но -FS, контроллер внешней памяти FSMC, порт для камеры DVP, ADC-12бит 2 по 16 (с возможностью тача), DAC-12бит, операционники/компараторы OPA/CMP (четыре штуки), часы реального времени, три SPI, два I2C. А главное ценник от 250 руб/шт (почти в розницу) и наличие в РФ. Кста, частота 144 МГц (но есть особенности). Оперативки можно накрутить до 128КБ за счет флеши (которая WS0). По плотности кода и эффективности исполнения соглашусь - до Cortex-M4 не дотягивает, но я на последние и не гуляю. FPU одинарной точности имеется. -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

Дело хозяйское, но рекомендую про RISC-V не забывать) Есть отладка, в два раза дешевле, по некоторым пунктам уделывает "нормальный" МК) https://aliexpress.ru/item/1005006650480128.html?sku_id=12000037925938796&spm=a2g2w.productlist.search_results.7.62aa778fnseC10 Если принципиально Cortex-M, то смотреть AT32F, GD32F что-то из 4хх-линейки. -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

Это очень хороший результат. Я бы разделил понятия: "точность-погрешность-и т.п." Тут все ок, без предфильтров будет 1 такт таймера. И "пропуски-дребезг-загнулись". Нужно до ядра доводить только ту информацию, которая нужна для принятия решений. Т.е. если можно аппаратно выкинуть часть импульсов - это нужно делать. У вас настроен DMA на два переноса - в будущем можете просто увеличить размер буфера или вообще перейти на кольцо. Если передавать ядру всю информацию об импульсах, то оно загнется раньше TIM/DMA/ISR. > Применить смогу, например, при измерении частоты Частоту можно двумя способами измерять: 1) измерив период между соседними импульсами. 2) измерив количество импульсов за единицу времени. В зависимости от требований выбирается тот или иной способ. > Анти-шим это обратное извелечение информации из ШИМ, декодирование что-ли? Да. Очень во многих областях/протоколах информация передается длительностью импульса/паузы. > Правильные МК посмотрел. Купить в розницу незадорого, и собрать минимальный набор для отладки не получится. Не знаю что в них правильного? В наличии нет, ценник конский, решение получится не универсальное, т.к. будет привязано к конкретному МК. Сразу поставить ПЛИС, если программист не способен решить задачу без красивостей/правильностей в железе. > Для того, чтобы сделать вывод о возможном пропуске Вариантов много. Я часто один из свободных каналов захвата/сравнения использую для аппаратных таймаутов. > Для меня интересным было время, которое тратится на дма, на вход в прерывание, на синхронизацию, время сохранности результата в регистре. Это правильные интересы. У вас ядро популярное. Советую книги Джозефа Ю - зачитаться. -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

В этом вы ошибаетесь сильно: у меня все разрабатываемые контроллеры нафаршированы максимально) Под задачу я выбираю МК из типовых (что уже серийно используем, чтоб не раздувать номенклатуру), затем свободные ресурсы задействую для добавления функционала в перспективе. Я максимально использую аппаратные возможности МК. "Хоть поллингом флагов" это не призыв к действию, а иллюстрация простоты задачи. Для захвата ШИМ я использую два варианта: 1) с обработкой в реальном времени каждого импульса в прерывании; 2) с постобработкой порции или всего пакета импульсов в связке TIM+DMA. ТС не поставил никакой практической задачи, поэтому конкретно ответить сложно, но это точно не "использовать нормальный МК". Когда мы подменяем принцип выбора подходящего под задачу камня, нытьем танцора, которому в "обычных" МК все жмет. Не хочу переходить на личности, но мимо заявления о существовании неких "нормальных" МК пройти не смог. Итого, ТСу нужно зафиксировать задачу. Если это анти-ШИМ чего-то нешустрого, то советую освоить TIM+ISR. Для более шустрого, но не требовательного с реалтайму - TIM+DMA. Это закроет 99% типовых потребностей. Будут вопросы - поможем. Если задачу экстремалить, т.е. повышать частоту до предела, то, разумеется, в этот предел упрешься, а там уже принципиально иные способы решения могут возникнуть. Вместо этого рекомендую освоить TIM_master+TIM_slave - добавит в копилку решений еще 0.99% -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

>Может не будем валить с больной головы на здоровую? Речь шла о фиксации длительности одиночных импульсов. С одиночными импульсами вообще проблем никаких нет - хоть поллингом флагов CCR таймера. Речь шла о захвате в пределе - в терминах ТС "с минимальной задержкой". Я понял, что речь идет о задержке между соседними импульсами. >отсутствие информации, что такая потеря произошла. И что делать с информацией, что потеря произошла? Какой практический смысл? > была короткая иголка (в несколько тактов) В таймере перед блоком захвата есть аппаратный фильтр - для борьбы с такими иголками) > Поэтому при наличии всякого рода дребезгов, анализ посредством DMA на STM32 очень сложен. Я борьбу с дребезгом поручаю аппаратному фильтру. Иначе "дребезги" разобьют в дребезги любую систему, борющуюся с ними программно. Разве нет?)) Системы, типа, "я зафиксировала дребезг на входе поэтому работать дальше не буду" я рассматривать не готов) > Тогда расскажите - как будете действовать в случае... Вообще проблем не вижу. Недавно сдал систему захвата 12 каналов датчиков детонации с привязкой к углу возникновения с точностью 0.025 градуса. Помехи от частотника прут и по каналам захвата и от энкодера)) Есть и аппаратная борьба на входе МК (причем лайтовая, чтоб импульс не сдвинуть и не наврать с углом), и программная низкоуровневая, и программная высокоуровневая. Забавно, вообще все построил на EXTI-прерываниях. А точность получилась - мама не горюй - видно как вал скручивается в зависимости от нагрузки и оборотов)) Кста, есть программная компенсация задержки распространения сигнала во входных аналоговых цепях. ШИМ-декодировать приходилось в драйвере приемника от ИК-пультов. Или в вызывной панели VIZIT. Или в работе с 1-wire устройствами. Вообще без проблем. Итого: если не придумывать себе проблему, чтоб потом ее героически решить, то и проблемы не будет. > ЗЫ: Или всё-таки в таймерах STM32 есть какой-то способ зарегистрировать факт потери события? Кто знает? Я же сказал: задача фиксировать факт потери события в большинстве случаев не стоит. Кто знает систему, где обработка потерь импульсов играет рояля? -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

Могут предложить такую задачку (если ТС не против): 1) Есть адресные светодиодные ленты (типа WS2811) - 4 шт. 2) Есть источник данных для этой светодиодной ленты. 3) Нужно сделать контроллер с одним входом (WS2811) и 4 выходами (WS2811). 4) На каждом выходе нужно индивидуально задать сколько светодиодов будет пропущено из потока. Проще: нужно входные импульсы пропустить на выход, но первые 24*Ni (i от 1 до 4, Ni > 0) заменить на лог "0". Будем считать, что импульсы со скважностью 2 и частотой 800кГц. Я сделал такое на STM32F042 (аналог F030, на F030 тоже заработает). Контроллер позволяет данные для одной длинной светодиодной ленты поделить на сегменты с индивидуальным смещением - резко удобнее становится подключение. Кста, одноканальный вариант вообще на Тини13 делал) -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

Идут импульсы/паузы в тактах: 1/1-1/2-1/1-1/1 и т.д. непрерывно. Сколько тактов стоит CPU вытащить эти данные из FIFO (со всеми флагами переполнения и т.п.)? Очевидно же, CPU не сможет обработать такой непрерывный поток. Очевидно же, DMA тоже может обеспечить поток, который CPU не сможет обработать. Чушь - ок. Отсутствие потери событий гарантируется архитектурой системы. Кто-то проектирует систему, где допускается потеря событий - я так не поступаю и другим не советую. Предметнее проще: приведите пример задачи, где без "нормального" МК не обойтись. Я довольно сильно использую таймеры - пока все задачки решаются STM-совместимой таймерной периферий большинства популярных МК. -

Вопрос по захвату таймера stm32f030

adnega ответил ozforester тема в STM

Обрисуйте конкретную задачу - будет проще предложить решение. Регистры CCR - это и есть FIFO на один элемент, далее - DMA (с характерным темпом не чаще 12 тактов CPU). Не знаю зачем "нормальным" МК какие-то FIFO: ну наловишь импульсы "хоть в 1 такт" - дальше что? кто их будет способен обработать? -

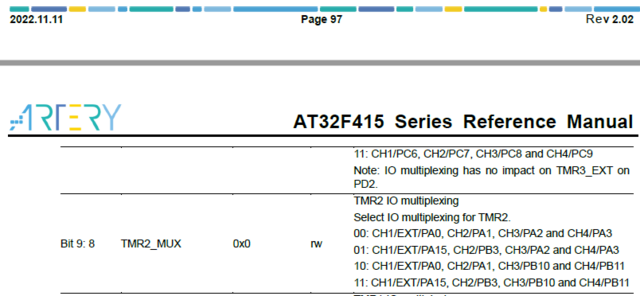

А разве TMR2 должен ремапиться на PB8/9 ? "Non-timer peripherals has priority over timer peripherals". Нужно проверить, что на этих пинах нет никакой нетаймерной периферии. Кста, в чем отличия _MUX и _GMUX регистров?

-

-

li t0, 0x1f csrw 0xbc0, t0 /* Enable nested and hardware stack */ li t0, 0x0b csrw 0x804, t0 /* Enable floating point and interrupt =0x6088 / =0x7888 */ li t0, 0x7888 csrs mstatus, t0 la t0, _vector_base ori t0, t0, 3 csrw mtvec, t0 /* la t0, main csrw mepc, t0 mret */ j main Можно поправить исходный примерно так.

-

В своем загрузчике startup от производителя не заработает, т.к. там делается переход в U-режим. И уже попытка записи csr в startup приложения вызовет сбой.

-

Чему равен Page_Address ? #define FLASH_BANK1_END_ADDRESS ((uint32_t)0x807FFFF) - не много для 16кБ флешки?

-

2000014a: jalr t0,160(zero) # 0x0 <_start> А это что? Что лежит по адресу 0xA0 ?

-

Почитал внимательно . ТС вызывает функции из функций )) Да, функции находятся в ОЗУ, но они могут использовать флешовые __riscv_save_0/__riscv_restore_0 Выглядит так: в начале функции 200000e0 <test_ram>: { 200000e0: 0c0002e7 jalr t0,192(zero) // 192=0xC0: <__riscv_save_0> 200000e4: 03000793 li a5,48 while(!(USART1->STATR & (1 << USART_STATR_TC))); ... и в конце 20000138: dfe5 beqz a5,20000130 <test_ram+0x50> test_foo(); 2000013a: 37b9 jal 20000088 <test_foo> - вызов вложенной ram-функции } 2000013c: 0ca00067 jr 202(zero) // 202=0xCA: <__riscv_restore_0> 000000c0 <__riscv_save_0>: c0: 1151 addi sp,sp,-12 c2: c026 sw s1,0(sp) c4: c222 sw s0,4(sp) c6: c406 sw ra,8(sp) c8: 8282 jr t0 000000ca <__riscv_restore_0>: ca: 4482 lw s1,0(sp) cc: 4412 lw s0,4(sp) ce: 40a2 lw ra,8(sp) d0: 0131 addi sp,sp,12 d2: 8082 ret

-

посмотрел v003 сильно отличается: CSR 0xBC0 - отсутствует; U режима нет совсем (mstatus.MPP=0b11, т.е. всегда в режиме M).

-

Не ваш случай, но на старших камушках еще и с частотой непонятки: ядро может 144МГц, а флеш то ли 120, то ли 60 МГц максимум. Типа нужно замедлятся при работе с флешью. Причем, read тоже за работу считается - не понятно(