SergeySoG

Свой-

Постов

162 -

Зарегистрирован

-

Посещение

Весь контент SergeySoG

-

Да, я полигон не перезалил, сейчас сплошной до антипадов

-

Спасибо огромное! Очень помогли прояснить пару мутных для меня пока моментов. Эти косяки я исправил

-

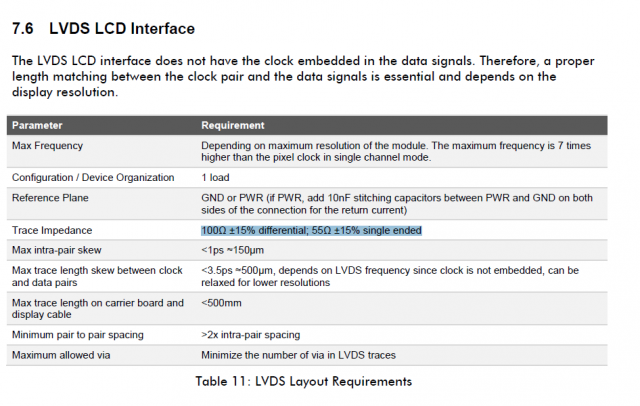

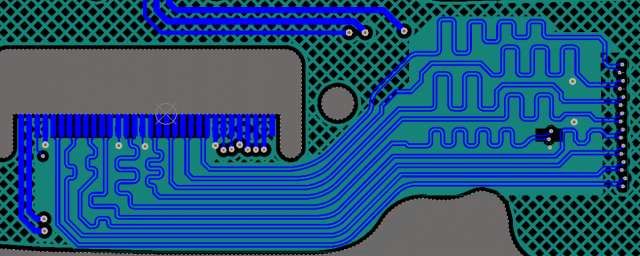

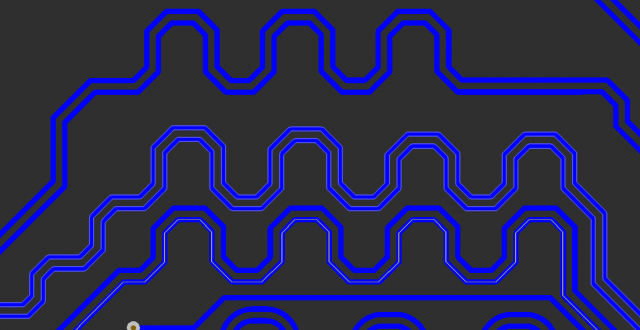

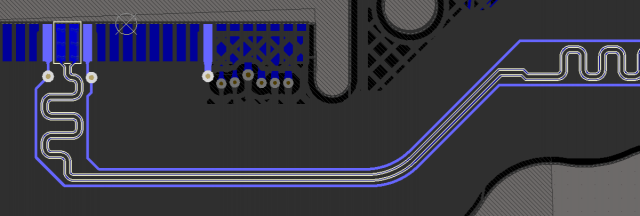

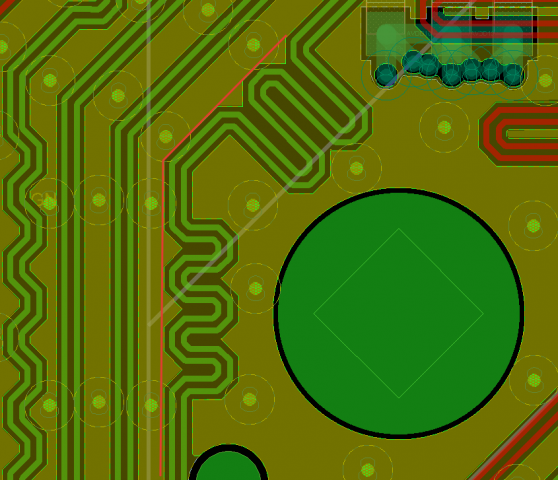

Можно поподробнее из-за чего надо всё переделывать заново? Я ориентировался вот на эти рекомендации для LVDS У меня трассы 0,1, зазор в паре 0,12, расстояние до референса 63мкм. Зазор между парами 0,25. Все пары выравнены на одном слое. Даже еслди в расстояниях от референса считать то зазор большой. Полигон сеткой потому что плата гибкая из полиимида, под дифпарами залита сплошная земля, сетка только в остальной области где нет хайспидов, переходные в дифпарах microvia прямо на площадки коннекторов,под коннекторами и via антипады сделаны. Земляные трассы уберу, специально про них спросил. То есть получается что спейсинги везде нормальные, параметры пары посчитаны, антипады есть, земдя нигде не рвётся - что не так то? Полигон уже перезалил, скрин старый, под парами сетки нет

-

Работает почти всегда, спасибо. Только если места не очень много между проводниками надо правильно начальные параметры меандра подбирать, а то совсем отказывается меандр размещать

-

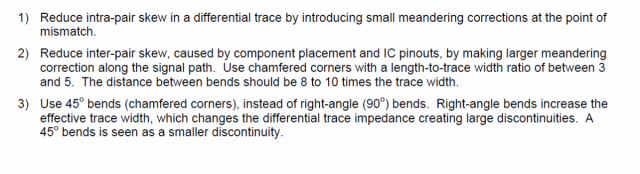

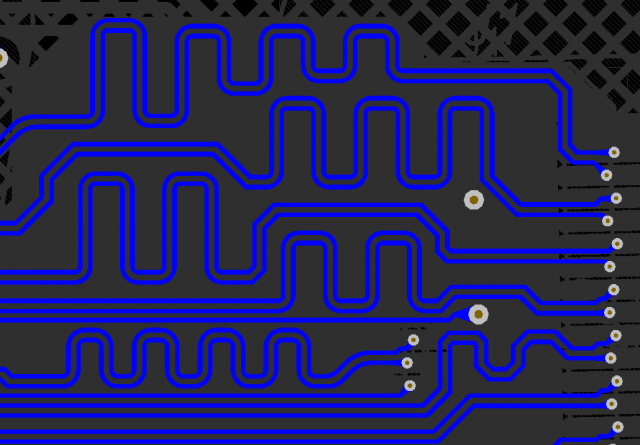

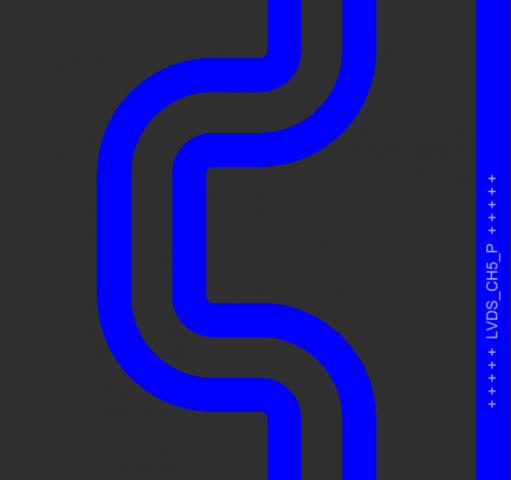

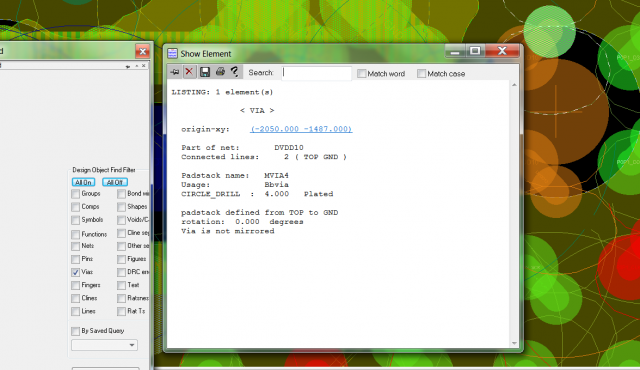

Всем спасибо, пользуюсь сноровкой. И тогда уж по теме ещё спрошу что бы удостовериться, вот рекомендации от TI для трассировки Display Port. Интересен пункт 3, гнуть под 45 градусов потому что так меньше изменяется ширина проводника. Eсли мы используем меандры не под 45 градусов, а со скруглением углов, на скруглениях ширина проводника не меняется и изменений импеданса не должно быть, в таком случае допустима ли такая форма меандров для LVDS По моему разумению вроде не должно быть проблем. Если допустима, какой минимальный радиус можно использовать для поворота трассы Так нормально или уже плохо? Если плохо почему? Или делать так по любому правильнее? В референсах видел и так и так, в одном референсе всё выравнено как на картинке в первом посте, Intel в своём референсе всё ровняет скруглениями, но у них радиус большой довольно, не похож на скруглённый прямоугольник. И в начале сказали что земля рядом плохо влияет на импеданс пары. У меня на коннекторах, клок LVDS с обоих сторон от данных отделён землёй как в референсах, я от коннектора до коннектора протянул эти земли вдоль пары клока толщиной 0,1мм с зазором от пары 0,1мм и на концах через Via посадил эти проводники на план земли референсной. Правильно это или убрать их пока плату в производство не запустили? Ну тупой, чего ж поделать то.... А если честно то, не работает. На работе аллегро нет, только вьювер стоит. По правой кнопке мыши вообще ничего не работает, если ткнуть Show Element, то via выбирается и открывается такое окно, где параметр падстека MVIA4 посмотреть? А на референсе от Intela вообще via не выбираются только корпус микросхемы под которой они находятя

-

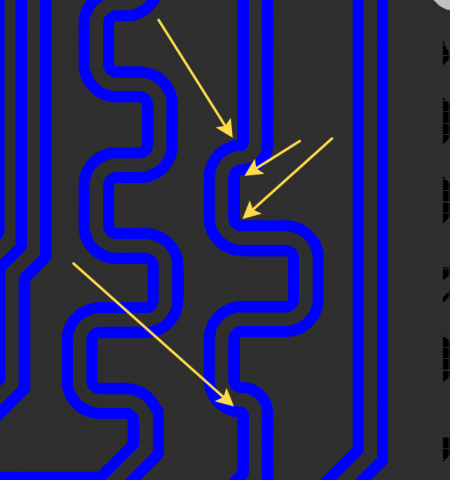

К сожалению не всё от меня зависит, пока Альтиум, пока исправляю ручками, он у нас давно, ещё до хайспидов куплен и меняеть его никто не собирается, сам давно в сторону аллегро смотрю хоть и стоит он конских денег, даже к ребятам в PCB soft ездил посмотреть, всё круто , но ценник не для маленьких контор. Но это уже лирическое отступление. По целостности сигналов понимание что чего то на подобии Sigrity нет то же есть. Да. меандры для LVDS с последней картинки поправили на 45 градусов как гайды советуют. Резюмируя по теме. Автоматом альтиум делать не заставить, руками наше всё? А интерфейс у аллегро просто ад на первый взгляд, я с учебником сидя за 30 минут не смог свойство via посмотреть в референсе

-

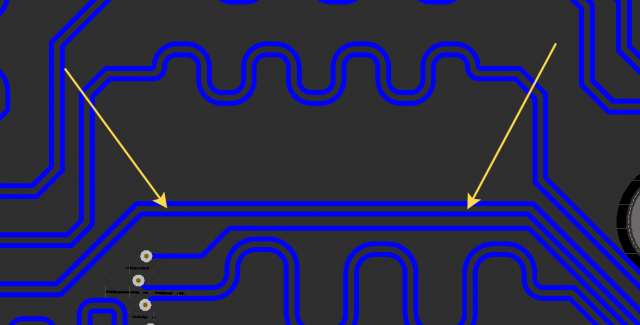

На первой картинке кусок референса от производителя микросхемы, действительно всё залито, но тут за что купил за то и продаю, я этот кусок для примера меандров привёл. Про последнюю картинку я понимаю, потому её и привёл. Выравниваешь в Альтиуме, думаешь, программа за 500 тысяч за рабочее место, ну должна наверное нормально меандры делать, тут такое, а потом главное не просмотреть где у тебя такие углы получились

-

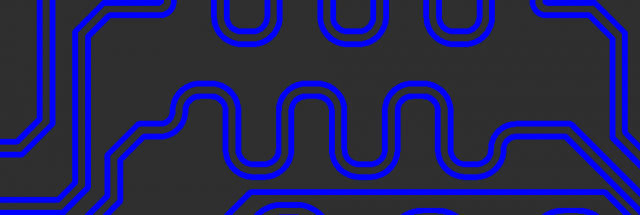

Добрый день, подскажите кто знает. Ровняю диффпары в Альтиуме 17.1. Может ли альтиум ровнять пары так что бы сегменты змейки были только на одну сторону пары, то есть вот так как в Allegro. Я когда в альтиуме провожу одну пару близко к другой и оставляю справа например достаточно места для выравнивания, но он не в какую не хочет добавлять меандры или дуги, как бы я с параметрами не игрался. Добавляет один сегмент и потом встаёт, второй не может добавить потому что слева нет места. Например вот здесь он отказывается ровнять пару с сегментами только вверх, делает один сегмент и всё, дальше не идёт. Получается выровнять только вот так Можно как то с таким поведением побороться, хорошо место есть, а если бы его не было, что делать. Размножать в ручную один сегмент как делают несколько моих знакомых как то не вариант в наше время. И ещё один вопрос тут же, когда альтиум ровняет пару он забивает на рекомендации которые все производители для изгибов хайспидов дают, то есть не выдерживает параметров изгибов сегментов автоматически, легко может сделать вот так Можно с этим как нибудь побороться, правило может какое прописать, или по старинке в ручную всё за ним проверять и править?

-

Вопрос по гибким печатным платам и Stiffener'am

SergeySoG опубликовал тема в Altium Designer, DXP, Protel

Всем добрый день. Подскаджите кто знает можно ли как то в Альтиум дизайнере добавить стиффенеры (укрепляющие пластинки, ужесточители из RF-4 или полиимида) стандартными средствами. Сейчас добавляем их как 3D тела в проект и потом на выходной документации отдельно рисуем где какой и какого размера поставить. Ничего стандартного не нашёл для Альтиума. Подскажите кто как делает? Пробовал в режиме редактирования контура платы создавать несколько стеков для разных областей платы, как для гибко-жёстких плат, но ничего не вышло - у меня stiffener'ы сложной формы, а как сделать split line отличной от прямоугольника формы и можно ли вообще я так и не разобрался, похоже что нельзя. Буду рад если поделитесь опытом. -

Я для уточнения декодер чего дал все свои контактные данные, проект уже заканчиваем.

-

На проект требуется инженер FPGA с опытом работы с FPGA Xilinx. Среда Vivado Требуется переработать декодер сигнала на FPGA Artix-7 100T от Xilinx плюс добавить коммуникацию по UART, декодер первой версии есть в исходниках. Требования: - Код без использования IP ядер от Xilinx только RTL - Язык VHDL - Верификация проекта на отладочной плате (предостаавляется). - Ориетнтировочный срок проекта 4 недели. - Старт в ближайшие дни Всех заинтересовавшихся прошу писать за подробностями на почту [email protected] или skype: s.sogurov

-

Да нет, у нас просто несколько проектов подряд на LPC4370 идёт и с первого проекта остались LPC LINK2, ими и пользуемся. Уже заказали обычный J-link. С Segger О-Link вообще проблем нет, воткнули разъём и понеслась. Так что до серийного производства не дошло, LPC-Link2 тупо разработческих будней не выдержал. Если у кого то стоит вопрос что брать для LPC43xx - сразу J-Link. Пробовали, писал где то уже давно в теме, и много чего ещё пробовали. Но электроника наука о контактах, и против поганенького шлейфа на разъёмах даже шаманство не помогает. Просто сейчас проблема известна и решилась за 2 минуты, а принципиально как уже написал решается использованием нормального J-Link

-

И ещё новости с полей. Слетел с катушек ещё один LPC-LINK2. Перестал определять платы которые до этого спокойно шил. Изнашивается шлейф и разъёмы, как результат ухудшаются соединения и Link перестаёт определять таргет. Опять помогла припайка проводами на прямую. Не определяются платы с контроллером LPC4370FET100

-

Разводка ПП для SRAM

SergeySoG ответил mihlit1 тема в Работаем с трассировкой

Нет, не так. Не надо запускать автотрассировку, после того как схему нарисовали, открываете апноты от производителя микросхем SRAM например вот этот от Cypress http://www.cypress.com/file/38651/download. Читаете внимательно, и начинаете разводить придерживаясь основных правил хорошей трасировки. 100 МГц трудно запороть, сам в этом убедился, но это при том что вы будете соблюдать основные правила разводки, а не трассировщик включите. Обратите внимание на Layout guide. Как правильно располагать блокирующие конденсаторы по питанию, как разводить питание и земплю, как линии данных, что с клоками делать. И будет вам счастье. -

Извиняюсь за долгое отсутствие. Нашёл минутку и хочу рассказать о развязке в истории. Может кому то поможет. перепаяли процессор на плате, а jtag и SWD так и ведут себя более чем странно. От безысходности взял и припаял я этот несчастный LPC LINK2 фирменный к плате проводами напрямую. И о чудо все платы стали определяться и дебажиться нормально. В это время второй LPC LINK2 со второй платой соединённые шлейфом из комплекта не работает. С процессором в 100 ногом корпусе работает, с процессором в 256 ногом корпусе не работает. Оригинальный Segger Jlink плату взял сразу и без вопросов . При первом же подключении нормальный дебаг. Видимо очень тонкие проводочки в шлейфе с шагом 0,63мм и 2 разъёма штыревых делали своё дело и программатор не мог вытянуть 256 ногий процессор. так что не всё то что фирменное и от производителя одинаково полезно. В техподдержке сказали что это не правильно и в плате косяк раз с проводами припаянными работает, а так нет ;) . Очень жаль кучу потраченного времени

-

Купили новые камни, будем менять, по результатам отпишусь. Ну и кажется развязка близится. Надеюсь кому то это сможет помочь. Инженер из техподдержки NXP прислал правильную последовательность действий для проверки коннекта с ядрами и отладки. Файл прилагаю Ответ поддержки Now, please follow my step to do it again: 1. Use the JLINK commander to check your JTAG connection at first. Just like my previous email, don't use the IDE, juse the JLINK command check the JTAG connections at first. After it can find the core, it means the hardware can work, then you can use the IDE to debug with the JTAG or SWD. 2. Open your MCUXpresso IDE Check your picture which you give me before, in the debug configuration window, delete all the item under C/C++(nxp semiconductors) MCU Application. Then apply, go back to your code window, build your code,in Quickstart panel, use the debug directly, it will find the JLINK automatically, but at first, you need to make sure your JLINK driver have been stalled. The MCUXpresso IDE will find the JLINK automatically. Please check my attached .doc details. Да и ещё, шлейф от LPC LINK оказывается не очень качественным, он прозванивается как исправный, но заработал стабильно только когда я таргет с дебагером проводами на пайке соединил. Отладка с использованием LPC LINK 2 в режиме RedLink так и не работает, коннекта нет Чуть позже будут боевые тесты с программистом. LPC4370_JLINK_1.pdf

-

JLINK Commander ядра видит без проблем.

-

Выкладываю кусок схемы с подключением. На ней перепутаны BOOT' ы, но это на плате поправлено. И с флэшки и с USB грузится. JTAG сейчас включен так. TCK - подтяжка с земли убрана - линия подвешена через 10k на +3,3В. TDO - подтянута через 10k на +3,3В _ontroller_V2___Schematics_Print1.pdf

-

Неа, там только про ISP, но вроде к делу не относится

-

В NXP сказали взять JLINK и поработать с ним, попробую сегодня то что они сказали

-

Я уже писал несколькими постами выше, схема подключения JTAG сейчаc как у haker_fox. До этого была как в LPC LINK. Это не первый проект на LPC4370& у нас они просто в корпусах BGA100 стояли и работают и шьются отлаживаются без проблем. Проблема с корпусами BGA256, делали по разному, получилось только через аттач подключится.

-

Печаль в том что в этом режиме нельзя залить прошивку и каждое исправление перед отладкой придется заливать по usb

-

Вот такая петрушка получается. Если параметр Attach only= true то коннект по JTAG есть. если параметр Attach only= false то ошибка и читает ID ядер по нулям. В чём может быть проблемма?

-

Ещё момент. Когда первый раз платы запустили на выводах JTAG и CS внешней SPIFI флэшки был уровень напряжения 3В. ядра определялись но не коннектились. Сейчас ядра не определяются, но на всех выводах 3,3В как должно быть. а до будет со второй платой сравнить, на которой ещё ядра определяются

-

Ещё сейчас пришла информация, мы отдавали плату со стоногим корпусом на перепайку процессора. После этого отвалился JTAG точно так же на стоногом проце. Вопрос может JTAG на этих камнях умирать от перегрева или статики? Можно ли как то через LPCScrypt проверить исправность JTAG? Тапками не кидайтесь. я не программист МК практически не разу. Текущие платы запаивались монтажником вручную, мог термопрофиль не выдержать. Но я ещё не встречал, что бы JTAG сдох, а всё остальное жило