gab

-

Постов

377 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные gab

-

-

Параллельный выход обязателен.

Около 1 MSPS. Можно больше, но нежелательно. Полоса сигнала - 4 КГц.

Требуется две штуки для лабораторного образца. Или параллельный, двухканальный.

Конечное устройство полетит к Марсу, поэтому желательно хотя-бы indastrial.

-

-

Посмотрите здесь http://www.synplicity.com/corporate/global...stributors.html

Попробуем связаться. Интересно, сколько будет это стоить?..

-

Где в России можно официально купить Synplify DSP?

-

Stas задал тот же вопрос (о причине исключения и откуда вылетел), что и тех.поддержка Элвиса.

Если все-таки ответите на него, то нам будет проще Вам помочь.

Если нет, то приезжайте с платой к нам.

Мы Вас уже давно приглашали :)

Запустили! Работает! Была ошибка в сигналах А10 и А10_.

НО! Возникает проблема при загрузке линукса. Без рамдиска всё нормально вылетает на попытке подмонтировать rootfs. А если указать в конфиге кернеля рамдиск, то подвисает (лог приложен). Судя по mdb крутится он в функции inflate, т.е. распаковывает рамдиск. Ждали часа 2. Висит... Меняли тактовую частоту - без результатов. Опорный тактовый генератор - 10 МГц.

Забыл сказать: Тоже самое и на отладочной плате. Т.е. ошибка не в нашем железе.

-

Мы купили у Елкора набор разработчика для -24-го процессора. Сейчас заказали свои инструментальные платы на нём. Пока процессором довольны. В частности, именно из-за приёмки и производительности :).

Для него есть линукс (2.6.х), jtag-адаптер стоит меньше $100 (он интегрирован в development-kit, так что умный может съэкономить :))

Хорошо стыкуется с NeuroMatrix, что тоже большой плюс для нас.

Есть большие надежды на чип Multiflex 2, что приведёт к сильному сокращению ПЛИСовой части наших разработок.

PS: полная документация на процессор имеется. Если есть желающие, то можно выложить.

Через пол-года отвечаю сам себе. Сроки горят. Разработтаная плата с этим процом - не работает. В документации явные ошибки. Техподдержка - невменяема, говорит "это вы такие идиоты". JTAG-адаптер - верх идиотизма! В наше время LPT - анахронизм. Из 10 компов он заработал только на принесённом из дома нотбуке. Одно большое разочарование.

Если тут есть кто-то из разработчиков этого проца, вопрос: SDRAM работает стабильно. Программа нормально исполняется из внутренней SRAM. При попытке запустить её из SDRAM она через некоторое время вылетает на адрес 0xbfc...

Содержимое SDRAM при этом не изменяется!!!!

-

Мы используем Фдискр=16*8МГц, ПЧ=16*5МГц.

Полоса +-16МГц. Фазовая ошибка при отстройке +-10МГц < 5 градусов.

-

Запустил и не нашёл! :07: Даже пример с микроблейзом теперь с PLB.

Тема закрыта. Нашёл. :twak: Но заметен постепенный переход на PLB.

-

Меня, как разработчика, напрягает отсутствие штатной среды программирования под linux. Блин, ну нет у меня вокруге виндов! А под вайном он (MC Studio) глючит.

PS: Делаю RedBoot под 24-й. Такое кому-нибудь нужно?

-

На pcb это распространяется (иерархия)? меня интересует, если в схеме некоторое кол-во одинаковых комплектов, трассируется только один из них (остальные автоматически дублируются) или каждый нужно трассировать?

Напрямую - нет. Но есть возможность оттрасировать один комплект сделать его элементом. Дальше небольшое шаманство и вуаля! :).

Последовательность проста: делаем лист схематика с этой многократноиспользуемой частью. Трассируем. И делаем полученное элементом в PCB. В gede делаем для него символ. Собственно, всё делается как в любом каде.

Остаётся проблема в refdes блоков. Но для этого можно написать скрипт переименования, благо форматы всех файлов открытые и в geda и в pcb есть возможность писать скрипты (есть уже готовые, например BOM).

Если возникла необходимость редактирования реиспользуемого блока - всё просто: редактируем схему, её "печатку" и апдейтим основную печатку.

Я такой (с небольшой модификацией) метод всегда применяю. Например, делаешь что-то для себя и хочется подешевле (т.е. двуслойка), выбирfешь законченные функциональные модули, выделяешь в подблок, делаешь миниплату для него, по краям ставишь выводы (получается, что-то вроде модулей POL от Traco). В результате имеешь ещё 2 этажа для монтажа.

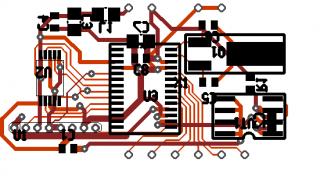

Приведённый мною выше пример разводки именно такой модуль. Магнитный компас + АЦП.

Кстати, в примерах у pcb есть 2 реиспользуемых модуля :). MSPxxx + jtag header и 68xxx CPU + FPU.

-

Особо еще с кикадом не разбирался, но похоже что нет. А в gEDA есть поддержка иерархии?

да. +поддержка spice.

-

А Вы kicad смотрели?

Пока нет. А geda мне понравилась за похожесть на Mentor Design View и возможность конвертации символов оттуда (у меня их много было).

А кикад умеет делать иерархические схемы?

-

Сравнил программы PCB (http://pcb.sourceforge.net, рекомендуемый для применения совместно с gEDA), kicad и freePCB в плане ручной трассировки печатной платы. Пришел к выводу, что использовать gEDA-pcb и freePCB для ручной трассировки вряд ли удастся. В freePCB похоже таких средств нет вообще, а в gEDA-pcb их явно не хватает.

Более или менее понравился kicad в этом плане. думаю попробовать развести пробную печ.плату как время найду.

А мне почему-то понравилась связка geda+pcb. Прикладываю примерчик.

-

ОС какая? Было такое на линуксе. Проблема была в переменных среды.

-

Можно-ли как-нибудь заставить ISE Simulator при поведенческом моделировании не ставить значение XXX для сигналов которые не были инициализированы?

Моделируется приемник с ФАПЧ. Перед ФАПЧем стоит туча всяких фильтров и дециматоров - присвоить всем значения нереально, а фильтры первые такты своей работы выплевывают мусор. Этот мусор попадает в ФАПЧ и зацикливается там.

На PP&R моделировании - все нормально, так как сигналы принимают конкретные значения. Но больно уж долго ждать каждый раз...

Как можно выйти из этой ситуации?

При объявлении используйре присвоение. Т.е., например:

wire aaa = 0;

reg ccc = 32'hffff_ffff;

-

Ещё, ИМХО, надо заменить '=' на '<='.

-

Если вы в Москве, то можно обратиться в "Модуль" (www.module.ru). Относительно недорого, и есть ренген-контроль.

-

В ALTlinux всё нормально с Xilinx ISE (c 7-й по 9-ю) и XPS.

Для x86_64 требуются некоторые телодвижения с XPS, но вообще, всё работает.

Modelsim (64 bit) тоже работает.

Одна большая проблема - драйвера JTAG-кабеля. Но при помощи IDA это скоро решится (штатные вылетают...).

-

Да устройство первый раз поставило прерывание, драйвер увидел, прочитал доп. регистр, понял что свое прерыванием сбросил его. ВСЕ. но если опять повторить такое то прерывание выставиться и будет стоять до тех пор пока я не пошевелю мышкой(((.... при следующем разе опять все норм пройдет(без шевеления мышки)... след. раз опять будет висеть до мышиного шевеления(или нажатия на клаву)

(К сожалению не я пишу программу) вызывается обработчик прерывания... читатет регистр, понимает что его прерывание, сбрасывает его... на след раз что бы прокатило... нужно пошевелить мышкой... а еще через раз опять все норм...

Xilinx является мостом шина ввода\вывода to PCI )

Получается так. 1 прерывание проходит, 2 не проходит, 3 проходит 4 не проходит и.т.п. но если сделать вот так

1-е прерывание проходит,(пошевелил мышкой) 2-е проходит, 3-е проходит, пошевелил мышкой, 4-е проходит

Скорее всего проблемы с буферизируемостью чтения/записи регистров устройства. Под линуксом лечаться rmb(). wmb() в обработчике прерывания (принудительный сброс кэша в область памяти). Под виндами ищите аналог сами.

Ну и главный вопрос: как написан обработчик прерывания? Поддерживает-ли shared-прерывания?

-

gEDA - отстой ИМХО EAGLE рулит Ограничение платы в 100мм х 100мм (Для Фрии врсии) не считаю существенным - при нынешней степени интеграции туда что хош запхнуть можно

Да и EAGLE стандартом становится - многие производители апноуты в нем дают

Еще можно платку из него в 3D в POV-ray посмотреть.

Библиотека обширнейшая по сравнению с отсальными ФРИ Кадами

gEDA может и отстой, но свободна. Eagle я проклял за его доморощенные антипиратские методы. Нах такую программу! (Мы деньги платили!)

А по поводу библиотек: ребят, не жмотитесь ГОСТовские символы выкладовать!

А то, прям, нашлись, кастраты в гареме... Потенциала много, а кинетики - нуль.

PS: В gEDA нет программы разводки ПП. Это делается отдельной программой. pcb.

PPS: В формат POV-Ray можно и из Mentor Graphics Expedition конвертить... Я-же это не рекламирую этот путь разработки ПП...

-

Спасибо огромное.

Ну и код. Там сам черт ногу сломит. Неужели нельзя описать все включения библиотечных компонентов средствами языка? Пусть даже ориентируясь только на синтезируемость с помощью xst.

На VHDL даже "hello world!" выглядит как исходник windows.

Что взять о выкидыша АДЫ и ПАСКАЛЯ?..

Как однажды было сказано (в вольном переводе): VHDL - для имитации, Verilog - для производства.

-

-

Конечно, я немного категоричен, но когда достаточно давно я исследовал первые версии PCI-Wishbone, меня на него все время как бы "рвало".

Да, в ряде случаев, данное решение может успешно работать, и имеет право на существование, но даже такой маленький факт, что оно в принципе не удовлетворяло требованиям setup=7 ns для PCI initiator на современных ПЛИС (про PCI 66 даже речи не шло), и никто по этому случаю особенно не заморачивался, кажется мне диким (не знаю как сейчас, но уверен, что подход не изменился - универсально, некачественно, и громоздко).

Одним словом, приятно обсуждать и критиковать интересные и качественные продукты, но не изначально посредственные (все сугубое ИМХО).

Тут ответ очень простой: не нравится - покупайте или делайте сами. Либо деньги, либо время. Другого ответа нет, ибо воровство не решение.

Не знаю как это все у Вас работало. Мы меняли размер FIFO от 8 do 256 - результатов нуль - при любых размерах только 3-4 слова идет на полной скорости, а потом затык...В конце-концов мы похоронили эту привлекательную идею и поставили PCI core от PLDA - все сразу заработало, запело и затанцевало.

Как ни странно, работало. Но сильно зависело от компа. На одном интеле вообще не завёлся (решилось только заменой биоса материнки). На Ксеоне - слишком короткие транзакции (особенности его моста). На амд - всё нормально (там просто всё по стандарту PCI сделано).

Да и вообще, этот WB-PCI нужно уметь готовить :). PCI66 на втором виртексе 2000 он держал.

PS: а за PLDA платить надо. Нам пока дешевле в глюках разобраться. Благо их немного.

-

На первую ссылку отвечаю: у меня фифо было больше барста (с АЦП данные гнали по триггеру), что совершенно логично с т.з. работы шины PCI со многими мастерами.

На вторую: многое зависит от материнки и воткнутых железяк.

Поиск потенциального изготовиттеля

в Изготовление ПП - PCB manufacturing

Опубликовано · Пожаловаться

Есть линейка фотодиодов. На стекле. Выводы от них идут с периодом 100 микрон. требуется сделать плату-переходник на что-то вроде QFP или BGA, желательно с предусилителями (>80 каналов). Возможно-ли это? За деталями - в приват или на почту.

Лимит - около $10 тыс за 2-4 образца.