LordVader

-

Постов

127 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные LordVader

-

-

В принципе да, основная задача вывод на ТВ, но как опцию хотелосьбы иметь возможность подключения к VGA монитору.

Да кстати не в курсе, есть ли какието особенности вывода на LCD ТВ(автомобильный) в отличии от обычного кинескопного, через выход SVideo.?

КМК если видеосигнал будет удовлетворять стандартам ТВ-сигнала, то пофиг, какой там телевизор - лсд или црт.

Насчёт ВГА опять же имхо - что с телевизионным он пересекается слабо, общими будут разве что только счётчики адреса, откуда читаются видеоданные =)

Да кстати не в курсе, есть ли какието особенности вывода на LCD ТВ(автомобильный) в отличии от обычного кинескопного, через выход SVideo.?А у него цифровых входов (DVI) нет? LCD в любом случае оцифрует аналоговый сигнал - так зачем вам его из цифры перегонять в аналог...

Врят ли там есть цифровой вход.

А зачем интересно acex понадобился?Уж не лучше ли второй циклон взять?Ну или может быть второй макс.

Сейчас мне вообще кажется, что лучше начать с MAX обычных - epm7064s например. Преимущества, существенные для совсем начинающих: напряжение питания 5в, не надо конфигураторов с прошивками, есть кристаллы в PLCC (а значит, можно использовать панельку под PLCC штыревую).

-

Добрый день!

Посоветуйте пожалуйста самую простую плис, на которой можно реализовать простеникий VGA адаптер для AVR с разрешением 800*600 8Bit.

Из обвязки планирую подцепить SRAM 512K и чтонибудь типа MC13077 для вывода S-Video.

Спасибо.

Подразумевается выход на ТВ? Тогда о каких 800х600 может идти речь?

На тв где-то 312 строчек в кадре (а видимых - и того меньше), или 625 в том, который 2 по 50 подряд (чересстрочная развёртка). И по горизонтали хорошо если 640 точек удастся разглядеть.

Например, 512х256 - вполне влезет в бесчересстрочный кадр.

Насчёт плис - видел реализацию ВК 256х192х4 бита на epm7128, но она читала данные из ДРАМ.

Наверное, acex1k ep1k10 хватит за глаза :)

-

У вас оптимизация включена? Попробуйте оптимизировать по площади.

Ну это первое, куда я ткнулся. Было включено 'Area'.

По умолчанию Квартус раскладывает асинхронную логику в одни ячейки, а регистры в другие. Для того чтобы этого не происходило ему нужно помочь. А именно: Assigments\Settings\Fitter Settings\More Settings\Auto Packed Registers -> On. ;)Не помогло.

Один очень шарящий чел не пожалел своего времени и разобрался. Говорит, что данную опцию фиттер в квартусе молча игнорирует. А чтобы всё-таки не 16 LE было, он поправил библиотечный файлик lpm_add_sub.tdf в недрах квартуса, заменив USE_CS_BUFFERS = 1 на 0.

Стало не 8, а 9, всё-таки, младший разряд отдельным LE генерится, а перенос с него - другим.

Интересно, чем альтеровцы думали, когда такое ваяли? :maniac:

-

Опубликовано · Изменено пользователем LordVader · Пожаловаться

Вот пишу простейший код:

module adder( clock, in1, in2, out ); input clock; input [7:0] in1; input [7:0] in2; output [7:0] out; reg [7:0] out; always @(posedge clock) begin out <= in1 + in2; end endmodule

синтезю, и что же? 16 LE! При этом 8 LE - сам сумматор, а ещё 8 - регистры на его выходах.

Странно, вроде бы, судя по даташиту, в одной LE должны сочетаться arithmetic mode и триггер на выходе...

Попробовал играться семействами (чисто из интереса, нужно-то для acex'а всё равно): для некоторых так и остаётся 16 LE, для других (например, stratix и cyclone) - получается 8.

В чём тут "собака порылась"?

PS: квартус - 6.0 web edition

-

Ой, похоже у меня действительно глюки =)

Но всё же у филипса эти инверторы чуть ли не 3 штуки подряд в даташитах рисуются, на HC/HCT. Наверное, навеяло ;)

Для ACT у ST явно нарисован 1 инвертор на 2 транзисторах.

Тогда единственный вопрос - какого порядка резисторы в ООС для последовательного резонанса (2 инвертора)? На ттл они порядка нескольких сотен ом, а тут?

-

По какой причине вы сделали заключение что не сработает? Триггеров Шмитта на входе у 74ACT04 нету. Резисторы в ООС нужны будут лишь значительно бОльшего номинала, чтобы ввести лог. элементы в линейный режим, и при этом обеспечить мягкий запуск. Вот и все отличия. Если на гармониковый кварц не нарветесь конечно. В этом случае с помощью последовательного LC на входе возможно придется "давить" основную гармонику. Но это навряд ли.

А вы какой резонанс имели в виду? Последовательный (2 инвертора) или параллельный (1 инвертор)?

Насчёт последовательного - где-то в инете вычитал, насчёт параллельного - сомнения такого плана: в филипсовских даташитах пишут, что hct/act содержат доп. инверторы, т.е. например 74act04 - это 3 инвертора друг за другом. Сомнения в том, что такая штука запросто выведется в линейный режим.

Осторожней с буквой T в названии!Мы однажды с этим сильно накололись. Тоже делали кварцевый генератор на одном инверторе, поставили HCT вместо HC и в итоге получили сигнал с неправильной скважностью (не меандр).

Спасибо за предупреждение :)

А сильно 'неправильно' получилось? В смысле что, 10% заполнение было, или 40%?

-

Могу предложить страничку по JTAG на моем сайте.

Спасибо! "Буду почитать"!

-

Ситуация: есть несколько свободных вентилей 74ACT04, необходимо собрать кварцевый генератор на них. Вопрос отображён в топике.

Насколько я догадываюсь, традиционная для 7404/74LS04/74ALS04 схема с 2 инверторами и последовательным резонансом не сработает для 74ACT04. А сработает ли традиционная схема с 1 инвертором и параллельным резонансом?

Да, частоты кварца 20-24 МГц

PS: вариант с отдельным 4-ногим генератором не проходит по цене (тем более, что нужно 2 генератора). Отдельный чип типа 74HCU04 ставить тоже не хотелось бы.

-

10x за пинок в нужном направлении =)

-

Насколько я понимаю, даже когда девайс сконфигурён для какого-либо метода загрузки прошивки (пинами MSEL0,MSEL1), возможна загрузка через JTAG.

А вот возможно ли дёргание ногами девайса через JTAG? Ну например, к девайсу подключена flash, хочется её зашить. ПОдскажите, где и что читать по этому поводу.

-

Розница на altera : http://www.altera.ru/cgi-bin/price/price

За ссылку спасибо, не подозревал, что там в розницу торгуют =)

acex+epc2 ~ 17$+26$=43$ep1c3+epcs1~ 12$+4$=16$

--------------------------------

связка на cyclone стоит в 2,68 раза дешевле

Ну, это некорректное сравнение. У меня например acex1k шьётся процессором из flash'и -> минус 26$ =)

-

Кстати, продолжая тему. У моего знакомого аналогичная ситуация: есть прошивка для epm7032 (без буквы S) в виде *.pof (сорцы утеряны). Её можно зашить на параллельном программаторе в epm7032S и она при этом работает, НО занимает опять же ноги JTAG'а. Вопрос - можно ли как-то поправить ноги на другие (используются далеко не все), открыв JTAG? А то опять же приходится (знакомому) ходить в ЭФО и там шить.

-

Ну задача глобально уже поставлена и кристалл выбран (ацекс1к), + макс3000 для бута, ну заодно и для переключения частот. Схема существенно 5-вольтовая, потому и ацекс.

////////////////////////////////////////////////////////////////////

Что значит схема пятивольтовая. ТТЛ или МОП уровни.

ТТЛ.

Любой циклон, циклон2 с загрузочным ПЗУ EPCS в разы дешевле той связки, которую Вы выбрали.Добавить сюда 10 рублей на преобразователи уровней или буфера, терпимые к уровням 5В(Здесь море рекомендаций по фирмам и сериям), и все дела. Ну просто неограниченные возможности.

[глядя на efind.ru] Что-то я не сказал бы, что даже самые младшие циклоны в разы дешевле ацексов. Вот например ep1k30 в ткфп-144 я покупаю в розницу (!) за 450руб, а за сколько я куплю самый младший циклон в таком же корпусе?

Да ещё геморрой с 5в tolerancy.

А макс у меня - для того, чтобы процессор смог забутить ацекс, в самом начале, как бонус - прошивка ацекса в флеше обычном.

-

Обычно сначала ставиться задача. И под нее выбирается кристалл. Например с pll. Там можно и свитчер организовать, и любой делитель в разумных пределах.

Ну задача глобально уже поставлена и кристалл выбран (ацекс1к), + макс3000 для бута, ну заодно и для переключения частот. Схема существенно 5-вольтовая, потому и ацекс.

А если речь идет о переходе из одного клокового домена в другой (глобаьный), то и переключатели не нужны. В конференции об этом подробно расписано. Наберте в поисковике слово метастабильность.С этим более-менее всё ясно.

-

В этом вроде бы все и заложено. Вы выносите на обсуждение схему, анализ которой требует больших временных затрат. У кого они есть. При этом игнорируете схемные решения с приличным анализом.

Главное отличие Вашей и другой схем это в тактировании триггеров.

Но самое главное, такая схема некорректна по определению. Без констрейнов по всем путям Вы долны получить сплошные clock skew, некорректные clock hold.

Ну я в принципе согласен, что некорректная. Но дело в том, что у меня все сигналы выбора - асинхронные, а насколько я понял, в таком случае надо использовать схему переключения для 'unrelated' клоков, даже если сами клоки 'related'. Ведь надо асинхронный сигнал через цепочку из 2 триггеров пропускать.

Я в лоб первел. Если хотите посмотритеСпасибо!

Вопрос - почему у вас

always @(posedge clock1)begin

reg_clock1_a <= a;

end

always @(negedge clock1)

begin

reg_clock1_b <= reg_clock1_a;

end

то posedge, то negedge?

В этом какой-то глубинный смысл именно для данной схемы, или просто, чтоб быстрее проходило?

-

Только вот укорочение импульса осталось - оно ведь произрастает из того, что клок, генерируемый делителем, запаздывает на Tco триггера относительно неделенного клока, и при переключении с быстрого на медленный получается первый период на это самое Tco меньше остальных.

Ну да, укорочение медленного клока осталось - но главное, что не быстрого.

-

-

Спасибо всем!

Насколько я понял, обе схемы переключения клоков функционально аналогичны моей (часть схемы не ниже 4 триггеров ряд): не дают глитчей. Но зато выглядят изящней :)

Насчёт предложенного переключающегося делителя пополам - промоделил сейчас в квартусе, он к сожалению укорачивает 1 клок при переключении с медленной частоты на быструю.

-

Опубликовано · Изменено пользователем LordVader · Пожаловаться

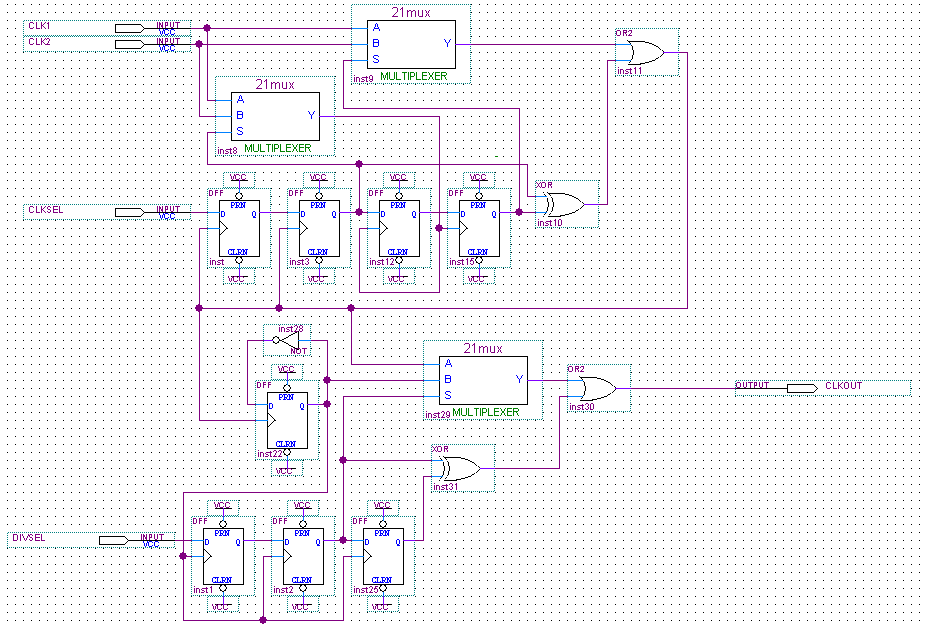

Задача:

Имеем 2 независимых клока (скажем, 20 и 24 МГц), требуется сделать переключататель, который на выходе даёт 20,10,24,12 МГц (выбор - 2 асинхронными сигналами). Требуется, чтобы на выходе не появлялось импульсов короче, чем полупериод самого быстрого входного клока.

Родил вот такую схему (нарисовано в квартусе)

, насколько она корректна?

, насколько она корректна?PS: вполне понимаю, что схема асинхронная и на очень быстрых клоках всё равно возможны глюки. Но макс. частота такая, как указана выше, а моделирование вроде бы не выявляет глитчей (целевой чип - epm3032).

-

зашел на сайт Алтеры и не обнаружил там в Devices ACEX.

Можно найти поиском, далее по ссылкам. Видимо, просто с морды убрали ссылки, а сами все страницы с доками и етц - остались на месте.

-

Спасибо, буду рисовать схему.

-

CS и nCS - по вкусу, лишь бы они в момент конфигурации имели нужные уровни.

В смысле, только в момент записи байта, или всё время, пока фпга в режиме конфигурации?

-

Впервые этим занимаюсь, посему вопросы:

1. В режиме загрузки все пины типа DATA0-DATA7, nCS, nWS и nRS - 5v tolerant?

2. DATA0 пин требуют не оставлять floating, и притянуть к 0 или 1. А если его оставить присоединённым к шине данных, по которой будет и дальше гулять инфа (5вольтовая, а также иногда floating будет, но недолго) - можно, или лучше отвязывать на время обычной работы от шины (пускать через буфер)?

3. В конфиг мануале часто упоминается, что CS и nCS должны быть active during configuration и initialization. Но по смыслу это обычные chip select'ы, и соответственно их разумно подключить к дешифраторам адреса, скажем, в то время как nRS и nWS - к стробам записи и чтения. То есть CSы могут спонтанно выбираться без стробов чтения и записи или наоборот - стробы дёргаться при неактивных CSах. Это прокатит, или опять городить огород, чтоб CS'ы стояли как вкопанные, а стробы давались только в нужные моменты?

4. по опыту, хватает ли 30-50к пуллапов у сабжа в режиме загрузки например чтобы удержать старшие разряды ША и CS'ы всех неиспользуемых м/сх памяти в состоянии единицы или лучше внешние пуллапы порядка 1-10к понаставить на критичные цепи?

-

Вот есть разные i2s цапы - например CS4340, WM8725 и другие.

В даташитах на них везде сказано - базовая частота должна быть в 256 (384, 192, етц) раз больше, чем частотота ввода семплов.

А вот в даташите TDA1543 ничего не сказано про базовую частоту. Соответственно, непонятки с ним - как вводить, какую частоту давать? Если дать x256 - сдюжит?

Какие ещё простенькие и дешёвенькие аудиоцапы существуют - 16бит 44100гц вполне хватает, параметры по качеству - любые. Главное - наличие в единичных количествах в магазинах/фирмах, а также в мелких партиях (10-100 шт), более-менее нормальный корпус (дип или соик).

MP3 декодер

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

А вместо мп3 - OGG можно? Это типа мп3, но лучше жмёт и полностью открытый.

http://www.vorbis.com/

Когда-то давно у меня плеер этих оггов с оф. сайта собрался без вопросов в мсвц. Так что, скорее всего соберётся и под любую платформу.