Kolia

Свой-

Постов

187 -

Зарегистрирован

-

Посещение

Весь контент Kolia

-

Через UART можно залить программу, нужно скачать загрузчик с сайта и собрать простую схему с кварцем.

-

Beremiz

Kolia ответил yanvasilij тема в Программирование

На оф. сайте представлены все проекты https://beremiz.org/apps Можно скачать IDE для панели http://www.smarteh.si/data/web_support_files_file/smartehide 5.3.0.0 setup.exe и покопаться в исходниках. Ничего другого не находил. -

Я_ПЛаКал(YAPLC-IDE)

Kolia ответил Ekka тема в Cредства разработки для МК

Возможно потому что адреса в HEX Файле начинаются с 0x10010000, а должны быть с 0x08008000 Попробуйте сделать из Hex бинарник и залить по адресу 0x08008000 -

Я_ПЛаКал(YAPLC-IDE)

Kolia ответил Ekka тема в Cредства разработки для МК

Там "хитрый" программатор. на сколько я помню, давно было... После нажатия кнопки залить программу, контроллер должен перейти в режим Boot по UART, с перезагрузкой. Далее зашивается программа стандартным программатором по UART с помощью утилиты. Затем переход в режим загрузки с флэш. Выбор режима загрузки вроде делает сам МК, в проекте есть специальная ножка для этого, вроде PLC_BOOT_PERIPH. Функция void plc_boot_mode_enter(void). Если это сделать нет возможности, то можно залить сгенерированный проект вручную по адресу 0x08008000 StLinkom и затем просто подключится к нему из Beremiz. 2. Обязательно, без него работать не будет. 3. Залить проект Runtime в МК, подключится к МК из Beremiz и залить туда еще то что генерирует Beremiz. -

PESD5V2S2UT W78E516DPG plcc atmega32a-au (tqfp) stm32w108cbu63tr stm32l152rbt6 tms320f2801pza at89c51ed2 (plcc68) lsm303dlm apQ84SN06A STS1NK60Z AD7714YN dip LT1076CT Дисплей DOGL128W-2

-

прошивка для EC2 Serial Adapter

Kolia ответил bh7fculvf65 тема в MCS51

Вроде этот, но не уверен давно дело с ним имел... ec2.zip -

ADSP-21XX Ez-kit Lite - полный комплект, диск с ПО, коробка + AD1847 в подарок ПО на диске - Limited version(8k) Забирать -> РБ, Минск https://content.onliner.by/forum/639/570/18...8bf83b78220.jpg

-

Вопрос решен...

-

Zynq SD-card

Kolia опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день. Как подключить контроллер SD-карты sdps в XPS PlanAhead? В списке ядер не нашел. Спасибо. -

C PlanAhead лучше работать добавляя IP-ядра проектов в XPS (xilinx platform studio). Проект исчез, т.к. сайт закрыт. На сайте фирмы где брал модуль есть проект http://www.axonim.by/ru/products/Processor..._AX-SoM-XC7Z020. Но он вам не подойдет т.к. это базовый (нулевой) проект для модулей AX-SoM-XC7Z020.

-

Как правильно подключить *.ngc сгенерированный CoreGen к PlanAhead -> XPS, если просто скопировать XPS ругается на отсутствие vhdl файла, если скопировать туда же файл vhdl сгенерированный CoreGe, то ругаться перестает, но уже planAhead выдает ошибку такого рода [NgdBuild 604] logical block 'module_111_i/axi_stream_generator_0/axi_stream_generator_0/axi_fifo_32b_inst' with type 'fifo_generator_v9_3' could not be resolved. A pin name misspelling can cause this, a missing edif or ngc file, case mismatch between the block name and the edif or ngc file name, or the misspelling of a type name. Symbol 'fifo_generator_v9_3' is not supported in target 'zynq'. Подключить пытаюсь файл CoreGen из этого примера

-

Zynq DMA+FIFO

Kolia опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

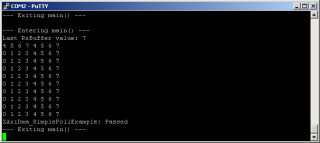

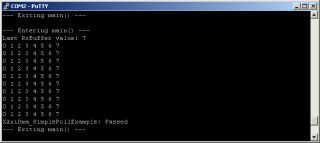

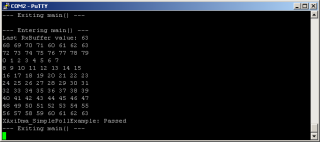

Чет никак не могу понять что за глюки в работе dma. Беру стандартный пример все работает, только там пример гоняет одно и тоже туда-сюда. Как данные в передаче, появляются какие-то непонятки. Вот результат работы примера Тут добавил сброс DMA перед отправкой стало лучше Тут отправляю данные пачками с разными данными (числа от 0 до 80) Т.е. как я понял 20 байт из предыдущей посылки, ходя такого быть не должно Проект https://yadi.sk/d/300_ExrCmACZW За основу брал этот проект https://github.com/fpgadeveloper/zc706-axi-dma-fifo Нужно просто передать данные из плис в проц, как проще сделать, можно ли без ДМА? -

Скорее всего кокой-то буфер накладывается на данные (выходит за свои пределы).

-

Код рабочий, ошибка была в том что не подал тактирование на таймер в XPS.

-

Вопрос решен

-

Есть еще память RTC и Backup ОЗУ, правда нужна батарейка, зато доступ как к обычной ОЗУ

-

Zynq Timer

Kolia опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Не получается настроить таймер в SDK. Не могу понять почему не работает. Может кто поможет где косяк? #define TIMER_LOAD_VALUE (0xF8000000) #define TIMER_DEVICE_ID XPAR_XSCUTIMER_0_DEVICE_ID #define INTC_DEVICE_ID XPAR_SCUGIC_SINGLE_DEVICE_ID #define TIMER_IRPT_INTR XPAR_SCUTIMER_INTR static XScuTimer Timer;//timer static XScuGic Intc; //GIC static void SetupInterruptSystem(XScuGic *GicInstancePtr,XScuTimer *TimerInstancePtr, u16 TimerIntrId); void TimerStart(void) { XScuTimer_LoadTimer(&Timer,TIMER_LOAD_VALUE); XScuTimer_Start(&Timer); xil_printf("Timer run..\n\r"); } void TimerInit(void) { XScuTimer_Config *TMRConfigPtr; // Инициализация TMRConfigPtr = XScuTimer_LookupConfig(TIMER_DEVICE_ID); XScuTimer_CfgInitialize(&Timer,TMRConfigPtr,TMRConfigPtr->BaseAddr); XScuTimer_SelfTest(&Timer); // Загрузка таймера XScuTimer_LoadTimer(&Timer,TIMER_LOAD_VALUE); // Set up the Timer interrupt SetupInterruptSystem(&Intc,&Timer,TIMER_IRPT_INTR); xil_printf("Timer config..\n\r"); // Запуск таймера //XScuTimer_Start(&Timer); //xil_printf("Timer run..\n\r"); } static void TimerIntrHandler(void *CallBackRef) { XScuTimer *TimerInstancePtr = (XScuTimer *) CallBackRef; XScuTimer_ClearInterruptStatus(TimerInstancePtr); //XScuTimer_LoadTimer(&Timer,TIMER_LOAD_VALUE); //user code -->> xil_printf("****Timer Event!!!!!!!!!!!!!****\n\r"); //<<-- //XScuTimer_Start(&Timer); } static void SetupInterruptSystem(XScuGic *GicInstancePtr,XScuTimer *TimerInstancePtr, u16 TimerIntrId) { XScuGic_Config *IntcConfig; //GIC config Xil_ExceptionInit(); //initialise the GIC IntcConfig = XScuGic_LookupConfig(INTC_DEVICE_ID); XScuGic_CfgInitialize(GicInstancePtr, IntcConfig, IntcConfig->CpuBaseAddress); //connect to the hardware Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler, GicInstancePtr); Xil_ExceptionEnable(); //set up the timer interrupt XScuGic_Connect(GicInstancePtr, TimerIntrId, (Xil_ExceptionHandler)TimerIntrHandler, (void *)TimerInstancePtr); //enable the interrupt for the Timer at GIC XScuGic_Enable(GicInstancePtr, TimerIntrId); //enable interrupt on the timer XScuTimer_EnableInterrupt(TimerInstancePtr); // Enable interrupts in the Processor. Xil_ExceptionEnableMask(XIL_EXCEPTION_IRQ); } -

https://www.segger.com/jtag-isolator.html

-

Ищите таблицу Special Function Register (SFR) Memory Map на свой контроллер и подставляйте нужные адресса, при использовании sbit обращение будет идти с битовой области памяти bdata

-

Всем спасибо, разобрался. Добавил к проекту planAhead файлы из ISE ( vhd, ngc и ucf). Если кому интересно вот базовый проект

-

Да спасибо работает... После загрузки старая конфигурация слетела, я так понимаю чтобы работало все без изменений нужно мигалку добавить к стандартному проекту, он в planahead. Что-то я не могу сообразить как спарить конфиг сгенерированный Xilinx Platform Studio и эту мигалку.

-

Zynq простой проект

Kolia опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день. Пытаюсь разобраться с zynq7020, набросал простую мигалку, все компилится, будет ли он работать если зашить в zynq? И не сломается ли зашитая конфифугурация? library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity led is Port ( clk_100 : in STD_LOGIC; led_1 : out STD_LOGIC); end led; architecture Behavioral of led is constant prescaler: STD_LOGIC_VECTOR(23 downto 0) := "101111101011110000100000"; -- 12,500,000 in binary signal prescaler_counter: STD_LOGIC_VECTOR(23 downto 0) := (others => '0'); signal newClock : std_logic := '0'; begin led_1 <= newClock; countClock: process(clk_100, newClock) begin if rising_edge(clk_100) then prescaler_counter <= prescaler_counter + 1; if(prescaler_counter > prescaler) then -- Iterate newClock <= not newClock; prescaler_counter <= (others => '0'); end if; end if; end process; end Behavioral; Смущает вот это -

Есть SAB 80C517A-N18-T3 новые 2 штуки в Минске