-

Постов

1 951 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные sonycman

-

-

Чертовщина творится.

Убрал схему VGA выхода - PLL стала стабильно выдавать 32 МГц, выше пока не пробовал.

До этого выше 29 МГц не поднималось.

Что изменилось в разводке - если раньше в моей схеме был один MMCM и одна PLL в одном CMT блоке, то теперь вивадо развёл их по разным CMT, на разных сторонах чипа.

Плюс раньше вивадо в цепи заворота тактовой между IOBUF и входом PLL вставлял BUFG, то теперь его нет.

Больше вроде ничего не поменялось.

Как объяснить повышение частоты PLL?

-

В 04.08.2023 в 22:23, Beby сказал:

1. Описать подробно: чем и как питается AUX ?

2. Что ещё (кроме VCCaux) питается этой же цепью ?

3. Какие настройки IO-ног для заворота тактовой используете ? (Std, Drive, Slew, LowPower, Pull-Up/Down/Keeker и т.п.)

4. Можете ли использовать какой-либо дифференциальный стандарт (например, LVDS) ?

5. Что ещё расположено в том же банке, в котором используется заворот тактовой ?

6. Как у вас с фазовыми шумами в этом завороте (в спецификацию на PLL укладываетесь) ?

Плата используется такая: Z-Turn v1.

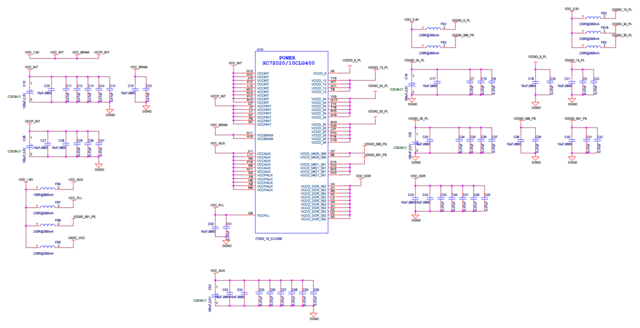

Вот схема питания:

Настройка пина: LVTTL, FAST, 8ma.

Можно попробовать настройку с бОльшим током...

Дифф. стандарт тоже пока не пробовал, надо глянуть в эту сторону.

В этом-же банке работает VGA выход на 28.5 МГц, который можно выключить, в принципе.

По поводу фазового шума, думаю, вся эта идея не укладывается в спецификацию.

В настройке PLL джиттер выставил по максимуму - 1 нс. Какой он там по факту - не скажу, но вероятнее всего поболее будет.

Есть ещё идея уменьшить разрядность oserdes с 8-ми до 6-ти бит, то есть снизить коэфф. умножения до 6-ти, чтобы уменьшить входную частоту PLL.

Но джиттер в этом случае только вырастет, мне кажется.

-

Работает без проблем с часотой до 29 МГц, выше PLL не лочится и нормального клока на ее выходе нет.

Получается,, входной пин не берет частоту выше 232 МГц (29 * 8)?

-

Beby

Благодарю за помощь, собралось, когда PLL инстанциировал как у Вас, в исходнике, а не через блок-дизайн.

Дальше пришлось пин, через который генерируется клок, повесить на свободно висящий пин чипа, иначе 250МГц уже не схватывается входным буфером.

Всё заработало, 576р @27МГц монитор подхватил как родные!

С 32 битным счётчиком такой генератор позволит мне подгонять частоту с отклонением менее наносекунды от кадра к кадру!

-

В 07.07.2023 в 15:12, Beby сказал:

Странно, зачем использовать 2 пина, когда должно быть достаточно 1 CC пина ?

Вот пример на VHDL, компилируемый ISE 14.7 для XC7Z010-1CLG400:

library ieee; use ieee.std_logic_1164.all; library unisim; use unisim.vcomponents.all; entity IO_Test is port ( IN_CLK_1: in std_logic; IO_CLK_2: inout std_logic; OUT_Q: out std_logic ); end entity; architecture Tushka of IO_Test is signal CLK_1_UB: std_logic; signal CLK_1: std_logic; signal CLK_1_Out: std_logic; signal CLK_2_UB: std_logic; signal CLK_2: std_logic; signal Q: std_logic := '0'; begin CLK_1_IBUFG: component IBUFG port map ( I => IN_CLK_1, O => CLK_1_UB ); CLK_1_BUFG: component BUFG port map ( I => CLK_1_UB, O => CLK_1 ); CLK_1_ODDR: component ODDR port map ( D1 => '0', D2 => '1', Q => CLK_1_Out, CE => '1', C => CLK_1 ); CLK_1_OBUF: component OBUF port map ( I => CLK_1_Out, O => IO_CLK_2 ); CLK_2_IBUFG: component IBUFG port map ( I => IO_CLK_2, O => CLK_2_UB ); CLK_2_BUFG: component BUFG port map ( I => CLK_2_UB, O => CLK_2 ); process( CLK_2 ) begin if rising_edge(CLK_2) then Q <= not(Q); end if; end process; Q_OBUF: component OBUF port map ( I => Q, O => OUT_Q ); end architecture;А если попробовать полноценный oserdes и завести CLK_2 на вход pll?

-

В 03.07.2023 в 19:29, quato_a сказал:

Интересно как тут решается вопрос синхронизации, клоки передатчика и приёмника будут отличаются по фазе и частоте.

Для идеального выравнивания сигналов по времени фрейма делаю HDMI клок чуть быстрее, а лишние такты клока блокирую через BUFGCE.

В 03.07.2023 в 19:57, Inanity сказал:По идее метод должен работать. По идее ещё можно вставить tristate buffer и отключить его навсегда. Тогда клок не будет покидать пределов ПЛИС, что может быть удобно, если не хочется светить этим клоком наружу или если по какой-то причине неиспользованный Clock-Capable пин прижат к земле или питанию банка.

Не получается без вывода клока наружу.

Только используя два пина - выходной и входной...

-

В 03.07.2023 в 09:54, quato_a сказал:

А видеосигнал идёт без сопровождаемой пиксельной частоты?

Видеосигнал VGA, различной частоты.

-

В 02.07.2023 в 01:36, quato_a сказал:

не понял, так PLL цинка походит?

Только для проверки.

В 02.07.2023 в 01:36, quato_a сказал:хм, вроде в clockwizard (PLL, MMCM) достаточно большая гибкость по умножителю/делителю, в моих задачах всегда удавалось сделать нужный клок, например из 200 -> для fullHD 148.5 МГц

сейчас не у вивадо, но уверен, что ровные 27 МГц можно сделать спокойно

Мне нужно генерировать частоту под входящий различный видеосигнал и синхронизироваться под него с точностью до нескольких сотен наносекунд на фрейм.

На такое куцые ФАПЧ простого цинка не способны, к сожалению...

-

В 30.06.2023 в 22:16, quato_a сказал:

какой номинал клока не получается сформировать?

Да всего 27 МГц. По осциллографу клок вполне ровный, частота по осциллографу 26.96, видеосигнал 576p 50 герц.

Монитор на него не реагирует.

Беру клок такой-же частоты с PLL цинка (без хитрого генератора), подаю на схему вместо сгенерированного - все работает.

На ultrascale есть периферийный блок display port с отличным генератором частоты, у пятых циклонов отличные PLL с 24 битным фракционным делителем, а вот у простого цинка нихрена подходящего 😞

Придется ставить внешний синтезатор частоты.

-

В 30.06.2023 в 10:21, fingertouch сказал:

Разве в вашей статье говорится про "завести с этого же пина"? Там же на картинке фигурирует выход за пределы FPGA и ввод через CC-pin.

Именно с этого-же пина:

IOBUF genclkio(.I(w_pin), .IO(io_pin), .O(pll_input), .T(1'b0));

w_pin - выход oserdes, pll_input - вход PLL.

Статья довольно мутная, не знаю, где там автор проверял на практике.

Проблему решил, использовав два пина. Идея, в общем-то работает, ФАПЧ лочится, но такой клок как пиксель клок видеосигнала использовать не получилось - монитор не распознаёт сигнал.

Видимо, слишком большой джиттер...

-

Приветствую.

Пытаюсь реализовать генератор частоты для подстройки под различный видеосигнал.

У цинка весьма ограниченные PLL с куцым 3 битным дробным делителем, которые не могут сгенерировать производьную частоту.

Наткнулся на вот такую статью:

Breaking all the rules to create an arbitrary clock signal

Смысл там в том, чтобы генерировать клок на обычной логике, на счетчике, а потом, прогнав его через oserdes (умножив, как я понимаю, его на 8 для снижения фазового шума), подать на вход PLL, которая снизит джиттер и уже этот сигнал использовать для тактирования.

Попробовал в железе - роутер не может развести выход oserdese2 на вход pll.

То есть не получается вывести на внешний пин сигнал с сериализатора, и потом с этого же пина завести этот сигнал на вход pll.

Это я что-то делаю не так, или действительно это не возможно?

-

Ultrascale имеет когерентные порты, работа через которые позволяет обойтись без инвалидации кэша.

По крайней мере в baremetal это работает.

-

В 24.04.2023 в 15:05, Quantum1 сказал:

Сгенерированный код FSBL смотриться в Vitis, и его спокойно можно разобрать на конкретные этапы - настройка тактирования, периферии, памяти, изоляции ну итд... Но в нем !нет куска! который брал бы и к примеру копировал пользовательскую программу по выбранному адресу, FSBL обрывается на настройках.... отсюда и вопрос, при создании бутлодеров Vitis сам дописывает эту загрузку? Т.е. пользователю ее код просмотреть и проконтролировать невозможно?

Как это нет?

Да в том-же xfsbl_main.c функция main:

XFSBL_STAGE3: Load the partitions: XFsbl_PartitionLoad - загрузка пользовательской программы.

XFSBL_STAGE4: Handoff to the applications: XFsbl_Handoff - запуск программы.

Всё это находится за 5 минут 👀

-

В 02.04.2023 в 14:31, Quantum1 сказал:

Как начинается выполнение твоего кода?

После загрузки пользовательской программы, FSBL передает управление ей - переходом по адресу Entry point.

Вроде бы доки в сети доступны, курите их и закрепляйте практикой.

-

В 19.10.2022 в 15:01, zorromen сказал:

Так от сюда и возьмите http://we.easyelectronics.ru/STM32/programmnyy-dekoder-mp3-perehod-na-platformu-stm32f407.html только под себя настроите. Так код рабочий вполне.После коррекции DMA открывает все, но нужно учесть еще и такой вариант, что Стерео может иметь 2304 и 1152, а моно 1152 и 576, https://www.silabs.com/documents/public/application-notes/an1112-efm32-helix-mp3-decoder.pdf

Я встретил такие файлы, пришлось подстроиться под этот момент.

Спасибо! Ну мне нужен только mp1 layer3, а там проще - только 1152 сэмпла для моно и 2304 для стерео.

-

А может кто дать линк на исходники этого декодера?

-

В 27.09.2022 в 14:00, yes сказал:

и в AArch32 архитектуре? в ARMv7 еще было

я не имею опыта с модными АРМами (i.mx6 то есть Cortex-A7/9 последнее, что трогал), интересуюсь "по инерции"

Неправильно выразился - в 32 битном режиме есть, конечно, я про 64 бита (aarch64).

-

В 26.09.2022 в 12:10, yes сказал:

насколько я знаю, ARM рекомендует не использовать STM/LDM инструкции для продвинутых Cortex-A

В ARMv8-a нет этих инструкций, есть только STP/LDP - load/store register pair.

Если юзать NEON можно ворочать сразу по 16 байт (Qx/Vx регистры), но на ARMv7-a тоже самое, кажется?

-

В 24.09.2022 в 21:06, mantech сказал:

В чем принципиальная прелесть этих 64бит? Кроме доступа к большим объемам ОЗУ?

Не знаю, мне стало интересно, вот и решил глянуть.

Наверное, ещё такие камешки могут быстрее ворочать большими объёмами данных?

Вообще, машинный код ARMv8-A мне показался больше похожим на MIPS или RISC-V, чем на собственно ARM... :)

-

На форуме ARM ответили, что они сейчас не делают супер-оптимизированные библиотеки для ARMv8-A, а вместо этого есть оптимизированные процедуры отдельно вот здесь: ARM-software / optimized-routines

И на том спасибо :)

Странно, конечно, что либы для нового 6-го компилятора не дотягивают до либ старого 5-го.

Кстати, прогнал Dhrystone Benchmark v2.1 (из Vitis 2022.1), оптимизация О2, DMIPS/MHz:

GCC 11.2: 2.88

armclang v6.16: 5.75

Почему-то получилось, что гнусь в два раза медленнее

-

Пробую хвалёный ARM Compiler 6 из под ARM Development Studio 2021, версия компилятора 6.16.

Скомпилировал простую програмку в режиме aarch64 с вызовом memset, оптимизация О2 (пробовал О3, даже Omax).

Дизассемблер этой функции:

_memset 0x00008c14: b4000261 a... CBZ x1,0x8c60 ; _memset + 76 0x00008c18: 36000060 `..6 TBZ w0,#0,0x8c24 ; _memset + 16 0x00008c1c: 38001402 ...8 STRB w2,[x0],#1 0x00008c20: d1000421 !... SUB x1,x1,#1 0x00008c24: f1000828 (... SUBS x8,x1,#2 0x00008c28: 54000143 C..T B.CC 0x8c50 ; _memset + 60 0x00008c2c: 36080060 `..6 TBZ w0,#1,0x8c38 ; _memset + 36 0x00008c30: 78002402 .$.x STRH w2,[x0],#2 0x00008c34: aa0803e1 .... MOV x1,x8 0x00008c38: f100103f ?... CMP x1,#4 0x00008c3c: 540000a3 ...T B.CC 0x8c50 ; _memset + 60 0x00008c40: d1001021 !... SUB x1,x1,#4 0x00008c44: f1000c3f ?... CMP x1,#3 0x00008c48: b8004402 .D.. STR w2,[x0],#4 0x00008c4c: 54ffffa8 ...T B.HI 0x8c40 ; _memset + 44 0x00008c50: 36080041 A..6 TBZ w1,#1,0x8c58 ; _memset + 68 0x00008c54: 78002402 .$.x STRH w2,[x0],#2 0x00008c58: 36000041 A..6 TBZ w1,#0,0x8c60 ; _memset + 76 0x00008c5c: 39000002 ...9 STRB w2,[x0,#0] 0x00008c60: d65f03c0 .._. RET __aeabi_memclr4 __aeabi_memclr8 __rt_memclr_w 0x00008c64: f100103f ?... CMP x1,#4 0x00008c68: 540000a3 ...T B.CC 0x8c7c ; __aeabi_memclr4 + 24 0x00008c6c: d1001021 !... SUB x1,x1,#4 0x00008c70: f1000c3f ?... CMP x1,#3 0x00008c74: b800441f .D.. STR wzr,[x0],#4 0x00008c78: 54ffffa8 ...T B.HI 0x8c6c ; __aeabi_memclr4 + 8 0x00008c7c: 37080061 a..7 TBNZ w1,#1,0x8c88 ; __aeabi_memclr4 + 36 0x00008c80: 37000081 ...7 TBNZ w1,#0,0x8c90 ; __aeabi_memclr4 + 44 0x00008c84: d65f03c0 .._. RET 0x00008c88: 7800241f .$.x STRH wzr,[x0],#2 0x00008c8c: 3607ffc1 ...6 TBZ w1,#0,0x8c84 ; __aeabi_memclr4 + 32 0x00008c90: 3900001f ...9 STRB wzr,[x0,#0] 0x00008c94: d65f03c0 .._. RET _memset_w 0x00008c98: f100103f ?... CMP x1,#4 0x00008c9c: 540000a3 ...T B.CC 0x8cb0 ; _memset_w + 24 0x00008ca0: d1001021 !... SUB x1,x1,#4 0x00008ca4: f1000c3f ?... CMP x1,#3 0x00008ca8: b8004402 .D.. STR w2,[x0],#4 0x00008cac: 54ffffa8 ...T B.HI 0x8ca0 ; _memset_w + 8 0x00008cb0: 37080061 a..7 TBNZ w1,#1,0x8cbc ; _memset_w + 36 0x00008cb4: 37000081 ...7 TBNZ w1,#0,0x8cc4 ; _memset_w + 44 0x00008cb8: d65f03c0 .._. RET 0x00008cbc: 78002402 .$.x STRH w2,[x0],#2 0x00008cc0: 3607ffc1 ...6 TBZ w1,#0,0x8cb8 ; _memset_w + 32 0x00008cc4: 39000002 ...9 STRB w2,[x0,#0] 0x00008cc8: d65f03c0 .._. RET

И что-то я не вижу высоко-оптимизированного кода.

Запись максимум 32-мя битами на 64 битном процессоре, никаких векторных регистров не задействовано...

Это что за шит такой? Даже в бесплатном GCC эта функция юзает регистр NEONа, а здесь даже конь не валялся...

Может, я что-то делаю не так? Или просто библиотеки для ARMv8-A под 64 бита сделаны абы как?

-

В 05.09.2022 в 14:56, aaarrr сказал:

Не нужно ничего менять: свой макрос и назвать по-своему.

Так есть же "нормальный" макрос, который создаёт пустой семафор: xSemaphoreCreateBinary()

И в доке по vSemaphoreCreateBinary() указывается:

ЦитатаMutexes and binary semaphores that were created using the old vSemaphoreCreateBinary() macro, as opposed to the preferred xSemaphoreCreateBinary() function, are both created such that the first call to xSemaphoreTake() on the semaphore or mutex will pass. Note vSemaphoreCreateBinary() is deprecated and must not be used in new applications. Binary semaphores created using the xSemaphoreCreateBinary() function are created ‘empty’, so the semaphore must first be given before the semaphore can be taken (obtained) using a call to xSemaphoreTake().

По крайней мере в 10 версии операционки так.

-

Зачем makefile править, просто в опциях компилятора укажите нужные директории для .h файлов.

-

В 25.08.2022 в 18:34, ovn сказал:

Да, плату не прислали, деньги через 3 месяца вернули. Курсы бесплатные? дайте ссылку.

Тоже от какого-то студента находил ссылку на обменник с примерами, но скачать с китайского обменника не смог.

Держите: https://disk.yandex.ru/d/aNaqbFADXJTT2A

Убрал только часть с AI, она весит 17 гигов

Мне прислали без проблем, вроде всё хорошо, только продавец странный какой-то, совсем не отвечает на сообщения, даже не читает их.

Схема модулей Mercury XU5 (Enclustra) на Zynq Ultrascale

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Приветствую!

Коллеги, если у кого-то вдруг имеется схема или другая документация на модули фирмы Enclustra, в частности Mercury XU5 и материнской платы Mercury+ ST1 - нижайше прошу поделиться.

Мануал их сайт даёт скачать без проблем, но схему нет - запрашивают фирму\адрес\и т.п., а я физ. лицо, не светит мне ничего... :(