ovs_pavel

Свой-

Постов

275 -

Зарегистрирован

-

Посещение

Весь контент ovs_pavel

-

Не совсем ясно, где какой пиксел на сколько умножать.

-

День добрый коллеги. Возник вопрос по преобразованию видео потока (grayscale, 8 бит/пиксель, 25 кадр/сек) на ПЛИС. Исходный формат - 1280х1024. Необходимый формат - 960x768. Я сделал просто и быстро (было задача главное сделать) - убрал каждую 4-ую строку и каждый четвертый пиксель в строке. Все работает и ок, но видны на косых линиях маленькие ступеньки. Поэтому и вопрос - есть ли простые (именно простые) алгоритмы аппроксимации, которые хорошо ложатся на ПЛИС (ну по соседним пикселям высчитывать новые или что-то в этом роде). Можно ссылку на литературу (не занимался видео обработкой даже в таком простом виде, поэтому и сделал все в лоб). Заранее спасибо.

-

ISE 14.2 ФИФО?

ovs_pavel ответил ovs_pavel тема в Среды разработки - обсуждаем САПРы

Если выразится совсем точно, то провел моделирование проекта после его размещения в кристалле (post-place and route). Обычно всегда так и делаю. Результат соответствия с железом 100%. -

ISE 14.2 ФИФО?

ovs_pavel ответил ovs_pavel тема в Среды разработки - обсуждаем САПРы

прогнал на временном анализаторе -

ISE 14.2 ФИФО?

ovs_pavel опубликовал тема в Среды разработки - обсуждаем САПРы

Утро доброе коллеги. Вопрос вообщем следующий. 1. Использую корку fifo generator (ПЛИС Kintex xc7k325t). Тип ФИФО: independent clock, block ram, first word fall-through. Выполняю временной анализ. Смущает то, что данные на выходе ФИФО появляются через 8 тактов частоты чтения. Насколько мне не изменяет память в virtex5 и spartan6 они появлялись на следующий такт от частоты чтения. 2. Решил использовать описание ФИФО из HDL Library Guide, т.е. такого типа: FIFO_DUALCLOCK_MACRO #( .ALMOST_EMPTY_OFFSET (9'h080), // Sets the almost empty threshold .ALMOST_FULL_OFFSET (9'h080), // Sets almost full threshold .DATA_WIDTH (32), // Valid values are 1-72 (37-72 only valid when FIFO_SIZE="36Kb") .DEVICE ("7SERIES"), // Target device: "VIRTEX5", "VIRTEX6", "7SERIES" .FIFO_SIZE ("18Kb"), // Target BRAM: "18Kb" or "36Kb" .FIRST_WORD_FALL_THROUGH ("TRUE") // Sets the FIFO FWFT to "TRUE" or "FALSE" ) FIFO_DUALCLOCK_MACRO_inst ( .ALMOSTEMPTY (), // 1-bit output almost empty .ALMOSTFULL (), // 1-bit output almost full .DO (w_dout), // Output data, width defined by DATA_WIDTH parameter .EMPTY (), // 1-bit output empty .FULL (), // 1-bit output full .RDCOUNT (), // Output read count, width determined by FIFO depth .RDERR (), // 1-bit output read error .WRCOUNT (), // Output write count, width determined by FIFO depth .WRERR (), // 1-bit output write error .DI (din), // Input data, width defined by DATA_WIDTH parameter .RDCLK (rd_clk), // 1-bit input read clock .RDEN (rd_en), // 1-bit input read enable .RST (rst), // 1-bit input reset .WRCLK (wr_clk), // 1-bit input write clock .WREN (wr_en) // 1-bit input write enable ); Данные на выходе ФИФО появляются после 4-го такта от частоты чтения (причем данные поломанные, надо еще разбираться). Что такого сделали с коркой ФИФО, что работать она стала "криво" по времени появления данных? -

Если честно я просто просмотрел их и не делал скрины.

-

От проца как раз все исходит. Т.е. проц выдает все как надо. А Вы процессор P4080 использовали в работе??

-

Последовательность команд на память после сброса следующая: LMR2 -> LMR3 -> LMR1 -> LMR0 -> ZQCL -> NOP -> REF -> ACT -> READ -> ACT -> WRITE -> READ. Используемая память - MT41K512M8RH-125IT:E (но работает в режиме 1,5 В, что допускается стандартом). Из 8-ми м/сх (я уже повторяюсь) отвечает только первая в цепочке, т.е. реагирует на последние команды - READ -> ACT -> WRITE -> READ. На остальных линиях DQ и DQS - тишина. Такое впечатление, что совсем не воспринимаются команды идущие с ЦП. AN4039 как раз и используем, а вот второй документ AN4189 что то на вскидку не помню.

-

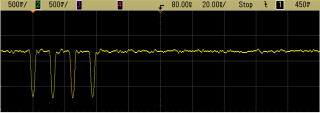

Да. Все тоже. Я на резисторах терминаторах снял диаграммы всех сигналов (AD[15:0], BA[3:0], RAS, CAS, WE, ODT...). Диаграммы все сигналов в норме, т.е. без переколебаний. Вот для примера сигнал CS.

-

Убут не используем (грузим монитором). В убуте, который под фрискейл, идут настройки памяти под DIMM. У меня своя плата, с отдельными м/сх памяти.

-

Сходил на рентген. Все м/сх памяти припаяны хорошо. Память инициализируется с процессора frescale P4080. Мне не понятен момент почему из линейки м/сх (8 штук по архитектуре fly-by) отвечает только одна. На каждую из них приходят одни и те же линии адреса, команд.

-

Еще вот такой интересный момент. После команды ZQCL (ZQ CALIBRATION LONG) последовательно происходит операции чтения - записи - чтения (снял все контрольные сигналы на резисторах (Rtt)). Но отвечает только одна микросхема из 8-ми (в линейке 8 микросхем памяти). Т.е. только одна формирует сигналы DQS и выставляет данные в циклах чтения. А остальные, складывается такое ощущение, не воспринимают команды. Не могут же быть не припаяны оставшиеся 7 микросхем?

-

DDR3. Настройка (+)

ovs_pavel опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Коллеги, настраиваю связку P4080 + DDR3. Топология "fly-by". Линии DQ, DQS, DM - между ЦП и DDR3 - резисторы 15 Ом (согласование). Линии Add, RAS, CAS, WE, ODT, BAdd - согласование в конце линий - 49 Ом. Линия CK - согласование аналогично два резистора 49 Ом + конденсатор. Все длины согласованны в соответствие с рекомендациями. ЦП выдает ошибку автоматической калибровки памяти. Есть ли у кого примеры загрузки значений в 4 рабочих регистра памяти (MR[3:0]), чтобы сравнить со своими значениями? Может в них не так что прописываю? -

Есть ли у кого опыт работы с PowerPC P4080?

ovs_pavel опубликовал тема в Все остальные микроконтроллеры

Не запускается контроллер DDR3 (постоянно висит ошибка ACE - Automatic calibration error), хотя эта автоматическая самая калибровка запрещена в принципе. -

День добрый. Пришлось на время "сесть" на Alter'у. Не подскажите, есть ли возможность создать файл по аналогии с .ucf в Xilinx, т.е. в текстовом виде и где посмотреть его формат. Не очень хочется таскать ножи к графическом редакторе.

-

Уже как часа два назад пришел в УЖОС. Оказались не припаяны ВСЕ ножки м/сх (у меня их несколько на плате). Припаяна была только PPAD. И это на серийном заводе с 5-ой приемкой (я в шоке). Куда смотрели технологи и ОТК я не знаю. Три дня и куча нервов. Про пайку я бы подумал последнее (ну так и оказалось, как начал смотреть на сам корпус под микроскопом). Всем спасибо за советы и участие.

-

Разводка полностью взята с дата шита. Коллеги, а Вы не могли бы рассмотреть что на корпусе у ваших м/сх (если не сложно, просто у меня стопор какой-то). Я использую TPS62080DSGTG4, т.е. корпус DSG (2х2 мм, без выводов). Я его через увеличительное стекло рассмотрел - сверху написано QVR (что соответствует таблице - Adjustable QVR 8-Pin SON TPS62080DSG). Единственное отличие - в дата шите 1-ая ножка маркируется как заштрихованный квадрат (стр. 25), а у меня на м/сх - точка. Я понимаю что это уже шаманство, но все-таки.

-

Все как на схеме (раньше EN был на корпусе через резистор и включался логикой; теперь отключил от логики и тупо подтянул к питанию). От нагрузки отключил вообще, т.е. голый макет. Тут вопрос - а если перегрели, то должно хоть что-то КЗ выдавать, он же по выходу показывает сопротивление десятки кОм. Вроде как и не горелый.

-

Всем привет. Коллеги, сломал уже голову (и не один, а ближайшие коллеги в КБ). Не могу запустить этот преобразователь ни при каких обстоятельствах. Не могу понять в чем причина. Схема согласно рисунку (Figure 34. 1.2V Output Voltage Application) даташита. Отличие - управление сигналов EN (но уже привел ее к рисунку, т.е. подал на сигнал En питание). Просто никак не запускается. Кто сталкивался с этим, для меня уже монстром, подскажите. Может тупо не рабочие м/сх.

-

Они нам не мешали. Пришла распорядка сверху (рособоронэкспорт) перевести все изделия (БРЛС на 35-ый, Т-50 и т.д.) на отечественные или комплектующие стран, не входящих в блок НАТО.

-

Интересует информация про высокоскоростные АЦП разработки Китая (идет волна по импортозамещению ну и замещаем LT2208). Вот такая печаль.

-

Вы знаете, я так думаю это не настраиваемые модули, т.е. необходимо выполнить рекомендации по подключению (согласование с помощью C, L) и все должно быть ОК. Ну посмотрим. Меня больше волнует вопрос по поводу изготовления. Раньше о такой организации (БУТИС) не слышал. И заявить одно, а организовать производство - это другое. Вообщем буду звонить и узнавать.

-

Спасибо. Нашел вот такие: http://butis-m.ru/wp-content/uploads/2014/07/FS-84B27.pdf и наш аналог (или что-то вроде того) http://butis-m.ru/wp-content/uploads/2014/07/smd133x65.pdf Полностью меня устраивает. Буду пробовать их достать.

-

У нас сейчас идет этап ОКР, поэтому потребность небольшая, конкретно 2 шт. (на две платы).

-

Я нашел импортные, а именно - AM84S573 (84 MHz IF Saw Filter 26 MHz Bandwidth; фирма ANATECH ELECTRONICS) и 813-IF84.0M-26A (84.0 MHz IF SAW Filter 26.2 MHz Bandwidth; фирма Oscilent Corporation). Видимо клоны друг друга. Но как их заказать непонятно. На efind.ru их никто не поставляет. Они конечно не совсем подходят (температура от 0 град), но на макет подошли бы.