-

Постов

10 908 -

Зарегистрирован

-

Посещение

-

Победитель дней

31

Сообщения, опубликованные Сергей Борщ

-

-

5 минут назад, Salamander сказал:

А угольный электрод зачем? Для ограничения тока?

Яндекс в помощь. Одну ссылку я для вас нашел, вы, судя по всему, просмотреть ее не удосужились.

-

Если вы обожмете оба проводника одинаковыми гильзами (из одинакового материала) - можно.

-

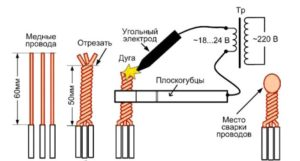

Сварка. Почти в каждой книге для начинающих радиолюбителей прошлого века описывался аппарат для сварки проводов из утюга и угольного электрода от батарейки.

http://electry.ru/elektromontazhnye-raboty/soedinenie-provodov-metodom-svarki.html

-

А что требуется потом от сигнала на выходе? Будет измерятся амплитуда импульсов или достаточно информации о его фронтах? Если амплитуда не интересует, я бы R13 подключил к катоду D21, а сигнал с анода подал через конденсатор на R15-R14.

-

-

-

1 час назад, Relaned сказал:

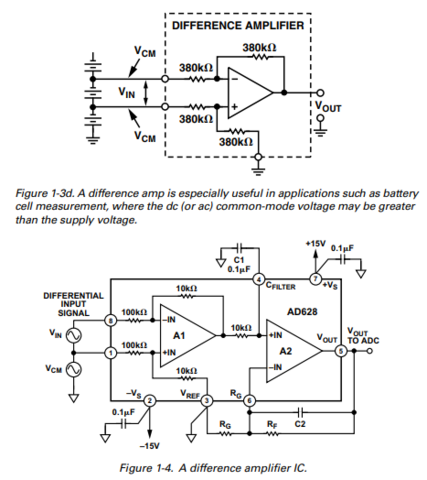

тогда я прихожу к выводу, что ОУ в принципе мне не подходят, для измерения на положительно полюсе

Ну не совсем так. Просто там часто схема на нескольких ОУ и, как заметил stells, резисторы с лазерной подгонкой расположенные на одной подложке для уменьшения температурных дрейфов.

-

1 час назад, srf55 сказал:

Может кто-нибудь, у кого есть установленный линукс и Quartus, попробует собрать этот проект?

Под линухом он собирается "из коробки":

Спойлер$git clone https://github.com/alexforencich/verilog-ethernet.git yyy Cloning into 'yyy'... remote: Enumerating objects: 13523, done. remote: Counting objects: 100% (1034/1034), done. remote: Compressing objects: 100% (396/396), done. remote: Total 13523 (delta 530), reused 988 (delta 506), pack-reused 12489 Receiving objects: 100% (13523/13523), 5.01 MiB | 7.17 MiB/s, done. Resolving deltas: 100% (9670/9670), done. $cd yyy/verilog-ethernet/example/DE2-115/fpga $make [.........] Info: Command: quartus_asm fpga Info (115031): Writing out detailed assembly data for power analysis Info (115030): Assembler is generating device programming files Info: Quartus Prime Assembler was successful. 0 errors, 0 warnings Info: Peak virtual memory: 826 megabytes Info: Processing ended: Tue Jun 13 12:52:42 2023 Info: Elapsed time: 00:00:04 Info: Total CPU time (on all processors): 00:00:04 mkdir -p rev EXT=sof; COUNT=100; \ while [ -e rev/fpga_rev$COUNT.$EXT ]; \ do let COUNT=COUNT+1; done; \ cp fpga.$EXT rev/fpga_rev$COUNT.$EXT; \ echo "Output: rev/fpga_rev$COUNT.$EXT"; Output: rev/fpga_rev100.sof make[1]: Leaving directory '/home/username/projects/yyy/verilog-ethernet/example/DE2-115/fpga/fpga' $cd ../../../../.. && rm -rf yyy-

1

1

-

-

3 часа назад, esaulenka сказал:

Возможно, в этом была ваша проблема.

Возможно. Последняя виндовс, на которой я полноценно работал, была XP.

-

Внутрисхемный отладчик (ST-Link/Jlink) есть? Можете им прочитать значения нужных GPIOx->MODER, GPIOx->AFR, GPIOx->OTYPER (а вдруг?) и регистров таймера? Убедиться, что их значения соответствуют ожидаемым, что значение TIMx->CNT меняется, если программу запустить и снова остановить.

-

25 минут назад, quark сказал:

Стандартного режима 9N1 не существует. Он физически не поддерживается контроллерами.

Он физически поддерживается контроллерами. То, что он не поддерживался микросхемой 16550 в IBM PC XT - на стандарт не тянет.

-

4 минуты назад, srf55 сказал:

Как выполнение makefile может зависеть от операционной системы?

Не знаю, появились ли symlinkи в виндовсах после 7, но на 7 и раньше проект, содержащий symlinkи в исходниках нуждался в копировании файлов.

-

19 минут назад, VaTiKaNeTs сказал:

но я пока не хочу сдвигать всю прошивку на 8 байт, и править стартовый адрес в линкере

Скрипт компоновщика - такой же полноправный член проекта, как и любой другой файл с исходным кодом. Не нужно бояться его править.

Ну вот положили вы размер прошивки и саму контрольную сумму куда-то в конец флеши, а дальше что? Вы потеряли одно очень удобное свойство циклической контрольной суммы - добавленная в конец блока данных она дает результирующую сумму равную нулю. То есть вам не нужно откуда-то дополнительно вычитывать ее, что-то сравнивать - просто обсчитываете блок данных с учетом размера этой контрольной суммы и проверяете результат на ноль. Положили вы размер прошивки тоже отдельно рядом с контрольной суммой - а вы не хотите его тоже защитить этой же контрольной суммой? Значит он должен лежать где-то вместе с прошивкой, в фиксированном месте (наиболее удобно - сразу после векторов, как показал dimka76).

Есть и другие недостатки размещения контрольной суммы отдельно. Вы можете или по совету опытных товарищей сделать сразу хорошо или все эти недостатки обнаружить самостоятельно

-

12 минут назад, Сергей Борщ сказал:

либо считается через рассеиваемую мощность.

Имеется ввиду, что если для одного выхода дают +-35, то это совсем не означает, что через 8 можно снять 35*8 = 280 мА. К сожалению, этот производитель указывает только максимальную мощность для корпуса, но не дает графиков падения напряжения на выходном ключе в зависимости от тока нагрузки, так что придется их измерить на живой микросхеме.

-

3 минуты назад, Turgenev сказал:

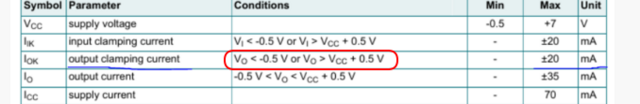

Не написано же общий этот максимальный ток или для 1 канала

Это ток через один вывод. Общий ток указывается для выводов питания и земли либо считается через рассеиваемую мощность.

-

1

1

-

1

1

-

-

17 минут назад, Turgenev сказал:

А как понять сколько максимум может выдать этот буфер на пин?

Так следующая же строчка. +-35 мА

17 минут назад, Turgenev сказал:И на все пины, если они будут включены разом

Считайте через выделяемую мощность.

-

6 минут назад, Turgenev сказал:

Установлен.

Да, туплю.

-

16 минут назад, Turgenev сказал:

мне не понятно для чего приводят максимальный ток- для одного выхода или для всех сразу.

Мне кажется, вы не поняли что это за параметр. Это не выходной ток, это максимальный ток через защитные диоды (clamping current) на выходах, то есть когда вы снаружи пытаетесь тянуть выход ниже земли или выше питания.

А 3.3 мА STM выдаст сам, тут HardEgor абсолютно прав

-

8 минут назад, Turgenev сказал:

У нее на этот счет другое мнение.

Чудес не бывает. На вашем левом розовом снимке экрана не установлен бит SPIEN. Если вы зашили его в такое состояние - поздравляю, ищите параллельный высоковольтный программатор. И никакие пляски с внешним тактированием тут не помогут.

-

2 минуты назад, Turgenev сказал:

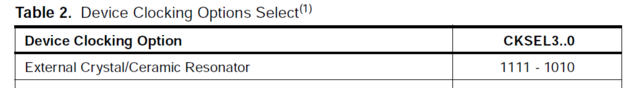

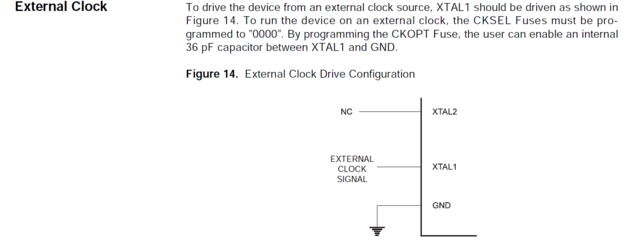

Там речь про CKSEL=0000, у меня CKSEL=1111.

В этом случае она должна работать и программироваться с кварцем без всяких дополнительных источников импульсов снаружи.

Внешнее тактирование требуется подавать только тогда, когда из-за неправильного понимания, что же означает установленная галочка - ноль или один, вместо 1111 записывают 0000.

Во всех остальных случаях оно не нужно.

-

-

26 минут назад, borodach сказал:

чё по деньгам?

Про деньги есть другой раздел форума - "предлагаю работу". Если автор темы хочет предложить деньги - пусть нажмет кнопку "жалоба" на своем сообщении и попросит перенести тему в тот раздел.

-

12 минут назад, adnega сказал:

Важно по ошибке порт закрыть, а затем открыть.

Важно успеть это сделать до того момента, как устройство определится снова. В противном случае (если память не изменяет) ему будет присвоен другой номер COM-порта.

-

9 минут назад, _pv сказал:

ам ещё есть режим так же автоматически щёлкать полярностью возбуждающих токов,

Весь предыдущий абзац перед отцитированным вами именно об этом режиме и написан. "AC excitation mode" = "режим возбуждения переменным током".

Подключение USB 3.0 FT601

в Пайка и монтаж

Опубликовано · Пожаловаться

Попробуйте также для проверки снять VD3. У него в документации сказано, что он предназначен для USB2.0, про USB3.0 не сказано ничего, а скорости там выше... Я с USB3.0 использовал SP3012, у него в документации упомянут USB3.0 и емкость в 6 раз ниже вашего.