liloukan

Участник-

Постов

23 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о liloukan

-

Звание

Участник

-

Спасибо, так и сделаю.

-

Извините, может не в тему: у меня есть проект Linux + QtGui на mips32. Для оптимизации по размеру пересобрал toolchain(gcc 4.3.6 + binutils 2.17 + eglibc-2.8) и SDK с опцией -fno-exceptions незначительно уменьшился размер libstdc++. Как по умолчанию сделать, чтобы new был std::nothrow? Toolchain не из buildroot, а самосборный с поддержкой --sysroot.

-

Вопрос снимаю))) Перепутал RxD1 с TxD11))

-

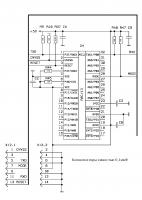

Помогите кто может! В режиме программирования (mode1 - синхронный последовательный режим без кварцевого резонатора) контроллер не входит в режим программирования. Всё делаю вот так: 1. Устанавливаю все пины RESET, MODE, CNVSS, RXD в "0". TXD - вход 2. Подаю на плату питание. 3. RESET перевожу в "1". 4. Жду 50 мс, делаю MODE как вход, а CNVSS устанавливаю в 1. 5. Жду когда MODE станет "0", но там всё время "1". Схема платы. PS: Свой программатор требуется для того, чтобы производить калибровку и зашивать в контроллер вместе с программой калибровочные значения.

-

Спасибо за информацию!

-

Программирование Renesas R8C/13

liloukan опубликовал тема в Все остальные микроконтроллеры

Приобрел Starter Kit Renesas r8c/13. В комплекте есть эмулятор, с помощью которого и программируется данный микроконтроллер. Но при промышленном изготовлении устройства на базе данного контроллера слишком накладно иметь несколько эмуляторов(программаторов), а хотелось бы использовать простой однобаксовый шнурок(как обычно). Пытался найти описание протокола и интерфейса программирования, но кроме схем соединения данных контроллеров с фирменными программаторами так ничего и не нашел. Может кто сталкивался с данной проблемой или знает как её решить? Или у кого есть opensource программатор для данного контроллера? -

Программатор FlashBlaster2

liloukan ответил Voloshchenko тема в MCS51

Порылся в нете, нашел Linux программатор для силабсов по C2 интерфейсу (всего 1 микруха)! линк h**p://www.ise.pw.edu.pl/~wzab/cygnal/index.html -

Программатор FlashBlaster2

liloukan ответил Voloshchenko тема в MCS51

Роботаю в Linux, поэтому интересует один вопрос: Есть ли у кого под данный девайс программа для Linux? Если нет, то может кто-нибудь поделиться инфой по C2 интерфейсу.:) -

Почему? Серия XC9572XL (Питание 3В) при 50 Мгц потребление 50мА .

-

Алгорит извлечения (Рота)

liloukan опубликовал тема в Документация

Столкнулся с задачей минимизации 24 функций из 10 переменных. Нужна дока по алгоритму (подойдет метода по АИЛОВТ БГУИР 2-ой курс КСИС ) чтобы реализовать в программе. -

Вывод: 1. Хотим получить стабильно работающую систему - используем синхронную логику(что я люблю делать). 2. Если старая плата на логических элементах (не, 2и-не, 3и-не) работает в асинхронном режиме, то нечего мудрить ставим CPLD и все работает как и работало, но с меньшим потреблением энергии и меньшими размерами платы в раз 20. Спасибо!

-

Интересует вопрос такого плана: При использовании синхронной логики обычно входной сигнал поступал на информационный вход тригера, который сохранял этот сигнал по клоку. А при отсутствии синхросигнала и не использования триггеров возможна ли стабильная работа схемы?

-

Ассинхронная логика

liloukan опубликовал тема в Работаем с ПЛИС, области применения, выбор

Имеется кучка логических микросхем на плате. Работают как дешифратор. Как заменить их на CPLD XC9500XL если нет клока. Возможна ли работа микросхемы как комбинационной схемы без тригеров в асинхронном режиме? -

Какой симулятор использовать

liloukan опубликовал тема в Среды разработки - обсуждаем САПРы

На VHDL сделал суматор с переменным числом слагаемых. Параметры задаются через generic map. Синтез проходит на УРА! при всех значенияях, но симуляция в ModelSime 5.7(из WebPack 6.3) выбрасывает ошибку. По моему в моделсиме не полностью реализован оператор for ___ generate. Что посоветуете? По другому описать данный компонент? Другой симулятор? library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity conveyer is generic (WIDTH : natural:= 4; INPORTS : natural:=6); port ( CLK : in std_logic; DATA_IN : in std_logic_vector(WIDTH*INPORTS - 1 downto 0); DATA_EN : in std_logic; DATA_OUT : out std_logic_vector(WIDTH - 1 downto 0)); end conveyer; architecture Behavioral of conveyer is function getst (INPORTS : in natural) return natural is variable st : natural; begin st := 0; while 2**st < INPORTS loop st := st + 1; end loop; return st; end; constant CONN : natural := getst(INPORTS); type ar is array (1 to 2**(CONN+1) - 1) of std_logic_vector(WIDTH - 1 downto 0); signal data:ar; begin ge1: for i in 1 to CONN generate process(CLK) variable num: natural; begin if rising_edge(CLK) then if DATA_EN = '1' then num := 0; cl1: for j in 1 to 2**(i - 1) loop data(2**(i-1)+(j-1)) <= data(2**i+num)+data(2**i+num+1); num := num + 2; end loop; end if; end if; end process; end generate; gen2: for i in 1 to 2**CONN generate data(2**CONN + i - 1) <= DATA_IN(i*WIDTH - 1 downto (i-1)*WIDTH) when i < (INPORTS + 1) else (others=>'0'); end generate; DATA_OUT <= data(1); end Behavioral; -

Интересует вопрос синхронизации NCO, точнее, по какому алгоритму производить выделение ошибки синхронизации с несущей (чтобы меньше ресурсов потребовалось)???