kan35

Участник-

Постов

649 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент kan35

-

Application Jump ch32v003

kan35 ответил Alexandr27 тема в RISC-V

Такой код если? asm volatile( "la ra, 0x80001800\n\t" "jalr ra" ); -

Вас не понять, то Вы собираетесь менять пластик на STM, то говорите про 5ю приемку, я запутался, извините.

-

Не знаю, где Вы металлокерамику видите. Обычный пластик, такой же как у STM, посмотрите на правую часть таблицы, там корпуса обозначены.

-

У Микрона довольно неплохой набор LDO и DCDC https://mikron.ru/products/chip-power-management/ldo-voltage-regulators/

-

Микрон проводит публичный технический практикум на МК Амур. Участие - бесплатное. 2 города - Новосибирск и Екатеринбург. https://www.mcu.mikron.ru/technical-training

-

2 миллиона микроконтроллеров на два года это слёзы. Не знаю получится ли у микрона столько хотя бы изготовить, но рынок заберет их легко, не говоря уже про балльные проекты.

-

А Вы нам и не нужны уже! Мы же тут плодотворно общаемся))) (шучу, конечно же)

-

itoa - тоже можно, только вот прелесть библиотек в том, чтобы взять что-то хорошо сделанное и использовать его для своего блага, а itoa можно и свой написать за 5 минут. Как вариант - есть еще от coremark printf (а может они сами его где-то позаимствовали), с опциональной поддержкой плавающей точки. Он тоже единицы кБ занимает. https://github.com/eembc/coremark/tree/main/barebones

-

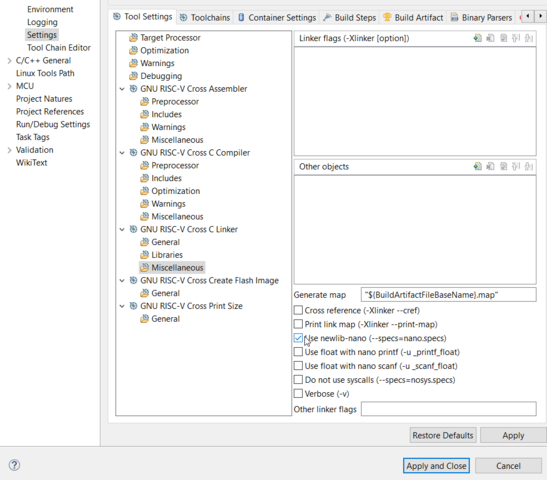

Чтобы вручную не переключать --specs=nano.specs, полнота выбирается в свойствах линкера. Там же включается поддержка плавающей точки.

-

Я там выше писал, компилятор - С18, для pic18. ANSI 89. И спасибо всем за комментарии

-

Регистр объявлен так: extern volatile far unsigned char RCREG4; не хотелось бы делать { тип i = RCREG4; } (у меня на самом деле оно примерно так и есть) Хочу, чтобы переменная в стеке не появлялась совсем. Просто поясню зачем мне это нужно: сейчас занялся высвобождением памяти, контролируя глубину стеков всех задач, таким образом, спасая один байт в обработчике прерываний я могу убавить стеки в 6ти задачах на 1, то есть по сути высвободится 6 байт. у меня такая мысль тоже была, но есть нюанс - в какой регистр свободен в этот момент... Я конечно применяю, совсем простые инструкции, типа: void vApplicationIdleHook( void ) { _asm sleep _endasm } А вот с регистрами уже просадка... плохо понимаю архитекктуру выходного кода, да и архитектуру процессора тоже плохо осознаю 🙂

-

Заменил unsigned char byte; byte = RCREG4; byte = RCREG4; byte = RCREG4; на (void)RCREG4; (void)RCREG4; (void)RCREG4; и по результату работы кода вижу, что он уже не делает вычитку из регистра. Компилятор C18 к сожалению не знаю как можно посмотреть дизассемблер этого куска кода... Есть ли еще что-нибудь более жестко регламентирующее, чтобы он не удалял эти строки из работы?

-

Благодарю, господа!

-

Как в Си считать регистр процессора "в никуда"?

kan35 опубликовал тема в Программирование

Доброго дня всем! Пробую уменьшить расход стеков, компилятор у меня с очень низкими возможностями оптимизации, потому вот такой вопрос: Нужно считать несколько раз регистр, но само значение не нужно. Сейчас я завожу переменную и читаю в неё. unsigned char byte; byte = RCREG4; byte = RCREG4; byte = RCREG4; Но это же бессмысленно, как записать в Си чтение в никуда? Спасибо всем. -

Всем доброго дня, Есть подозрение на недостаточность стека в определенных случаях. Попытался использовать функцию uxTaskGetStackHighWaterMark. Из описания https://www.freertos.org/uxTaskGetStackHighWaterMark.html следует, что нужно лишь определить INCLUDE_uxTaskGetStackHighWaterMark -> 1 Правильно ли я понимаю, что он заполняет стек определенным числом и потом вычитывает и смотрит на сколько он залез на шаблон?

-

Наверное в этом есть смысл при работе кода из внешней памяти, на сколько я понимаю в ESP flash висит как раз на SPI. При памяти на кристалле - 1мс это совершенно не нагрузка. Например, на самом утлом PIC18 - 12000 циклов между тиками при 1мс. Получается расход на обслуживание ОСРВ наверное будет - 1-10%, вполне приемлемо. Лично мне просто 1мс привычно, оно и в Windows 1мс кстати, в общем устоялось так.

-

Вот так "легким движением руки" процессор 144МГц, с TCM и L1 кэш памятью, FPU и TZ затесался у нас между CM0 и CM3. Вам нельзя работать в присяжных с вашей объективностью 🙂

-

Ну опять 25, BL702 имеет ядро близкое к CM4-7. Вы подбираете варианты, чтобы высказать негатив? Coremark Вам тоже не Вам авторитет... странное отношение к синтетическим тестам, вы же можете открыть исходники и увидеть что там за попугаи, и прочитать описание почему выбраны именно такие вычисления, с обоснованиями Эллиптические кривые - было бы интересно попробовать. Но задача, я бы сказал - специфическая, чтобы из результатов делать широкие выводы. Я кстати, недавно делал подсчет MD5 (где есть 64 битные аккумуляторы) на PIC18, вот там я мечтал об Амуре. Так что всё относительно 😉 Позволю выразить такое мнение: если бы Микрон начал массово выпускать продукты близкие по функционалу AVR или PIC18, то мы уже приобрели бы значительный технологический суверенитет. А производительности Амура достаточно для 99% задач для этого класса микроконтроллеров. Даже 16кБ ОЗУ это достойный объем.

-

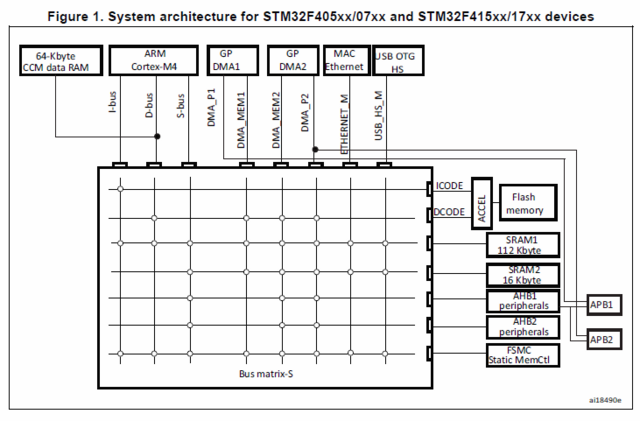

Не совсем так, матрица шин, хоть и работает на частоте ядра, но она делится между многими мастерами, например DMA, у которого есть пачковый burst доступ, плюс время на захват шины и будет процессор M7 сидеть без данных или без кода многие десятки циклов. Только не говорите "а можно не использовать DMA" 🙂 , но кстати за счет деления SRAM банки в STM32 - там можно распределить нагрузку на матрицу шин, но все же . В общем и целом у CM0-CM4 всё те же слабые точки, что и у других архитектур того же уровня интеграции. Кстати, TCM на некоторых контроллерах может быть использована для кода тоже. Конечно же лучше, когда кэш находится и в самом процессоре. Ну и опять мы внезапно пришли к сравнению SCR1 с CM7... Все таки, более честно будет сравнивать с СM0 или хотя бы с СM3, так как у SCR1 есть аппаратное умножение, но точно не с CM7.

-

Согласен на счет ширины шины между кэш и память, этого я не учел. Но какая эффективность у этого решения на реальных задачах - нужно хотя бы уметь оценить (так как ширину этой шины нельзя регулировать как правило - понять пользу от нее на реальных приложениях будет не так то просто - лучше на %% или в разы). У STM32 кэш так же находится за шинной матрицей, поэтому ваша претензия не обоснована. И опять же - есть предварительные замеры производительности: https://wiki.mik32.ru/CoreMark_Test и по этим данным кэш QSPI достаточно эффективен на задачах, близких к реальным. И немного лирики. Я встречался со случаями, когда производительности 500МГц не хватало для автосигнализации и разработчик требовал 1ГГц минимум, начинали разбираться в чем дело - машина состояний - он по очереди опрашивает разные датчики и у него всё по микросекундам уже. Говорю - применяй RTOS и будет тебе достаточно 10МГц, в ответ - "нет, мы боимся, мы не умеем, мы не хотим, дайте 1ГГц".

-

Амур работает на 32МГц, при этом QSPI - на 16МГц, соотвественно, требуется 64мб/с, а есть 8, но хорошая новость в том, что кэш таки есть, он не в процессоре, а не блоке QSPI, его объем составляет 1кБ. Кстати, на STM32 флэш весьма медленная, около 30МГц, соответственно какой-нибудь STM32F4 на 180МГц будет иметь 6 циклов ожидания, а ведь у него ART акселератор - тот же кэш - составляет тот же 1кБ. Но считается, что флэш на нем не сильно его тормозит. А ведь это почти как в Амуре по количеству циклов ожидания. Хотя на QSPI еще и команды, протокол передачи... тут нужно просто замерять на самом деле. На счет TCM памяти - это память, которая не имеет задержек доступа из за загрузки матрицы шин, для сигнальных вычислений или чего то максимально реалтаймового. Но минус - не доступна для DMA.

-

Ну чисто технически Амур может работать, например, в трекере для транспорта, тот же Платон или тахограф или эра. А экономически - там, где заказчик готов немного доплатить за локализацию. С sip нет проблем, это чистая косметика. У нас это делают и довольно уже давно. Но по честному - многим ли не хватит места на плате под 8 выводный соик? Смарт часы или мобильники у нас что-ли производят?? Так зачем лишаться гибкости, мне нравится внешняя память. Кому то хватит и 512кб, а кому-то нужно 16мб или более.

-

Цена на Амур будет разумеется выше, чем на wch сравнимого уровня. флэш технологии в России нет, поэтому память только внешняя, или sip В нашем случае, даже если бы была флэш, то наделать зоопарк контроллеров от 8кб до 4мб не представляется реалистичным в короткие сроки, поэтому внешняя флэш - решение даже скорее логичное 8 выводная микросхема за 50центов (8мб) не сильно ударит по карману, тем более сам контроллер дорогой настолько, что его обвязка это прямо скажем - статистическая погрешность по затратам И я уверен, что контроллер потенциально зайдет много куда, но меня две вещи беспокоят - получится ли снизить цену хотя бы рублей до 200 и будет ли стабильным качество… ну и еще вопрос конечно - сможет ли Микрон нашлепать миллионы Амуров в год…

-

ну и замечательно, Но могли спокойно продолжать делать и кортексы, кто бы им запретил. Типа ARM подаст в суд😃? Для информации - Миландр под санкциями США и ЕС, скорее всего навсегда. И чего им бояться - страшнее чем это с ними уже ничего не случится, кмк. И все же почему делают ставку на RISC-V - ну очень просто, многие у нас в стране мечтают, что все вернется как прежде, что будем опять пить кокаколу и ездить на шкодах, и мы типа - хоба - ничьи авторские права не нарушаем, и метрополия нами довольна.

-

RISC-V на начальном уровне (а мы работаем в основном на маленьких одноядерных контроллерах) это аналог Кортекса, и кому какая разница как там пишутся ассемблерные инструкции - да плевать 99%м людей, так как пишут все на Си. И кстати, советую открыть два референс мануала и посравнивать CH32V103 и CH32F103, увидите как меняются ядра RISC_V и CM - легко! не до конца понимаю ваши тревоги на счет патентообладателей 🙂 Вон Миландр делает кортексы и не жужжит, и что... да ничего. Я понимаю, что Вы не будете ничего сравнивать, да и не понятно с чем именно сравнивать и по каким параметрам? Количество портов или памяти или что...

.thumb.png.2e43c376c71924ee24c8ccdb3db8e581.png)