javalenok

Участник-

Постов

290 -

Зарегистрирован

-

Посещение

Весь контент javalenok

-

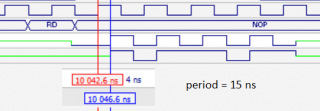

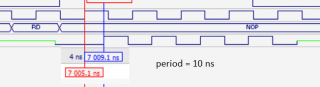

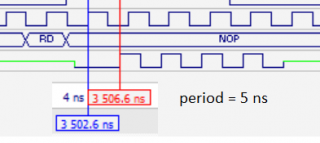

У меня на 200 МГц нормально работает, даже без DLL (хотя с ДЛЛ на 20% окно валидности шире). Просто откалибровал его положение (три отдельных домена - сперва отдельно чтение, адрес с командами, потом запись) и самплю в наилучший момент. Никаких стробов на приём действительно не нужно. Зачем они предлагают читать по DQS во всех своих аппнотах? Вот например знаменитый PLB Double Data Rate (DDR) Synchronous DRAM (SDRAM) Controller. И стробы и внешняя ОС для клока. Я где не срашивал, мне везде отвечали "это важно использовать чтобы meet timing". Никто похоже не знает. С VHDL действительно проблема в двустороннюю линию задержку ввести. Просимулировать удалось переключением напарвлений сперва прослушиванием команды (чтение или запись), а затем автоматически, при помощи такого вот хитроумного коммутатора, который направление сам определяет. Во время z-состояния на линии смотрит куда ветер подует, в том направлении и берётся ретранслировать с задержкой, пока источник не утихнет. Это работает поскольку любое переключение направления должно сопровождаться перерывом, когда оба драйвера молчат.

-

А я грешным делом думал что модели от производителей нужны чтобы мы могли подкручивать СВОИ до состояния коммуникации с ними. Подождите. Для схватывания DQ по DQS нужна 1.25 ns задержка на DQS. Какое отношение к этому имеют клоки? В FIFO данные направлять, продолжая использовать DQS как тактовый? Восьми штук (для DIMM больше не надо) хватит?

-

Спасибо.

-

Ковырять недостоверную модель чтобы узнать как на самом деле? Я тоже решил это сделать. Но для платы (XUPV2p) у меня модели нету. Не понял чего конкретно не осилили вы, но я задержики в 3-state шину. Проблема ещё что память оказывается имеет ограничение снизу на скорость. Нельзя слишком медленно запустить, а потом ускроять. Как раз из-за того видимо что она не после CL откликается, а через 4 ns на такт раньше. А вы как данные ловили - по DQS? Я слышал что до 100 МГц работает простой клок.

-

(источник) Из картинки вроде бы понятно что CS никуда не декодируются. Но что с клоками? Зачем их три штуки? Там же объяснение больше похоже на кусок спецификации DDR SDRAM. Этим производители чипов занимаются. На каждом чипе один клок. Как вы три дим клока подключаете к чипам, гады?

-

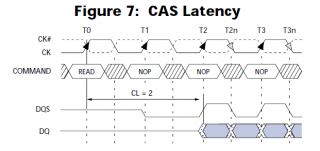

Я взял модель DDR400 у самсунг. Она восприняла мой write правильно. На всех частотах. Я вижу что и данные в read выходят правильные вместе с DQS. Однако когдА они выходят! Я ожидаю что-то вроде этого После периода RD, идёт низкий строб. Это два периода. После них, вместе с появлением данных, строб начинает повторять clock. Видите? У меня тоже CL=2. Однако в симуляции строб опережает свой такт Вместо периода ожидания через 4 ns после RD начинается вывод данных. Период ожидания начинается не после того как мы клокнем команду RD передним фронтом, а более чем за пол такта до того. Как работать с такой фигнёй? Тут даже частоту не снизишь!? PS! Когда всюду и у них в модели я вижу что DQS не должен убегать от CLK: `define tAC 0.7 // Output data access time from CK/CKB (min:-0.7, max:+0.7) Модель показывает 4 ns спереди и соотв-но 6 ns сзади. Они сами в своей модели не исполняют спецификации!

-

В SDRAM есть CKE и /CS. По-сути - два разнополярных CS. Поэтому покуда все выходы одинаковые SDRAM откликаться не будет! Нужно в нужный момент включить CKE, затем отключить /CS и CKE. После чего удерживать все выходы FPGA на одном уровне. Так? Правда они зачем-то предлагают 3-стейтить выходы на время переконфигурации и мужественно подавлять возникающие глюки, напоминая там же что с HSWAPEN глюков не происходит? Ну не сумасшедшие ли? Но главное что у меня на плате HSWAPEN TRI-state'ит выводы. Связи с SDRAM, по стандарту терминирования, притягиваются в среднее между 0 и 1. А по сему хотелось бы чтобы безглючность достигалась за счёт способа реконфигурации. Вот такая информация The Virtex II provides glitchless configuration logic, meaning if a bit stays the same between two configurations no glitch will occur. или Figure 3 shows how the physical design has been partitioned. In this design bus macros are not used since there is no communication between the logic that makes up the embedded Linux system and the filters that are reconfigured. However there is communication between the main Linux system on the right hand side and the Ethernet and SystemAce peripherals on the left hand side via an OPB bus. The DSP filter between these two regions can be reconfigured without disturbing the communication on the OPB bus. This is possible because Virtex 2 [Pro] devices offer glitchless partial reconfiguration. If a configuration bit holds the same value before and after configuration there will be no glitch on the resource that bit controls. Resources to be careful of are SRL16s and LUT Rams because they change dynamically and will be over written when configuration occurs. We worked around this problem by constraining the filters to the top part of the reconfigurable region and allowing only OPB routing (no logic) under the filter region. Создала у меня впечатление, что можно сделать ряд реконфигураций [1] отдельный пин просто переконфигурировать активно и безглючно - установить в константу. [2] перегрузить новым битстримом, где он тоже - константа. [3] какой-нибуть внутренний net, служащий reset-входом дизайна, переконфигурировать 0->1 чтобы дать сигнал сброса новой схеме. [4] ещё одной реконфигурацией переключить выход FPGA с константы на логику нового дизайна [5] последней реконфигурацией reset2 линии 0->1 Я так понимаю что все пункты кроме [2] не должны затрагивать ничего кроме своего сигнала чтобы не получилось так что дело сделано, а окружающая логика ещё конфигурируется. Или это уже совсем параноя? Можно ли так и какими тулзами автоматически в IOB битстриме можно перестроить на констатну? Как быть с остальными ногами на время переконфигурации? Если она активная другие ноги тоже могут дурить. Или не могут если я их ни в каком дизайне не использую или использую как входы?

-

Спасибо, это - ответ. Осталось FPGA-way расследовать. Как удерживать IOB регистр во время перепрошивки и сразу после (пока reset своё дело не сделает)?

-

Какие I/O пулапятся? Я вижу что он только FCS_B и MOSI подтягивает. В "Packaging and Pinout Specification" вообще не говорится про то какие ножки подтягиваются.

-

Я тут почитал - Virtex может дрожать во время перепрошивки. А я хотел бы память, с которой он сопрекасается, держать в self-refresh. Говорят у Xilinx бывает какая-то активная реконфигурация, когда устройство остаётся активным во время реконфигурации. Как этого достичь? Я вижу что Xilinx позволяет управлять состоянием "Unused IOB Pins" во время конфигурации. Что происходит с "Used IOB Pins"?

-

В руководстве Xilinx8 сказано 1. Initial bugeting ngdbuild -modular initial top 2. floorplan, который создаст UCF # Start of Constraints extracted by Floorplanner from the Design INST "M_INST" AREA_GROUP = "AG_M_INST"; AREA_GROUP "AG_M_INST" RANGE = SLICE_X16Y159:SLICE_X27Y0; AREA_GROUP "AG_M_INST" RANGE = TBUF_X16Y159:TBUF_X26Y0; AREA_GROUP "AG_M_INST" RANGE = RAMB16_X1Y1:RAMB16_X1Y18; AREA_GROUP "AG_M_INST" RANGE = MULT18X18_X1Y1:MULT18X18_X1Y18; 3. снова ngdbuild со ссылкой на полученный UCF. Выдаёт всё ту же ошибку: module 'M_INST' is missing an AREA_GROUP property Это потому что я ISE 10 использую?

-

Как DIMMы собираются из SDRAM чипов?

javalenok опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Откопал JEDEC спецификацию. Но всё равно не понятно. Почему банков (clock en и селекта) два, а клоков - три? Как замаплены S0 и S1 на CS-ы: тупо или через декодер, который не позволит выбрать оба ранга одновременно? Почиму об этом нигде не сказано? -

Лолшто?

-

Идея, которую реализует чисто компаратор, без ШИМ! Ему не за науку досталось, а ложную философию с её вызывающим пренебрежением вопроса и уничижением правильных ответов. Пусть сам извиняется.

-

Я тут кажется ещё один аргумент надумал. В случае с полным мостом, когда когда ошибка мала ШИМ держит ключи почти всегда запертыми. При компараторе ключи всегда будут открыты - в одну или другую сторону, вызывая как минимум постоянные транспортные потери (вроде реактивной нагрузки в сети). А зачем вводить гистерезис в обратную связь? Это же аутизм! Управленец должен «держать руку на пульсе»! Да, тогда и с выбором транзисторов затруднения могут наверняка возникнуть - слишком высокая частота для них тоже вредна, насколько я знаю. Ну или эффективность снижает. Однако не очень понятно как это решается ШИМ-ом. Ведь ШИМ всё равно не держит период, т.к. ОС на него влияет мнгновенно: перевалил уровень - пора вырубаться, несмотря на то что период ещё не истёк.

-

А разве дроссель с кондецатором выходного фильтра её не накапливает? Я говорю про ненужность накопления между PFC и усилителем! Убираем усилитель вместе с промежуточным DC фильтром. Остаётся PFC с выходным audio фильтром. Действительно, что нам это общество - у нас своя жизнь! Даёшь гайку на грузила, троллейбусные провода на металлолом!

-

Имеются ввиду сильные заносы, перерегуляция? Открой нам глаза! А пацаны с IR то и не знают! Какие-то аппноты пишут, основы импульсного усиления! Нужно же сперва разобраться - зачем усиление, а потом уже микрухи усилительные выпускать! Потребности ведь у всех разные! Значит выпуск этих универсальных class-D контроллеров - глупость!!! Видимо ориентируются на просточков вроде нас, с нишим «безотносительно к предмету, где используется, при управлении домной, машиной для поньчиков или в звуковом усилите мощности». Учитель! А ты случаем не из этих, не из фолк-филосов? Кому ещё открыт тот «правильный ответ», что «все абстрактные теории бессмысленны потому что каждый случай индивиуален»? Узнать почему механика быстрее электроники было бы занятно. Но ни это, ни АЦП, не имеет отношения к обратной связи, реализуемой посредством резисторного делителя и ОУ. У меня был теоретический вопрос. Кто его понял может добавить.

-

У нас как-то принято сперва выпремлять напряжение потом использовать ещё один идентичный импульсный блок для усиления. Не разумнее ли совмещать - потреблять в соответствии со спецификацией электросетей, а в качестве опорного значения использывать не постоянное ref, а требуемое Uin? То есть сам PFC может работать как усилитель. Так ведь можно и от здоровенных кондецаторов избавиться?

-

Вот например про усилители http://www.irf.com/technical-info/appnotes/an-1071.pdf Чем усиливать и ШИМить ошибку лучше использования простого компаратора, Uin==fb, для управления ключами напрямую?

-

Пройдя курс codesign-a, понял наконец про что этот раздел. И оказалось что имею вопрос по теме. У меня есть VHDL-модель устройства, которое должно общаться с компом по Rs-232. Написал и Java-программу, которая должна этим устройством управлять. Родилась мысль просимулировать систему целиком. Ведь пока не проверишь всё равно ошибки остаются. Хотя бы ототго что так легко порядок бит напутать что в rs232-байте, что в передаваемых словах. В курсе кодизайна встречал описания принципов работы (mixed-language) косимуляторов. Тока такого, чтоб VHDL с Явой соеденил или любой компьютерной программой, я что-то не нащёл. Но ведь в той же книжке пишется, что чаще всего системы разбиваются на PC + HW accelerator!

-

1. Да, я так потом и подумал: подмагниченность должна увеличивать индуктивность и ток растёт медленнее. Не знаю я если честно литературы, которая понятно бы описывала магнитные процессы: разницу между B, M и H полями. 2. "Хорошо" я имел ввиду тут то, что подмагниченность наблюдается как и должна по теории. :)

-

Ага, ток в первом четвертьпериоде ускоряется сильнее, чем тормозиться во втором четвертьпериоде? Подмагниченность это хорошо - ведь я ток только в одном направлении гоняю.

-

Да, у меня тоже 3тау = 1,5 мксек для 100 нКл затвора в расчёте получилось. Ага, думаете, что весь ток в контур уходит? Это интересная мысль. Питание драйвера законденсировано, уверен что номиналом большим чем 100 нф в контуре. теперь меня беспокоит что уменшенное путём уменьшения конденсатора затухание стало меньше нуля - напряжение прыгает выше удвоенного - своего теоретического максимума! Как это объяснить?

-

Во всех экспериментах? Насыщение дросселя -- сверхвысокий ток? Это значит что сопротивление конд-ра выше транз-ра при насыщенном дросселе? Спасибо за идею. Но не хотите ли вы сказать, что это из-за насыщения сердечника (закоротки дросселя) у меня напряжение сверх теоретического максимума обнаружилось?

-

Подозрение на сопротивление источника напряжения интересное, но медленный заряд затвора вызван резистором 85 Ом. Резистор рекомендован изготовителем его драйвера. Индуктивность разную пробывал в диапазоне от 70 мкГн до 8 мГн толстым многожильным проводом - всё одно. Энергоёмкость индуктивности E= I²L/2. 1 мкФ - это электролит. Поменял на другой 10 мкф, вот что получилось: . Напряжение пика ещё уменьшилось видимо из-за большого тока, вызыванного большой ёмкостью. Смена на неэлектролит 1 мкф дало положительный эффект: теперь добивает почти до 27 вольт. Поменял на другой неэлектролит 1,5 мкф тоже даёт 26-27 вольт. Все кондёры куплены пару лет назад. Самое забавное получается если поставить конд-р 100 nF: Полупериодный пик уходит выше удвоенного напряжения!! Можно видеть что в асимптоте - 15 в, а первый пик - целых 35 в!! :07: