Aleksey_Serov

Участник-

Постов

57 -

Зарегистрирован

-

Посещение

Весь контент Aleksey_Serov

-

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Когда я выбирал этот МК, меня не особо интересовала его максимальная тактовая частота - этот я взял чтобы хотя бы начать, ну светодиодом помигать, программу синтезатора перенести (переделать) с avr, так что непринципиально. И да, тему хорошо бы переименовать, думал парой вопросов отделаюсь кину cmsis куда надо и пойдет, а тут такое. Светодиод у меня так и не замигал, хотя программа прошивается и верифицируется, я поставил 8 мгц -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Ладно, от этой пораженки на КВ никуда не деться (хотя не такая уж и проблема), где-то в чипе-и-дипе на сайте восьмибитные с высокой тактовой частотой видел (может там тоже такой же "низкочастотный" кварц), но решил модные stm32 освоить -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Понятно, у меня если по максимуму на будущее это контроллеры для КВ приемников, то есть вход/выход клавиатуры на 74hc595 и выход данных на дисплей и синтезаторы (ну может ПЛИС) ну еще АЦП для измерителя уровня сигнала и заряда батарей. Мне для всего этого хватало ATmega, единственный у них минус был для меня - тактовый генератор пропадает в КВ диапазон, а возможность использовать цветной дисплей - это постольку поскольку - и нокии 48*84 достаточно. За STM32 взялся так, чтобы не были темным лесом для меня, а то они выходят доступнее и дешевле с каждым годом. И не ожидал что там такая куча файлов ми все так взаимосвязанно. Насчет тактового генератора потом буду использовать или кварц с частотой более 30 МГц или готовый генератор -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Спасибо! Работает, хекс тоже есть и программатор его видит и готов прошить. Наверно будет правильным если я сделаю так же самостоятельно. У меня вопрос, те файлы, которые туда включены, они в своем первоначальном виде, или туда все же нужно залазить и править? -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Ну понятно, попробую сейчас -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Еще вопрос - некоторые программы, например ксилинкс неправильно работают, если там где они размещены, то есть в ихнем пути есть пробелы или русские надписи, например Мои документы и все такое. У кейла такого нет случайно? -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

в тексте блокнота не нашел поиском слова stm32f103vct6, как в таком виде так и без хвоста vct6 Я не спорю, я не хакер, но а какой проект не голый? В чем смысл этой фразы. Вот есть в статейке листинг си, я его копировал и вставил, потом включил те файлы на которые жаловался компилятор что их нет, может понавключал лишнего, но вроде сошлись на том ччто дерево проекта теперь ОК. как должен поступить грамотный технарь/микроконтроллерщик в этом случае у которого проект не голый и не наскоком (каким наскоком опять же, как не наскоком) Я без эмоций -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

в файле stm32f10x.h нашел /*#define USE_STDPERIPH_DRIVER*/ это раскомментировать? тип МК это полностью f103 или первая попавшаяся f10x? А если использовать другую программу, cube, например, там проще? так работать по-моему никак, контроллер сжечь можно, в файлы залазить, менять там непойми чего, где-нибудь есть обучалка со всем исправленным, или это индивидуальные особенности каждого установленного кейла и надо так подстраивать? -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Нет, ничего не идет -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Сейчас, галку в output я первым делом добавлял вместо обведенной красным сорс групп я ранее создавал другую группу и указывал ее, тоже без результатов, и еще как папки эту самую созданную я нигде не нашел, хотя отображается как папка -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Ну теперь в дереве проекта все правильно, осталось только допинать кейл чтобы он-таки выдал хекс, знать бы только как -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

вот когда у меня такое окно свойств таргета то кейл пишет коротко (от этого не легче) Build target 'Target 1' FCARM - Output Name not specified, please check 'Options for Target - Utilities' Target not created выделенный синим я трогать не стал. Теперь правильно, или его тоже убрать? Убрал и тот что синим подчеркнул, без изменений. А что это за FCARM, из за него весь shit как я понимаю, может где-то в другом месте галка нужная не убрана или не поставлена? -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

файл 0158.hex (это я так назвал output file) появляется всякий раз как я жму на f7, насчет остального сейчас посмотрю Вот добавил, обведено синим. То что зачеркнуто красным пока не трогал но как я понимаю надо убрать, а файлы стартап на своем месте? -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Пятый. А вообще, вот он создаст хекс, если все пойдет правильно где этот хекс окажется, в какой папке А еще в mаnanage project items можно выбрать ARM или GCC compiler, стоял ARM, на что это влияет, при GCC тоже не может выполнить, но пишет другое Build target 'Target 1' FCARM uses the following Files via command file '.\Auto_FcArm_Cmd.inp': Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_cl.s, Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_hd.s, Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_ld.s, Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_ld_vl.s, Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_md.s, Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_md_vl.s, Includes\STM32_CMSIS\DeviceSupport\ST\STM32F10x\startup\arm\startup_stm32f10x_xl.s TO 0158 NOPRINT custom translating @.\Auto_FcArm_Cmd.inp... Custom: H:\Keil_v5\ARM\Bin\FCARM.exe @.\Auto_FcArm_Cmd.inp FCARM FILE CONVERTER V2.50 Completed 7 File(s), Ratio 100% compiling Test_002.c... --- Error: failed to execute 'arm-none-eabi-gcc' ".\Test_002.elf" - 1 Error(s), 0 Warning(s). Target not created -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Пак 1.0.2 под xp другие не пошли У меня вот что в моем проекте происходит. Он выдает, не знаю уж, то ли это хекс или нет,(например в нкекоторых попытках расширение указываю, он создает хекс на полмегабайта файл) и тут же сам на него в любом случае жалуется -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Там все что нужно включать( stm32f10x_conf.h, например ) уже в папке вашего проекта, или мне свои инклуды-потроха туда закидывать? пишет Build target 'Target 1' compiling misc.c... Includes\STM32_SPL\src\misc.c(24): error: #5: cannot open source input file "misc.h": No such file or directory #include "misc.h" Includes\STM32_SPL\src\misc.c: 0 warnings, 1 error ".\STM32F103.axf" - 1 Error(s), 0 Warning(s). Target not created файл misc.р добавлен, не знаю чего ему надо -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Да я не спорю что у меня с этими стм и кайлом какая-то хрень получается, может не мое (по стилю, простоте, точнее сложности в отличие от avr. Даже xilinx ise с vhdl и то столько вопросов не вызывало) но надо добить эту гадину раз уж столько времени потратил. А вообще я по примерам и делал -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Галочка в Output напротив Create HEX file поставлена с самого начала - в статье-примере про это написано было, так что дело в чем-то другом. Кейл пишет в ответ Build target 'Target 1' FCARM - Output Name not specified, please check 'Options for Target - Utilities' Target not created -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Сейчас вроде бы процесс пошел, но теперь требует выполнить еще одну вещь - в опции таргета->utilities указать файл output (я так понимаю желаемое имя hex файла) какой-то init файл, что за init? Насколько я понял, предыдущий мой тупеж с файлами startup был связан с тем, что их надо еще в дереве проекта в окне справа через нажатие правой кнопкой сделать "Manage Project Items" и там добавить, они в дереве проекта тогда появляются -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Насколько я понимаю все нужные файлы это всего лишь блокнотовские файлы с нужными расширениями. Кто-нибудь может скинуть обычный rar архив с этим добром всяких примочек установки в целевую папку и т.д. На всякий случай напоминаю STM32F103VCT6, беру его, распаковываю и в нужную папку в проекте, и указываю один путь. Почему так не делают? К тому же, возможно при установке ПАКа какой-нибудь файл не распаковался, комп подозрительно себя вел - какой-то debug от микрософт пытался запустить -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Я сейчас тоже так сделал и включенные пути отобразились те же что я делал для свойств таргета. Понятно, значит свойства "нижних ступенек" трогать не надо Добавить в проект это в смысле написать вначале листинга # include "---------------" или нужный файл закинуть в папку? что касается закинуть нужный файл, то все что было разместил, пути указал, файла нужного может нет? Как этот стартаповский файл называется, какое расширение у него? -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

-

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Вобщем в папке которая распаковалась есть папки STM32_CMSIS и STM32_SPL, в последней одна папка с файлами 1 Я создал в папке проекта папку для всего этого и указал на нее путь 2 перекинул все файлы из STM32_SPL 3 в папке STM32_CMSIS есть как файлы так и две папки CoreSupport и DeviceSupport, в DeviceSupport более сложно, там как файлы так и папки. Я "распоторошил" все папки, перекопировав файлы в папку, которая в проекте или надо полностью перенести? (Я думал, так путь не найдет) я на всякий случай и полностью перенес, "рядом поставил" в папке -

Куда в keil5 закинуть cmis stm32f106

Aleksey_Serov ответил Aleksey_Serov тема в ARM, 32bit

Злоключения продолжаются. На этот раз все установлено, МК на макетке, программатор коннектится (у китайского программатора ST-LINK, оказывается надо крышку снять, на которой распиновка написана и посмотреть на плату - там может быть другая распиновка), файлы F10x GPIO rcc , как .h так и .c в папке вложенной в паку проекта, путь указан в настройках как таргета так и сорс группы. Создаю пробный проект, взял вот отсюда https://microtechnics.ru/stm32-uchebnyj-kurs-gpio-porty-vvoda-vyvoda/, вот код /***************************************************************************************/ //Подключаем все нужные файлы #include "stm32f10x.h" #include "stm32f10x_rcc.h" #include "stm32f10x_gpio.h" /***************************************************************************************/ //Тут будет вся инициализация всей использующейся периферии void initAll() { // Объявляем переменную port типа GPIO_InitTypeDef GPIO_InitTypeDef port; // Это функция из файла stm32f10x_rcc.c, включает тактирование на GPIOA // GPIOA сидит на шине APB2 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE); // Про эту функцию напишу чуть ниже GPIO_StructInit(&port); // Заполняем поля структуры нужными значениями // Первый вывод – вход для обработки нажатия кнопки – PA1 port.GPIO_Mode = GPIO_Mode_IPD; port.GPIO_Pin = GPIO_Pin_1; port.GPIO_Speed = GPIO_Speed_2MHz; // А про эту функцию мы уже говорили // Отметим только что один из параметров – указатель(!) на нашу структуру GPIO_Init(GPIOA, &port); // Настраиваем вывод, на котором будет висеть диодик – PA0 port.GPIO_Mode = GPIO_Mode_Out_PP; port.GPIO_Pin = GPIO_Pin_0; port.GPIO_Speed = GPIO_Speed_2MHz; GPIO_Init(GPIOA, &port); } /***************************************************************************************/ int main() { // Объявляем переменную для хранения состояния кнопки uint8_t buttonState = 0; initAll(); while(1) { // С помощью функции из SPL считываем из внешнего мира состояние кнопки buttonState = GPIO_ReadInputDataBit(GPIOA, GPIO_Pin_1); if (buttonState == 1) { GPIO_SetBits(GPIOA, GPIO_Pin_0); } else { GPIO_ResetBits(GPIOA, GPIO_Pin_0); } } } /***************************************************************************************/ Кейл выдает ошибку Build target 'Target 1' linking... .\Test_001.axf: Error: L6320W: Ignoring --entry command. Cannot find argument 'Reset_Handler'. .\Test_001.axf: Warning: L6320W: Ignoring --first command. Cannot find argument '__Vectors'. Not enough information to list image symbols. Not enough information to list the image map. Finished: 2 information, 1 warning and 1 error messages. ".\Test_001.axf" - 1 Error(s), 1 Warning(s). Target not created До этого создавал проекты по другим примерам, все то же самое - не находит аргумент обработчика сброса и аргумент __векторы (что это значит я без понятия) -

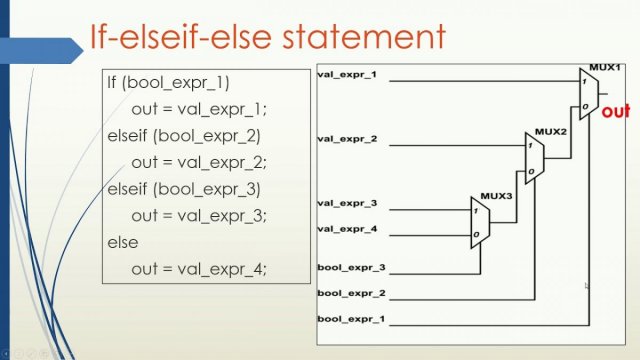

Вот так теперь выглядит мой проект library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ADSQ is port( in_aa,in_bb: in signed (28 downto 0); out_cc: out signed (28 downto 0); to_xyy: out std_logic ); end entity; architecture adswq of ADSQ is signal adsr: signed (29 downto 0); begin adding:process(in_aa,in_bb) begin if(in_aa<1)then adsr<=in_aa+in_bb; elsif(in_aa>0)then adsr<=in_aa-in_bb;end if; to_xyy<=adsr(28); out_cc<=adsr(28 downto 0); end process; end adswq; ------------------------------------------------------ ------------------------------------------------------ library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ADRQ is port( in_aa,in_bb: in signed (32 downto 0); out_cc: out signed (32 downto 0); from_z: in std_logic ); end entity; architecture adsrwq of ADRQ is signal adsr: signed (33 downto 0); begin adding:process(in_aa,in_bb,from_z) begin if(from_z = '0' )then adsr<=in_aa+in_bb; elsif(from_z = '1' ) then adsr<=in_aa-in_bb;end if; out_cc<=adsr(32 downto 0); end process; end adsrwq; ------------------------------------------------------ ------------------------------------------------------ library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity kolonka_z is port( test_005: out signed ( 32 downto 0 )); end entity; architecture kolonka_zz of kolonka_z is type ARCTG_MSV is array ( 20 downto 0 ) of signed (28 downto 0);signal arctg: ARCTG_MSV; type Z_to_Z_MSV is array ( 21 downto 0 ) of signed (28 downto 0);signal ztz: Z_to_Z_MSV; type X_shifted is array (21 downto 0) of signed ( 32 downto 0 ); signal x_sdvinut: X_shifted; type Y_shifted is array (21 downto 0) of signed ( 32 downto 0 ); signal y_sdvinut: Y_shifted; type IN_X is array (21 downto 0) of signed ( 32 downto 0 ); signal xtx: IN_X; type IN_Y is array (21 downto 0) of signed ( 32 downto 0 ); signal yty: IN_Y; signal to_xy: std_logic_vector( 21 downto 0 ); ---------------------------------------------------- component ADSQ port( in_aa,in_bb: in signed (28 downto 0); out_cc: out signed (28 downto 0); to_xyy: out std_logic ); end component; component ADRQ port( in_aa,in_bb: in signed (32 downto 0); out_cc: out signed (32 downto 0); from_z: in std_logic ); end component; begin abbc003: process begin to_xy(0)<='0'; xtx(0)<="001000000000000000000000000000000"; yty(0)<="000000000000000000000000000000000"; -- ztz(0)<="00010000000000000000000000001"; ztz(0)<="00000111000111000111000111000"; arctg(0)<="00010000000000000000000000000"; arctg(1)<="00001001011100100000001010001"; arctg(2)<="00000100111111011001110000101"; arctg(3)<="00000010100010001000100011101"; arctg(4)<="00000001010001011000011010100"; arctg(5)<="00000000101000101110101111110"; arctg(6)<="00000000010100010111101100001"; arctg(7)<="00000000001010001011111000101"; arctg(8)<="00000000000101000101111100101"; arctg(9)<="00000000000010100010111110010"; arctg(10)<="00000000000001010001011111001"; arctg(11)<="00000000000000101000101111100"; arctg(12)<="00000000000000010100010111110"; arctg(13)<="00000000000000001010001011111"; arctg(14)<="00000000000000000101000101111"; arctg(15)<="00000000000000000010100010111"; arctg(16)<="00000000000000000001010001011"; arctg(17)<="00000000000000000000101000101"; arctg(18)<="00000000000000000000010100010"; arctg(19)<="00000000000000000000001010001"; arctg(20)<="00000000000000000000000101000"; test_005<=xtx(21); end process; obviazka_adder: for i in 0 to 20 generate obviazka_gen:ADSQ port map( in_aa=>ztz(i), in_bb=>arctg(i), out_cc=>ztz(i+1), to_xyy=>to_xy(i+1) ); end generate; X_obviazka: for k in 0 to 20 generate y_sdvinut(k)<=shift_right (yty(k),k); obviazkax_gen:ADRQ port map( in_aa=>xtx(k), in_bb=>y_sdvinut(k), out_cc=>xtx(k+1), from_z=>not to_xy(k) ); end generate; Y_obviazka: for k in 0 to 20 generate x_sdvinut(k)<=shift_right (xtx(k),k); obviazkay_gen:ADRQ port map( in_aa=>yty(k), in_bb=>x_sdvinut(k), out_cc=>yty(k+1), from_z=> to_xy(k) ); end generate; end kolonka_zz; Арктангенсы в этом же entity, как и исходные данные. В сумматорах вначале было применено 2 независимых if, потом переделал на elsif, Warning'ов стало меньше, хотя не до конца понимаю в чем дело - elsif проиллюстрирован в примерах где мультиплексоры подключены лестницей. Разрядность выбрал избыточную - это поправимо, для НЧ АЦП (приемник с преобразованием вниз до ПЧ в десятки кГц) может и так нормально. Код компактный, но синтезатор генерирует дольше