Ascold

Участник-

Постов

21 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Ascold

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

У Хоровица и Хилла есть уравнение Эберса-Молла и рассуждения про бету, а также отсечку и насыщение. Что касается симуляторов, то насколько я знаю, в микрокапе у транзистора существует эквивалентная схема(не столько физическая, сколько рассчётная), у которой больше 20 параметров. Хотя, кажется, я(не без сторонней помощи) понял, в чём дело: пусть потенциал базы Т2 фиксирован, а Т1 - растёт. Транзистор Т1 пытается приоткрыться, Т2 - призакрыться, потенциал точки В чуть падает, ток зеркала чуть возрастает в обеих плечах. При этом суммарный ток плеч зеркала равен почти неизменному току источника тока, т.е. источник тока будет препятствовать коллекторному току Т4 нарастать тоже, тогда как транзистор Т4 по мере роста потенциала точки in будет стараться открыться. Это приведёт к тому, что он начнёт двигаться к состоянию, близкому к насыщению, отберёт часть базового тока Т3 на себя, но в итоге сильно уменьшит своё напряжение Uкэ, что приведёт к существенному росту напряжения на коллекторе Т2, а токи плеч особо меняться не будут.

-

1)Транзистор Т1 приоткрывается, пусть и чуть-чуть(сопротивление между коллектором и эмиттером падает). По какой причине не будет происходить уменьшения его коллекторного напряжения?(одно предположение я выдвинул - чуть подскочивший вслед за этим ток зеркала мгновенно скомпенсирует падение потенциала точки В, а так как эта ООС действует мгновенно, ток коллектора Т1 и зеркала меняться не будет. Это верно?) 2)Если первое верно, то потенциал базы Т3 хоть чуть-чуть, но упадёт(и окажет своё влияние на ток зеркала: феноменологическая моделька Эберса-Молла говорит, что для увеличения тока коллектора в 10 раз надо увеличить Uбэ всего на 60 мВ). Если (1) неверно, тогда нет, ибо потенциал коллектора Т1 равен потенциалу базы, и следовательно, задаёт ток зеркала. С другой стороны, транзистор Т1 тоже попытается выставить в зеркале ток, равный своему коллекторному. 3)Почему Т3- КЗ? Напряжение база-эмиттер Т3 невелико, но весьма малые его изменения приводят к большому изменению тока эмиттера, а с ним и коллектора Т3. Вроде, ничего не отрезал - скопировал из книжки рисунок как есть. Высокоомная нагрузка и цепи смещения подразумевается, конечно. Важно определить, меняется ли потенциал точки В постоянным при наличии дифференциального входного сигнала или нет, и почему? Каскод пока добавлять не будем, любопытно, как ведёт себя потенциал точки В именно в таком варианте. Про ограничение коэффициента усиления эффектом Эрли - Вы имеете ввиду небесконечность диф. сопротивления токового зеркала как источника тока в коллекторной нагрузке? Но именно с этого я начал тему: не хочу рассуждать формально, хочу разобраться, как будут меняться токи и потенциалы при поступлении диф. сигнала. В общем, чего бы я хотел получить от уважаемых участников форума: обоснованного рассуждения о том, будет ли меняться потенциал точки В и ток зеркала при появлении диф. сигнала.

-

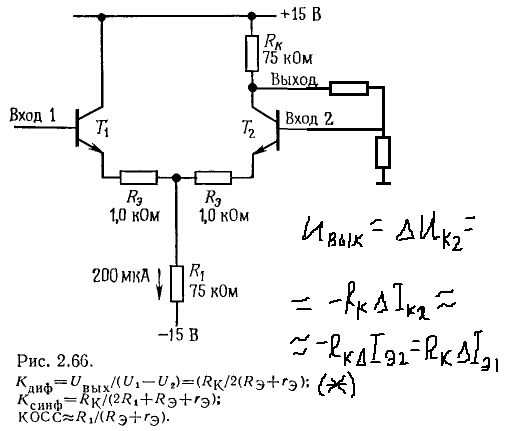

Здравствуйте! Начал изучать схемотехнику по Хоровицу и Хиллу. С токовым зеркалом как таковым вопросов нет: потенциалы баз одинаковы, если же транзисторы в линейном режиме, то с точностью до дисбаланса токов базы и эффекта Эрли, который делает горизонтальные участки выходных характеристик чуть наклонными, коллекторный ток Т2 будет равен коллекторному току Т1 независимо от сопротивления нагрузки. Однако далее Хоровиц и Хилл говорят о "красивом решении" коллекторной нагрузки диф. каскада, если туда поставить токовое зеркало. На первый взгляд, так оно и есть: токовое зеркало как источник тока имеет высокое дифф. сопротивление, что придаст каскаду большой коэффициент дифф. усиления Kдифф=Rк/2Rэ. Объяснения работы такой схемы, которые мне встречались, опираются на фразу о высоком дифференциальном сопротивлении зеркала. Но смотрю внимательно, и вырисовывается немного другая картина: потенциал базы Т3 ведь меняется? Пусть потенциал эмиттера Т1 растёт, тогда Т1 и Т2 приоткрываются и призакрываются соответственно. Пусть в начальный момент состояние Т1 соответствовало точке P на характеристике. Будь Uкэ=const, с ростом входного сигнала транзистор перешёл бы в точку Q, однако на самом деле(он же приоткрывается - сопротивление между коллектором и эмиттером падает, причём сильно, значит, и напряжение на коллекторе должно упасть(попадаем куда-то в точку R), значит падает потенциал базы Т3 и ток зеркала увеличивается, что приводит к сильному росту потенциала коллектора Т2(ток возрос и сопротивление призакрывающегося Т2 возросло). Прав я, или это нужно объяснять иначе? А с другой стороны, приоткрывание Т1 влечёт за собой приоткрывание Т3 - падение уже его сопротивления между базой и эмиттером, ведь входная характеристика Т3 напоминает диодную, т.е. нельзя исключить, что сопротивление Т3 начнёт падать примерно так же, как и Т1, что приведёт к неизменности потенциала точки В - коллектора Т1, а также тока зеркала? Потенциал точки А, конечно, тоже меняется, но не сильно, значит, в плане напряжения источник тока "не портит" картину распределения напряжения между T1-T3.

-

Поставил оптимизацию в компиляторе, проблема решилась.

-

ATMega8: не получается запись в EEPROM

Ascold опубликовал тема в MCS51, AVR, PIC, STM8, 8bit

На выходе стабильно получается d=0xFF. С напряжением питания МК всё в порядке(5,2В от лабораторного источника). Вот мой код, вроде, делаю всё по даташиту(там, правда, есть ещё пункт " Wait until SPMEN in SPMCR becomes zero", в примере кода они его опускают, но даже если добавить, ничего не меняется. Пробовал менять контроллер(явно из другой партии) - ничего не меняется. Пытался писать в ячейки с другими адресами - тоже не получается. #include <iom8.h> #include <ina90.h> #define bit(n) (1<<(n)) /* set i-bit */ #define setbit(port,n) (port|=bit(n)) /* set n-bit in port */ #define clrbit(port,n) (port&=(~bit(n))) /* clr n-bit in port */ #define EEMWE 2 //EEPROM Master write enable bit #define EEWE 1 // EEPROM write enable bit #define EERE 0 //EEPROM read enable bit unsigned char x, d=0; void WriteEEPROM(unsigned char adr, unsigned char data) { while(EECR&(1<<EEWE)); //wait for the previous EEPROM operation to be ended EEAR=adr; EEDR=data; //enter adress and data to the registers _CLI(); // forbid interruptions setbit(EECR,EEMWE); // let write setbit(EECR,EEWE); // command to write _SEI(); //let interruptions } unsigned char ReadEEPROM(unsigned char adress) { while(EECR&(1<<EEWE)); //wait for the previous EEPROM operation to be ended EEAR=adress; //enter adress setbit(EECR,EERE); // command to read x=EEDR; //save EEDR return x; //return data } void main(void) { DDRB=0xFF; PORTB=0x00; // PORTB out WriteEEPROM(0,1); for(;;) { d=ReadEEPROM(0); if(d==1) setbit(PORTB,0); else if(d==0xFF) setbit(PORTB,1); } } -

Титце и Шенк уж очень формально обращаются с транзисторами - валят на читателя сразу эквивалентные схемы, ну и вообще транзисторной схемотехнике уделяют меньше внимания, чем ХХ. Я в своё время пытался найти книжку, написанную про то же, что ХХ, но системнее, чем ХХ, и не нашёл таковой, приходилось читать ХХ "между строк", общаться с опытными электронщиками, в общем дискомфортно. Именно поэтому любопытно, в каком ВУЗе эта проблема более-менее успешно решена, ну и всё остальное. Вообще, не покидает ощущение, что с системностью и качеством передачи накопленного знания математики впереди планеты всей, физики - несколько хуже, инженеры - ещё хуже(что соответствует падению уровня точности науки от математиков к инженерам и не радостно).

-

Это всё, конечно, отлично, но довольны ли те, кто считает, что долбаться с корявостями в том же Хоровице и Хилле студент должен непременно героически и один, своим собственным образованием в области аналоговой схемотехники? Я вот своим недоволен категорически(а вот математическим образованием - доволен вполне, хоть и ни разу не математик, но книги по оному написаны почтив всегда последовательно и системно). Ой, там же информатика сплошная или нет? В смысле, что времени на схемотехнику в учебном плане достаточно ли?

-

Само собой, учёба в ВУЗе ограничена, но она может быть качественной, а может - не очень. Например, если меня спросят про физфак МГУ в сравнении с ФОПФ МФТИ, я тут же отвечу, что курс матанализа наиболее сбалансированный как раз в МГУ, в МФТИ же последний его вариант настолько гружёный(за три семестра студент должен освоить не только пределы, производные, интегралы, ряды, но и основы дифф. геометрии на многообразиях, исчисление форм, когомологии), что я отказываюсь верить в качество этой затеи; тем не менее в том же МФТИ есть возможность теоретикам войти во "святая святых" теоретической физики в виде струнной тематики, однако сколь оно глубоко - не поручусь, да и один ныне покойный академик скептически относился к струнной тематике в РФ; могу показать нюансы преподавания ряда разделов теорфизики там и там(или свести со знающими людьми), благо эти институты на данную тему не секретничают; также могу обоснованно заметить, что качественный, красивый курс квантовой теории поля вообще трудно встретить где-либо. При этом личность научрука с какого-то момента становится для студента-физика более важной, чем учебный план(это к вопросу о самостоятельной работе), но вот МГУ и МФТИ любят детально рассказывать про эти вещи(а математики так и вовсе находятся состоянии почти конфликта и ранжирования друг друга на тему "кто же из нас лучше всего готовит студентов на планете"), чего не скажешь о технических ВУЗах. Что такое "создавать условия для самообразования и роста" - непонятно, это очень туманное утверждение. Вот когда в моём провинциальном универе лектор по матану в своё время начала пачками пропускать доказательства теорем, но при этом вскользь произнесла фамилию автора прекрасного учебника(Фихтенгольц"), по которому я, собственно, обучался, это было типа создание условий для моего роста? А когда лектор по "Основам радиоэлектроники" дико коряво изложил принцип работы транзистора(поливая при этом доску кучей формул с h-параметрами, наводя тень на плетень около понятия "выходное сопротивление" и апеллируя к сомнительной книге Нефёдова) - это тоже было "создание условий для моего самообразования"? Мне кажется, что скорее разгильдяйство и вредительство. Микроконтроллеров у нас был целый семестр, но научились мы почему-то рекордно мало чему. В бытность свою учителем в физматшколе я детям по этой тематике на факультативе давал больше, чем универ мне - как студенту по учебному плану. Моя alma mater - место, так сказать, с неопределённым профилем(и они этим отбивались от вопросов " а почему так мало", " а почему так криво" и т.д.), типа "здесь университет - вас учат учиться, а не дают профессию, за профессией - в технические вузы". Вот я и исследую вопрос - какой из технических вузов по электронике более качественный и в каких аспектах, как раз для того, чтобы неголословно отвечать людям на такие вопросы, тем более, что литература для самообразования по электронике зачастую очень плохо написана(думаю, никто не будет спорить, что Хоровиц и Хилл методически весьма корявы, да и в принципе аналоговая электроника такова, что в ней что-то можно легко и точно доказать, а что-то - не подлежит аккуратному анализу, потому хороший преподаватель здесь гораздо значимее, чем лектор по матану или по общей физике, альтернативу которому всегда можно найти в виде хорошей книги).

-

При попытке получить ответ на данный вопрос путём поиска отзывов в интернете, столкнулся с трудностью: их мало и они весьма водянисты. Кроме того, в рамках институтов есть ещё и разные специальности, а подробные учебные планы не везде выложены. С другой стороны, бауманка, например, какбе намекает(и её выпускники это подтверждают), что системное, методичное образование а-ля мехмат МГУ или матфак ВШЭ- не их конёк: https://iu4.ru/stud/howto.php (например, пассаж "когда проучился 4 года, вроде ничему и не научился. Причина такого синдрома - отсутствие сочетания хобби и учебы"). Но у Бауманки хотя бы подробные учебные программы и материалы гуглятся. Про МИЭТ видел хороший отзыв https://tabiturient.ru/vuzu/miet/ (от 29 марта 2023), правда у меня создалось впечатление перекоса в тему ПЛИС(впрочем, неясно, что там за "хорошие лабы по аналоговой схемотехнике"), да и специальность автора отзыва - ИВТ, а не радиотехника или КРЭС. Было бы здорово, если бы здесь нашлись люди, окончившие эти институты, или преподающие в них, которые могли бы дать ответы на такие вопросы: 1. Сколь полно и обстоятельно осваивается аналоговая схемотехника в размере, например, 2-3 глав 1 тома Хоровица и Хилла? Устраняет ли программа ВУЗа всякие методические недочёты, свойственные этой книге? (типа отсутствия доказательства утверждения "последовательно соединённые резисторы из делителя смещения по сигналу соединены параллельно" и т.д.) 2. Сколь хорошо и гармонично(без заскоков в применение квантовых статистик в физику твёрдого тела) предваряется аналоговая схемотехника азами твёрдотельной электроники? 3. Сколь глубоко идёт изучение аналоговой электроники вглубь и вширь(нюансы проектирования усилителей, генераторов, приёмников, передатчиков и т.д)? 4. Цифровая схемотехника "рассыпная"(булева алгебра, триггеры, регистры, шифраторы, автоматы с памятью)? 5. ПЛИС - сколь много, сколь глубоко? 6. Микроконтроллеры - какие, сколь много, сколь глубоко(скажем, сумеет ли хороший выпускник ВУЗа, за вечер состыковать на Си какую-нибудь авр-ку или stm-8 с часовой микросхемой по TWI)? 7. Теория антенн - есть ли, сколь глубока? 8. Философский вопрос: у инженеров вообще бывает так, чтобы их обучение в ВУЗе было именно методически хорошо выверено, обстоятельно и качественно сделано или же всё-таки "какая-то квалификация не благодаря, а вопреки институту"?

-

Операционный усилитель и ООС

Ascold ответил Ascold тема в В помощь начинающему

если напряжение, подаваемое на конденсатор, меняется со временем по линейному закону, а сопротивлением проводов и утечкой конденсатора можно пренеберечь, то ток будет определённо постоянным. -

Операционный усилитель и ООС

Ascold ответил Ascold тема в В помощь начинающему

Я, м.б. виноват, что недостаточно точно сформулировал задачу, что же здесь считать идеальным, т.к. сам с этим не определился. Если предельно упростить, пока придумал такое. Пусть у нас просто диф. усилитель(ООС по типу схемы неинвертирующего усилителя на ОУ), изменение выходного напряжения dV которого пропорционально разности входных потенциалов прямого u и инверсного входов: dV=k*(u-v) с большой точностью(k конечен). Для простоты пренебрежём задержкой по времени между изменением напряжений на входах и откликом на выходе, пусть также в начальный момент u=v. Вот напряжение u растёт на б.м. величину du, тогда через цепь ООС с коэффициентом передачи b тут же возникает приращение dv, свяжем du с dv: раз исходно было u=v, то u-v=d(u-v)=du-dv. Раз v=b*V, то dv=b*dV=b*k*(du-dv), отсюда du=(1+1/b*k)dv, интегрируя, получим u=(1+1/bk)v+С. Раз u=0 влечёт за собой v=0, то и С=0, и если b*k велико, то u примерно равно v. Если же ввести задержку - отклик сигнала на выходе ОУ наступает через время T после появления его на входе, то, наверное, будет что-то типа dv(t)=b*k*(du(t-T)-dv(t-T)), что сложненько для дальнейшего, даже если задать скорость нарастания фронта u=u(t) явной формулой. Мне кажется, я спрашивал что-то такое, но продолжаю думать, т.к. при быстром фронте нарастания сигнала задержка, вносимая ОУ, значима. -

Операционный усилитель и ООС

Ascold ответил Ascold тема в В помощь начинающему

Доказательство утверждения для ясности и полноты картины, не более. Подумал, и решил для себя вопрос так: в основе операционного усилителя лежит дифференциальный усилитель, рассмотрим его, например, самый примитивный, что на прилагаемом рисунке. Добавим к нему простейшую цепь ООС и проанализируем поведение. Пусть в какой-то момент сигнал на эмиттере T1 вместе с эмиттерным током I1 начал расти, а ток I2, соответственно, падать. Это через ОС повлечёт за собой повышение напряжения на эмиттере T2, ну и надо не забывать, что выходным напряжением мы называем превышение выходного напряжения над потенциалом покоя коллектора T2, именно в такой трактовке выводится формула (*). Поэтому входные напряжения в итоге более-менее подравняются, а ток через R1 изменится мало(или не изменится вовсе, если заменить R1 идеальным источником тока), причём, видно, что чем больше Rк и тем лучше источник тока, тем больше Кдиф и тем сильнее КОСС. Можно эти рассуждения провести и сразу на идеальном ОУ без рассмотрения всех этих транзисторов и резисторов, конечно, но я, похоже, в такой абстрактной формулировке изначально запутался в том, как правильно понимать Uвых в формуле для коэффициента усиления диф. сигнала. Понятно, что всё вышенаписанное имеет отношение лишь к постоянным сигналам, не о каких переходных процессах и задержках речи нет, но именно это я и пытался понять: почему ОУ, охваченный петлёй ООС, в принципе стремится подравнять потенциалы своих входов. -

Операционный усилитель и ООС

Ascold ответил Ascold тема в В помощь начинающему

Со скоростями процессов мне самому это не нравится, т.к. в ОУ куча переключающихся транзисторов, а цепь ОС может быть всего лишь резистивной цепочкой. Однако другого способа думать на эту тему я что-то пока не изобрёл. Мне доводилось, и не единожды пользоваться операционными усилителями(как усилителями и компараторами, вводить гистерезис и т.д.). Но вот недавно задумался, каковы теоретические основания считать, что отрицательная обратная связь реально всё выровняет, откуда это вытекает для идеального ОУ? Верование в 3 главу Хоровица и Хилла(там это постулируется) + эксперимент - не впечатляет... -

Операционный усилитель и ООС

Ascold опубликовал тема в В помощь начинающему

Здравствуйте! Расчёты схем с операционным усилителем(идеальным), охваченным отрицательной обратной связью, базируются на том, что раз его коэффициент k усиления дифф. сигнала без ООС принимается практически бесконечным, то наличие ООС с к-том передачи b влечёт за собой выравнивание напряжений на входах посредством, собственно, ООС. На первый взгляд оно логично: пусть напряжение прямого входа чуть-чуть подросло относительно напряжения инверсного, тогда эта добавка через цепь ООС придёт на инверсный вход, разность напряжений между входами станет меньше, она через выход ОУ и ООС снова приложится к инверсному входу, и мы и глазом моргнуть не успеем, как потенциалы входов выровняются. Но я решил рассмотреть эти "итерации"(на деле, конечно, всё происходит непрерывно) подробнее, и вот что получилось. Пусть на "нулевой" итерации потенциал инв. входа 0, а прямого входа - u. Значит, на выходе возникает напряжение k*u, его доля b*k*u через ООС поступит на инв. вход и в итоге на первой итерации усиливаться усилителем будет уже u-bku, значит, на выходе будет k(u-bku), а на инверсный вход поступит bk(u-bku). На n-й итерации на выходе будет напряжение, равное ku(1-bk+(bk)^2-...+-(bk)^n), что на (n+1)-й итерации даст напряжение на инверсном входе u(bk-(bk)^2+(bk)^3-...-(bk)^(n+1)). Если многочлен в скобках даёт в сумме 1 на каком-то этапе(или хотя бы сходится к ней как бесконечный ряд), то да, на инверсном входе тоже установится u, а на выходе - 0. Но произведение b*k не обязано быть меньше 1, да и будучи таковым, не кажется, что в итоге всегда будет получаться 1 в скобках. Если bk>1, то на выходе на первой же итерации будет напряжение ku(1-bk)<0 и в силу большой величины k установится минус напряжение питания... Где я ошибаюсь? -

Рация со сверхрегенерацией

Ascold опубликовал тема в RF & Microwave Design

Решил поизучать радиоприём и передачу. Детекторный приёмник уже делал, а дальше сложнее. Вот здесь https://sekret-mastera.ru/elektronika/ratsiya-nachinayushhego-radiolyubitelya-na-50-mgts.html рассматривается прибор со сверхрегенерацией. Про сверхрегенерацию решил почитать Белкина https://bookree.org/reader?file=532195&pg=9 . У Белкина непонятны некоторые моменты - например, как он выводит затухание https://bookree.org/reader?file=532195&pg=10 (1.4) и что означает фраза "относя E к Uк"? Когда я подставляю (1.2) и (1.3) в (1.1), то получаю E=jw(C_0*R_0-MS)Uк, как отсюда сделать шаг к (1.4), не врублюсь, как отсюда раздобыть мощности в контуре и потери за полпериода? Кстати, (1.1) подразумевает, что в контуре "настоящий" резонанс напряжений - напряжения на катушке и конденсаторе в противофазе. Всегда ли в сверхрегенативных приёмниках такое допущение верно, ведь для этого требуется предположить, что входное сопротивление транзистора велико по ср. с реактивным сопротивлением конденсатора, а это в свою очередь требует малого коллекторного тока, поскольку (хотя бы согласно модели Эберса-Молла) сопротивление эмиттерной части обратно пропорционально этому току?