PICNICK

Участник-

Постов

30 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о PICNICK

-

Звание

Участник

-

Спасибо!!!

-

21891ВМ12Я, каким симулятором пользуетесь? Icarus пойдет? Спасибо!

-

Понял. Спасибо!

-

С задержкой должна же работать. Без буфера картинки не получить?

-

Здравствуйте! Не могу завести камеру, вывод на монитор. Показывает как телевизор без антенны. При повороте камеры "изображение" меняется. Модуль вывода видео работает (сделал вывод цветных полос для проверки). Код простой, без кадрового буфера. always@(posedge PCLK_cam) begin case(FSM_state) WAIT_FRAME_START: begin //wait for VSYNC FSM_state <= (!VSYNC_cam) ? ROW_CAPTURE : WAIT_FRAME_START; frame_done <= 0; pixel_half <= 0; end ROW_CAPTURE: begin FSM_state <= VSYNC_cam ? WAIT_FRAME_START : ROW_CAPTURE; frame_done <= VSYNC_cam ? 1 : 0; pixel_valid <= (HREF_cam && pixel_half) ? 1 : 0; if (HREF_cam) begin pixel_half <= ~ pixel_half; if (pixel_half) data2fifo[7:0] <= data_cam; else data2fifo[15:8] <= data_cam; end end endcase end // *************** always @( posedge clk25) begin pixel_data <= data2fifo; end Что-то упустил видимо. Помогите в нужном направлении пожалуйста. Спасибо!

-

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

Спасибо большое!!! -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

2 new123 По форумам, подкиньте ссылку... Спасибо. -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

В проекте поменял чип на Cyclone ||, компиляция прошла успешно. Всем спасибо! -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

Попробую...Спасибо. -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

Two PLLs are designed to support the LVDS interface. When using LVDS, the I/O clock runs at a slower rate than the data transfer rate. Thus, PLLs are used to multiply the I/O clock internally to capture the LVDS data. For example, an I/O clock may run at 105 MHz to support 840 megabits per second (Mbps) LVDS data transfer. In this example, the PLL multiplies the incoming clock by eight to support the high-speed data transfer. You can use PLLs in EP20K400E and larger devices for high-speed LVDS interfacing. Походу просто на моем APEX EP20K60EQ нет поддержки LVDS..... даташиты читать нужно -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

Больше нет ни предупреждений, ни ошибок -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

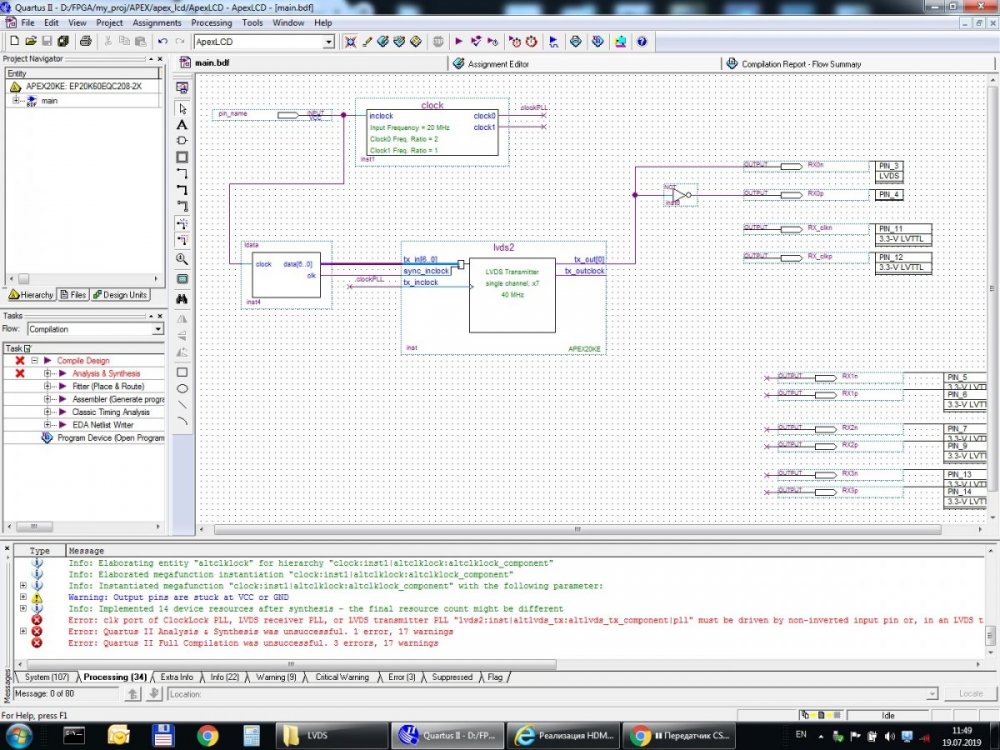

2 Lmx2315 Error: clk port of ClockLock PLL, LVDS receiver PLL, or LVDS transmitter PLL "lvds2:inst|altlvds_tx:altlvds_tx_component|pll" must be driven by non-inverted input pin or, in an LVDS transmitter PLL, the output of an LVDS receiver PLL. Больше нет ни предупреждений, ни ошибок -

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

-

LVDS ошибки..

PICNICK ответил PICNICK тема в Языки проектирования на ПЛИС (FPGA)

Error: clk port of ClockLock PLL, LVDS receiver PLL, or LVDS transmitter PLL "lvds2:inst|altlvds_tx:altlvds_tx_component|pll" must be driven by non-inverted input pin or, in an LVDS transmitter PLL, the output of an LVDS receiver PLL. Пробовал PINs по разному конфигурировать, не помогло. Если к функции не подключать пины, то ошибка не формируется. Спасибо. -

LVDS ошибки..

PICNICK опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Доброго времени суток. Решил попробовать сделать управление LCD панелью по LVDS. Код в графическом веде на мегафункции LVDS. Но возникают ошибки. Что я упустил, подскажите пожалуйста... Схема во вложении APEX 20KE LVDS.bmp