dak

Участник-

Постов

37 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о dak

-

Звание

Участник

- День рождения 29.10.1994

Информация

-

Город

Array

Посетители профиля

967 просмотров профиля

-

Вот это подляна! Спасибо.

-

Quartus II 15.1 не генерирует sdo для Циклон 5?

dak опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Хотел провести post PAR моделирование для пятого Циклона и обнаружил, что sdo файл не генерируется. Пересобрал тот же проект под Max II - sdo появился. Небольшой поиск в интернете показал, что вроде как для пятого Циклона так и должно быть. Я чего-то не понимаю? -

Здравствуйте. Имеется массив из 32 векторов. Одновременно должно что-то писаться только в пять из них. Номера используемых векторов не фиксированы и передаются из вне. Проблема в том,что при использовании текущего подхода синтезатор говорит мне,что он видит для каждого бита каждого вектора ситуацию множества драйверов - то есть, потенциально может возникнуть ситуация, когда все пять модулей контроля будут писать в один и тот же вектор массива. LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.numeric_std.all; library L1_rom_bank_lib; use L1_rom_bank_lib.types.all; ENTITY addr_controller IS port( clk : in std_logic; data_current : in std_logic_vector (7 downto 0); data_1 : in std_logic_vector (7 downto 0); data_2 : in std_logic_vector (7 downto 0); data_3 : in std_logic_vector (7 downto 0); data_4 : in std_logic_vector (7 downto 0); addr_in : in std_logic_vector (9 downto 0); addr : out mem_adr (31 downto 0) ); END ENTITY addr_controller; -- ARCHITECTURE arch OF addr_controller IS BEGIN process(clk) begin if rising_edge(clk) then if (data_current /= data_1 or data_current /= data_2 or data_current /= data_3 or data_current /= data_4) then addr(to_integer(unsigned(data_current))) <= addr_in; end if; end if; end process; END ARCHITECTURE arch; Все пять модулей управления выполнены по одному шаблону, код которого приведен. Не совсем понимаю,на что жалуется синтезатор, ведь контроль записи в один и тот же вектор присутствует. Я подумал, что происходит это из_за отсутствия ветки ELSE, и в случае совпадения хотя бы одного из задающих векторов два модуля пишут в один и тот же вектор состояние неопределенности. Поэтому я добавил к массиву еще пять векторов, куда модули пишут в случае хотя бы одного совпадения: LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.numeric_std.all; library L1_rom_bank_lib; use L1_rom_bank_lib.types.all; ENTITY addr_controller IS generic( false_vector : integer := 33); port( clk : in std_logic; data_current : in std_logic_vector (7 downto 0); data_1 : in std_logic_vector (7 downto 0); data_2 : in std_logic_vector (7 downto 0); data_3 : in std_logic_vector (7 downto 0); data_4 : in std_logic_vector (7 downto 0); addr_in : in std_logic_vector (9 downto 0); addr : out mem_adr (36 downto 0) ); END ENTITY addr_controller; -- ARCHITECTURE arch OF addr_controller IS BEGIN process(clk) begin if rising_edge(clk) then if (data_current = data_1 or data_current = data_2 or data_current = data_3 or data_current = data_4) then addr(false_vector) <= (others=>'0'); else addr(to_integer(unsigned(data_current))) <= addr_in; end if; end if; end process; END ARCHITECTURE arch; У каждого модуля свой generic,разумеется. Впрочем, это не дало нужного эффекта. Подскажите,пожалуйста,как быть.

-

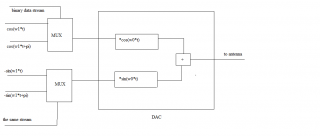

Они здесь не используются. Я делаю имитатор неких известных сигналов, и в оригинале формирование происходит с боковыми лепестками.

-

Так я его и использую на приложенной картинке. Вопрос в том, не сломается ли модуляция от того, что фаза сдвигающих син/косов может меняться несколько раз за один их период.

-

Здравствуйте. Возник вопрос. Реализую на ПЛИС передатчик с BPSK модуляцией несущей. Формирую сигнал, передаю его на ЦАП - все ок. Следующий этап: помимо изменения фазы несущего колебания хочется сдвигать частоту несущей (то есть той частоты, что задается в ЦАПе, поскольку перенос на высокую частоту осуществляет именно он). Известно, что для спектрального сдвига надо умножить несущую на комплексную экспоненту, то есть на синус/косинус. То есть, теперь мне по сути можно умножать несущую н на последовательность из 1 -1, а поставить мультиплексор и переключать битовой последовательностью синус/косинус соот. фазы. Здесь и возникает вопрос. Частота несущей: десятки-сотни МГц, частота битовой последовательности: 0,5 - 10 МГц, а вот частота смещения имеет порядок кГц. То есть, за один период этих смещающих синусов/косинусов смена фазы может произойти несколько раз. Не повлияет ли это в итоге на формирование сигнала на высокой частоте?

-

Я тут вот о чем подумал. Для меня не критично, если данные задержатся на такт. В таком случае, я могу делить отсчеты на степень двойки, сдвигом. Это не дорого по ресурсам и сразу понятно, какие биты взять. Как вам такое решение?

-

Спасибо. Эта формула вызывает вопросы. Видимо, там в скобках должно быть сложение, а не умножение. "МАКСИМАЛЬНЫЙ коэффициент передачи фильтра K (вернее округленный в большую сторону Lk=log2(K)" Не совсем понимаю, как это применить к моему случаю. Можно считать, что я отсчеты синуса умножаю на константу. Диапазон синуса -32000 до 32000, константа может принимать целые значения от 0 до 32000.

-

Так я же написал, что хочу получить знаковое число.

-

Округление и отбрасываение разрядности

dak опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет. Допустим, у меня есть вектор 48 бит, из которых мне надо только 16 бит. Известно, что вектор 48 бит получается из перемножения векторов 32 бита и 16 бит, при этом вектор 32 бита - беззнаковое число (максимум 32000, 2 в какой-то там степени), а 16 бит - число знаковое, и диапазон от -32000 до 32000 (та же степень двойки). Мне надо, чтобы оставляемый от 48 битного вектор в 16 бит был также в диапазоне от -32000 до 32000. Идея в том, что тот 16 битный вектор, который умножается на 32 битный вектор - это отсчеты синуса, я не могу менять его амплитуду. Вектор 32 бита - амплитуда синуса, и хочу, чтобы выходной вектор (который также будет синусом) имел близкую амплитуду (близкую к тому значению, что записано в 32 битный вектор). Рассматривал на таком примере: допустим,есть 4 битный вектор. Диапазон от -8 до 7. Если убрать младший разряд, то останется 3 бита, и диапазон будет от -4 до 3. То есть, убрать младший разряд - это практически эквивалентно тому, чтобы поделить записанное в вектор число на 2. Как я понимаю, удаление старшего бита будет иметь схожий эффект. Я попробовал покрутить это все дело, но особо не вышло. Подскажите пожалуйста, как выбрать разрядность. PS. Я знаю, что просто отбросить разряды нельзя и знаю что делать дальше, но вопрос сейчас именно в выборе разрядности. -

Оконные функции и преобразование Фурье

dak ответил dak тема в Алгоритмы ЦОС (DSP)

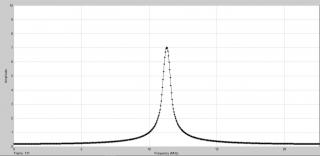

Я тоже об этом думал, поэтому и сделал подсветку частот дискретизации в Матлабе. Во всей модели используется одна и та же ЧД, и равна она в точности той, с которой получены значения синуса. -

Оконные функции и преобразование Фурье

dak опубликовал тема в Алгоритмы ЦОС (DSP)

Здравствуйте. Возник небольшой вопрос. Вроде и книжки полистал, и погуглил, но ответа не нашел. Есть некий сигнал - набор значений синуса, который имеет частоту 11 кГц. В модели Симулинк использую блок Short-Time FFT - то есть, перед вычислением БПФ происходит умножение входного сигнала с окном. Использую окно Блэкмана. В спектре вижу, что гармоника, соот. моему синусу, "переехала" с 11 кГц в 11 МГц. Не могу никак понять - это закономерный и правильный результат, или это ошибка? -

Диплом на FPGA

dak ответил kereokerekeke тема в Языки проектирования на ПЛИС (FPGA)

Построение автоматов что на VHDL,что на Verilog подробно рассмотрено в книжках автора Pong Chu. http://academic.csuohio.edu/chu_p/rtl/index.html -

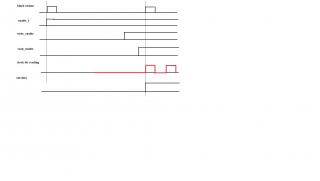

В общем, поковыряв все это дело и полазив в интернете, что-то придумал. На идею натолкнул Maverick. Сразу скажу, что в стартовом посте мой косяк: я не сказал, что клоки для RAM получаются делением некой отдельной тактовой частоты; при этом клок для первого потока получается непосредственно из деления входящего клока,а клок для второго потока получается делением клока для первого потока. Погуглив, нашел такой примитив Xilinx - BUFG_CTLR. При определенной настройке этот примитив работает как клоковый мультиплексор, который по мере своей возможности мгновенно переключает клоки (проверено на железе осциллографом). Итак, как это работает по шагам: 1) получение сигнала разрешения. Использую схему определения изменения фронта сигнала из 0 в 1 (вот такую http://marsohod.org/verilog/157-verilogedges). С каждым изменением проверяю, поднят ли у меня внешний управляющий сигнал,и если поднят, то отправляю единицу: process(arst,mark_imp,control) begin if arst='1' then enable <= '0'; elsif rising_edge(mark_imp) then if control <='1' then enable <= '1'; else enable <= '0'; end if; end if; end process; Буду называть этот сигнал разрешения сигналом EN_1. 2) теперь у меня поднят сигнал разрешения по импульсу метки. К моменту приходу следующего импульса метки мне надо сделать свои дела. Первый поток данных я считаю из ROM внутри ПЛИС. Клок для него я запускаю сразу, но считывать хочу начинать не сразу после поднятия сигнала разрешения, а уже ближе к подходу следующей. Для этого мне нужен счетчик, который отсчитает нужное количество времени, а потом заблокируется и перестанет считать. Здесь я и использую указанный выше примитив. На один из входов данных заводится сигнал разрешения, который я получил при приходе метки, а на второй - тот,который хочу получить, и его же использую для адресации. При сбросе этот сигнал устанавливается в 0. Счетчик, пока не отсчитает нужное количество времени, получает сигнал разрешения EN_1, а после (через инвертор) - сигнал разрешения EN_2. Проверка на то,досчитал ли счетчик до нужного значения выполняется так: process(clk240Mhz,arst) begin if arst = '1' then en_2 <= '0'; elsif rising_edge(clk240MHz) then if unsigned(counter) = "нужное число в бинарном виде" then en_2 <= '1'; else en_2 <= '0'; end if; end if; end process; То есть, при старте этот сигнал сбрасывается в 0. Потом, пока счетчик не досчитает до нужного значения держит ноль,а после поднимается в 1. При этом этот EN_2 переключает клоковый мультиплексор и сам служит в качестве данных. 3) чтобы начать считывать что-то в определенный момент времени, надо чтобы в этот момент времени клок для считывания изменил фронт с 0 в 1. Для этого, к двум делителям, которые запукаются при подъеме EN_1, я добавляю еще два, который запустятся по третьему сигналу разрешения EN_3; при этом делить начинают сразу с высокого фронта. EN_3 получаю аналогично EN_2. Теперь что касается фронтов. Использую все тот же клоковый мультиплексор. На один вход данных подаю константу 0, а на другой подключаю выход делителя,работающего по EN_3. EN_3 так же переключает адреса мультиплексора. Так я надеюсь получить имитацию смены фронта. Что скажите?

-

Я нарисовал временную диаграмму того,что я собственно хочу. Mark of time - моя временна меточка; enable_1 - сигнал разрешения, по которому начинают работу некоторые блоки; Далее идут сигналы разрешения на чтение и запись в/из RAM; Потом красненьким нарисован как раз тот сигнал,который я хочу получить. Ну и последний - один (для упрощения) из двух моих потоков данных на выходе. Спасибо, посмотрю.