BuTeK

Участник-

Постов

67 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о BuTeK

-

Звание

Участник

- День рождения 07.10.1981

Контакты

-

Сайт

Array

Информация

-

Город

Array

-

Реализация БПФ на ПЛИС

BuTeK ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

Конечно актуально! Поделитесь информацией... Очень итересно! -

Реализация БПФ на ПЛИС

BuTeK ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

поделитесь рабочей коркой БПФ на почту [email protected] -

А как же AUTO REFRESH и SELF REFRESH, вот что меня сильно пугало... При разработке..

-

Не получается сгенерировать MIGом 1.6 Core SDR RAM (mt48lc4m32b2) на Spartan 3E ? она предлагает только DDR RAM почему так? Или я что-то не так делаю? Объясните в чем дело...

-

Оптимизация проекта

BuTeK ответил BuTeK тема в Языки проектирования на ПЛИС (FPGA)

А он разве ещё и SDRAM поддерживает?! А я почему-то считал, что только DDR... Сейчас посмотрим.. -

Оптимизация проекта

BuTeK ответил BuTeK тема в Языки проектирования на ПЛИС (FPGA)

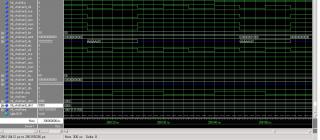

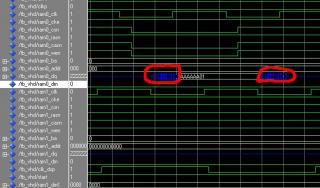

Упростил уже по последнего... Всё равно задержка почему так? Может не там копаю... Совсем уже сбился с толку.. На рисунках показан Behavioral Sim (Img1.jpg) - т.е. то что нужно.. а на Img2.jpg xxnj имею(Post-Route Sim).. process(rst_int_n, sys_clk) if rst_int_n = '0' then .... elsif rising_edge(sys_clk) then .... if start_wr then wr_ena_q <= '1'; else wr_ena_q <= '0'; end if; if wr_ena_q = '1' then shift <= data_in; end if; .... end process; process(sys_clk, st_wr) begin if falling_edge(sys_clk) then SDR_DQ_OE <= not start_wr; SDR_DQ2_OE <= SDR_DQ_OE; end if; end process; SDR_DQ_int <= shift; SDR_DQ<=(others =>'Z') when SDR_DQ2_OE else SDR_DQ_int; Img1.jpg Img2.jpg -

Оптимизация проекта

BuTeK опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Помогите оптимизировать. А то большая задержка получается при выводе данных... А сам что-то не могу ничего придумать не могу... :-( out_cnt: block begin process(rst_int_n, sys_clk, st_wr) begin if rst_int_n = '0' then nom <= 0; elsif rising_edge(sys_clk) then if st_wr then nom <= 8; elsif nom/=0 then nom <= nom - 1; end if; end if; end process; process(sys_clk, rst_int_n) begin if rst_int_n = '0' then SDR_DQ <= (others => 'Z'); elsif falling_edge(sys_clk) then SDR_DQ <= (others => 'Z'); if nom /= 0 then SDR_DQ <= shift(nom - 1); end if; end if; end process; end block; -

Как найти ошибку?

BuTeK ответил BuTeK тема в Языки проектирования на ПЛИС (FPGA)

Хотел поправить.... А получилось как всегда... совсем запутался... и даже то что было перестало работать так как надо.... Может кто-нибудь посмотрит.. подскажет в чем дело... А то я совсем уже не знаю что делать.. :-( Помоги.... А вот и код... ______.rar -

Как найти ошибку?

BuTeK опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Следующая ошибка. При моделировании Post-Route Simulation результат получается правильный, но на плате другой почему так? Где искать причину? То есть я пишу числа в ОЗУ от 01 до 08, и затем с какого бы я не считывал адреса понучаю 01. То есть то что записанно с адресе 00. -

Да так и есть... Вот я и спрашиваю почему ISE неправильно создает файл .mdo для ModelSim? И как это можно обойти...

-

А какое расширение должно быть у этого файла?

-

Ошибка при работе с ModelSim

BuTeK опубликовал тема в Работаем с ПЛИС, области применения, выбор

При попытке эмулирования на ModelSim SE в режиме Post-Map Simulation и Post-Route Simulation программы ISE 8.1.03 ModelSim выдает следующию ошибку: # vsim -lib work -sdfmax /UUT=mt48lc4m32b2.sdf -t 1ps tb_vhd # ** Error: (vsim-SDF-3196) Failed to find SDF file "mt48lc4m32b2.sdf". # Error loading design # Error: Error loading design # Pausing macro execution Почему ISE не создает файл sdf и вообще он должен его создавать для проекта модели? Как быть с такой ошибкой? -

Проблема инициализации

BuTeK ответил BuTeK тема в Среды разработки - обсуждаем САПРы

Попробую посмотреть в документации, правда что-то не замечал.... Может не внимательно читал... А с кабелем думаю все в порядке... Как никак в ПЛИС напрямую кидается... -

Проблема инициализации

BuTeK ответил BuTeK тема в Среды разработки - обсуждаем САПРы

Режим выставлен МАСТЕР (M(2:0) = 0:0:0) Все выводы, кроме TDI и TDO, подключены как рисунке 3.1. А имеет значение в какой последовательности подключены Сигналы TDI? У меня подключение такое: TDI (JTAG)-> TDI |Flash PROM| TDO -> TDI |FPGA| TDO-> TDO (JTAG) -

Проблема инициализации

BuTeK опубликовал тема в Среды разработки - обсуждаем САПРы

Следующая проблема. Не происходить инициализации (загрузки данных с последовательного ПЗУ (XCF04S) с ПЛИС(Spartan 3E)), хотя напрямую в ПЛИС через кабель (Parallel Cable IV) все нормально заливается. При этом данные в ПЗУ заливаются тоже без проблем и проверку проходят. И ещё когда смотрю шины между ПЛИС и ПЗУ осциллографом данные идут, а вот сигнал DONE (ПЛИС) не выставляется… Почему так? Может я не так какие настройки выставил (хотя вроде бы стоит все по умолчанию)? Подскажите в чем может быть дело… А то уже не знаю что делать.