vat

Участник-

Постов

66 -

Зарегистрирован

-

Посещение

-

zombi, Вы правы, иногда симулятор действительно насыпает выходные линии поштучно (реально бесит), иногда на них есть что-то похожее на ожидаемый результат, а иногда тоже Z (закономерности от чего зависит я не заметил). Но правильно, на двунаправленную шину (bidir в последнем примере) он не выводит никогда. Проще вывести это содержимое на виртуальную шину и там смотреть в HEX формате.

-

alexadmin, зачем внутренние цепи? Для симуляции я могу продублировать сигнал на что угодно. Меня смутило что двунаправленная шина не поддерживается встроенным симулятором - не отрисовывается реальный сигнал. Работать ведь будет?

-

Nick_K, включил a и b в списки чувствительности. Результат не изменился. Без процессов и клока я еще вчера попробовал - тоже нет занятия шины. Народ - это пример (bidir.vhd) из первоисточника - "библии" от Интела/Альтеры. Если он не правильный, то во что верить ? )))

-

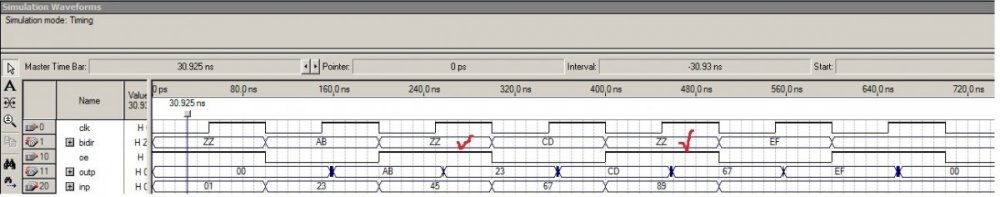

по порядку... сначала результат симуляции для интеловского примера... Комбинации AB, CD и EF вывожу на шину я, между ними должно быть занятие шины устройством, но его нет - Z

-

Все попробовал, ничего не помогает. Не работает симуляция даже в примере от Интела/Альтеры (bidir.vhd (Tri-state bus implementation)): LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY bidir IS PORT( bidir : INOUT STD_LOGIC_VECTOR (7 DOWNTO 0); oe, clk : IN STD_LOGIC; inp : IN STD_LOGIC_VECTOR (7 DOWNTO 0); outp : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END bidir; ARCHITECTURE maxpld OF bidir IS SIGNAL a : STD_LOGIC_VECTOR (7 DOWNTO 0); -- DFF that stores -- value from input. SIGNAL b : STD_LOGIC_VECTOR (7 DOWNTO 0); -- DFF that stores BEGIN -- feedback value. PROCESS(clk) BEGIN IF clk = '1' AND clk'EVENT THEN -- Creates the flipflops a <= inp; outp <= b; END IF; END PROCESS; PROCESS (oe, bidir) -- Behavioral representation BEGIN -- of tri-states. IF( oe = '0') THEN bidir <= "ZZZZZZZZ"; b <= bidir; ELSE bidir <= a; b <= bidir; END IF; END PROCESS; END maxpld; точнее она не работает только в части вывода на двунаправленную шину (команда "bidir <= a;"). Она остается в состоянии Z. Ладно, обойдусь без этого... Всем спасибо!

-

процесс меня асинхронный и эти сигналы я перечислил. У меня такое ощущение что это закидон симулятора. Набросал сейчас на привычной мне схемотехнике простенькую аналогичную схемку - то же самое вышло - шина IO не занимается устройством, там или Z или то что я сам на ней задам внешним воздействием. До этого я использовал выходы с 3я состояниями для ресетов или согласования с 5В девайсами (с резисторами подтяжки) - все работало, даже не тестировал в симуляторе, а тут впервые обратил внимание, так как железки еще нет, а прошивку готовить надо.

-

Спасибо! Попробую изменить (хотя этот пример взял из методички Интел/Альтера). а что такое " список чувствительности" и где его настраивать?

-

Народ, подскажите плиз! Элементарная вещь, но не получается что-то (от жары мозги клинит наверно)). Имеется проект в VHDL , Quartus II 9.1 Web Edition, MAX II EPM570. Использую bidirectional bus: IO : inout std_logic_vector(7 downto 0); .... if OE='0' then IO <= "ZZZZZZZZ"; DB(7 downto 0) <= IO; else IO <= rD; end if; Железка пока не подъехала, тестирую на встроенном симуляторе Quartus. Получается что чтение с шины IO работает нормально, а вот при выдаче данных на нее (из регистра rD при OE='1') на шине IO остается третье состояние (Z). Даже не знаю - в моем VHDL коде ошибка (я в нем новичок) или симулятор неправильно отрабатывает или еще что... Заранее спасибо

-

PHY 100/1000 Mbit/s

vat ответил vat тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Спасибо всем кто ответил... Пожалуй я действительно слишком конспективно все описал... Текущая версия устройства работает по 100 и ничего другого ей не надо, а гигабитный свитч нужен чтобы не резать скорость компа. Тогда как Вы и предложили, решение типа KSZ9893R будет оптимальным (разве что корпус я предпочел бы типа TQFP). Но в перспективе я планировал расширение функционала устройства - мониторить (а может и "корректировать") трафик компа в некоторых приложениях (фильтрация по IP, портам). Тогда лучше иметь не свитч, а пару PHY и пропускать трафик через девайс. Печальки насчет гига у меня нет, так как устройство сделано на базе FPGA и вполне успевает работать с потоком. P.S. а насчет RTL8211CL... кто-нибудь использовал это чудо? Его нет на дигикее (в частности поэтому и не хочу делать на нем), но на Али их завались по пол-доллара за штуку. Просто любопытно - что с ним не так? Почему его не используют в разработках (на али он продается вероятно для целей ремонта аппаратуры)? -

PHY 100/1000 Mbit/s

vat опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Помогите плиз выбрать PHY на 100/1000 Mbit/s. Есть устройство, хорошо работающее на 100 Mbit/s на dp83848c. Этот чип всем устраивает, но в некоторых случаях (когда всего одна Ethernet розетка и комп с выходом через Ethernet) приходится использовать внешний свитч, что не есть хорошо. Если его реализовать в самом устройстве на тех же dp83848c, то скорость подключения компа режется до 100Мб. Была мысль использовать м/с свитча на Гиг с 3я выходами, но в некоторых случаях пригодилась бы возможность фильтровать трафик PC (доработав устройство). Т.е. требуется пара PHY на 100/1000. Очень хочется что-то в простом корпусе типа того же TQFP-48. Интерфейс устроит RGMII. Уже есть в наличии чипы RTL8211CL(LQFP-48) (купленные давным-давно), которые вроде отвечают заявленным требованиям. И с доступность и ценой у них неплохо, но ... уж очень они древние. Не хочется закладывать в разработку чип, который вот-вот исчезнет. Посоветуйте что-нибудь! -

Спасибо большое! Это то что нужно :)

-

Quartus II: как создать мегафункцию на VHDL?

vat опубликовал тема в Среды разработки - обсуждаем САПРы

Доброго времени суток! Имеется довольно большой проект, развиваемый уже много лет (время от времени). Исторически он делался схемотехническим способом. Для дальнейшего его развития хочется использовать VHDL. Но времени (да пожалуй и знаний) для быстрого перевода его на VHDL не хватает. Возможно ли делать свои мегафункции (типа стандартных LPM_ADD_SUB) на VHDL и подключать их в виде блоков в схемотехническом проекте? Если да, то достаточно ли для этого бесплатного Quartus II Web edition? И если можно, то дайте намек - как это делать? Заранее спасибо! Валерий -

нужен монтажник, разовая работа (4 чипа+разъем)

vat ответил vat тема в Предлагаю работу

В заголовке я написал - Одинцово (Подмосковье). Часто бываю в Кунцево, на Филях, Беговой. Готов подъехать и в др.места, если не далеко от метро. Заказ готов удвоить (2 комплекта плюс доп.детали). Телефон выслал в личку. -

нужен монтажник, разовая работа (4 чипа+разъем)

vat ответил vat тема в Предлагаю работу

неужели никого нет? Работа на самом деле несложная. Пару сторон чипа я пропаял прилично менее чем за 5 минут. Потом только напартачил, когда снимал лишний припой оплеткой - ножки очень тонкие, погнулись и склеились. Неохота отдавать заказ в мастерскую по ремонту мобил. У них нет опыта с такими PQFP. Может есть кто недалеко от метро в других частях Москвы? Народ, спросите своих монтажников плиз, дайте им подхалтурить. Но только профи с опытом по данной теме, студенты и любители не подходят. -

нужен монтажник, разовая работа (4 чипа+разъем)

vat опубликовал тема в Предлагаю работу

Доброе время суток. Обычно свои протипы паяю сам, но недавно пришлось поменять паяльник и я им почти запорол большой чип FPGA (погнул и склеил ноги, потом еле-еле разогнул, но все вкривь и вкось). С ним собственно основная проблема. Корпус PQFP208, шаг 0.5мм, но не в этом дело - я такие паял всегда легко. Но у этого выводы длинные и тонкие как волоски, гнуться сами в любую сторону, даже поставить его трудно, чтобы все выводы стояли ровно. Для заказчика нужен красиво спаяный экземпляр, а у меня вышел уродец. До кучи можно поставить LQFP100 (0.5мм) и LQFP80(0.65мм), LQFP-48(0.5мм) и HDMI-19 (SMD разъем) - эти паяются легко, т.к. ноги жесткие. Т.е. всего 460 точек. Работа на часок-полтора максимум, расчет по исполнении. Я приеду с деталями и платой к вам в обговоренное время и дождусь завершения. Там еще много более мелких чипов и рассыпухи, но сначала мне надо протестировать эти основные. Так что возможен еще один визит. Если есть интерес, то назовите свою цену и где находитесь. Валерий.