=======================================================================

Xpedition Layout - Version 120.0.1628.2758

=======================================================================

Job Directory: C:\my_design_2\PCB\

Design Status Report: C:\my_design_2\PCB\LogFiles\DesignStatus_02.txt

Thu May 19 18:31:51 2022

=======================================================================

DESIGN STATUS

=======================================================================

Board Size Extents ............ 160 X 100 (mm)

Route Border Extents .......... 159.5 X 99.5 (mm)

Actual Board Area ............. 15,996 (mm)

Actual Route Area ............. 15,867.01 (mm)

Placement Areas: Name Available Required Required/Available

Entire Board 31,992 Sq. (mm) 16,135.86 Sq. (mm)50.44 %

Pins .......................... 3073

Pins per Route Area ........... 0.19 Pins/Sq. (mm)

Layers ........................ 8

Layer 1 is a signal layer

Trace Widths .......... 0.15, 0.2, 0.22, 0.5, 1

Layer 2 is a Positive Plane Layer with nets

GND

Trace Widths .......... 0.2

Layer 3 is a signal layer

Trace Widths .......... 0.15, 0.17, 0.2, 0.5

Layer 4 is a Positive Plane Layer with nets

VCC_AUX

VCC_BRAM

VCC_INT

VCC_MGTA

VCC_NEG

VCC_3V3

VCC_5V

VCC_12V

VTT_MGTA

Trace Widths .......... 0.15, 0.2

Layer 5 is a signal layer

Trace Widths .......... 0.15, 0.2, 0.23, 0.5

Layer 6 is a signal layer

Trace Widths .......... 0.15, 0.2, 0.26, 0.28, 0.5

Layer 7 is a Positive Plane Layer with nets

VCC_12V

VCC_3V3

Trace Widths .......... None.

Layer 8 is a signal layer

Trace Widths .......... 0.15, 0.2, 0.22, 0.25, 0.5

Nets .......................... 512

Connections ................... 2370

Open Connections .............. 0

Differential Pairs ............ 14

Differential Pair Names: $2N1342 $2N1343

$2N1344 $2N1345

$2N1346 $2N1347

$2N1349 $2N1475

$2N1350 $2N1351

$2N1352 $2N1353

$2N1354 $2N1355

$2N1356 $2N1357

$2N1358 $2N1359

$2N1360 $2N1361

$2N1362 $2N1363

$2N1364 $2N1365

$2N1366 $2N1367

$2N1368 $2N1369

Percent Routed ................ 100.00 %

Netline Length ................ 0 (mm)

Netline Manhattan Length ...... 0 (mm)

Total Trace Length ............ 33,176.37 (mm)

Trace Widths Used (mm) ........ 0.15, 0.17, 0.2, 0.22, 0.23, 0.25, 0.26, 0.28, 0.5, 1

Vias .......................... 1916

Via Span Name Quantity

1-8 TR0,4_0,2 1

TC0,4_D0,2 1296

TC0,6_D0,3_P 227

VC0.6_D0.3 392

Teardrops....................... 0

Pad Teardrops............... 0

Trace Teardrops............. 0

Custom Teardrops............ 0

Tracedrops...................... 0

Virtual Pins.................... 0

Guide Pins ..................... 0

Parts Placed .................. 671

Parts Mounted on Top ...... 295

SMD ................... 216

Through ............... 78

Test Points ........... 0

Mechanical ............ 1

Parts Mounted on Bottom ... 376

SMD ................... 311

Through ............... 65

Test Points ........... 0

Mechanical ............ 0

Embedded Components ........ 0

Capacitors ............. 0

Resistors .............. 0

RF Shapes .................. 0

Edge Connector Parts ...... 0

Parts not Placed .............. 0

Nested Cells .................. 0

Jumpers ....................... 0

Through Holes ................. 2393

Holes per Board Area ...... 0.15 Holes/Sq. (mm)

Mounting Holes ................ 7

Wirebonds

Bond Fingers ............... 0

Bond Wires ................. 0

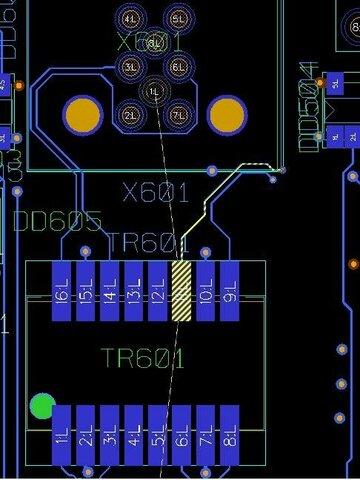

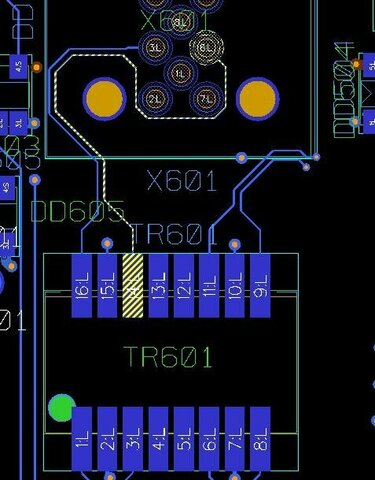

В общем разобрался. Не были поставлены необходимые галочки. Сбило с толку сообщение :"Percent Routed ................ 100.00 %"

Еще один вопрос.

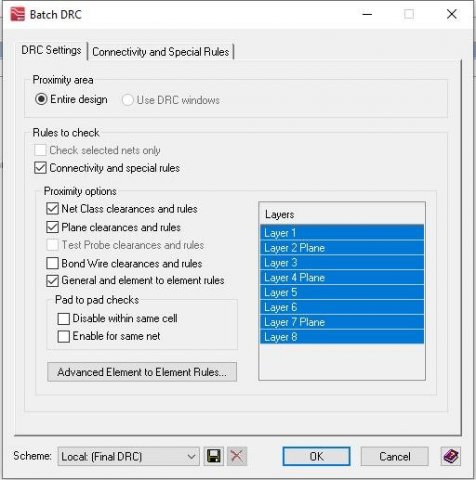

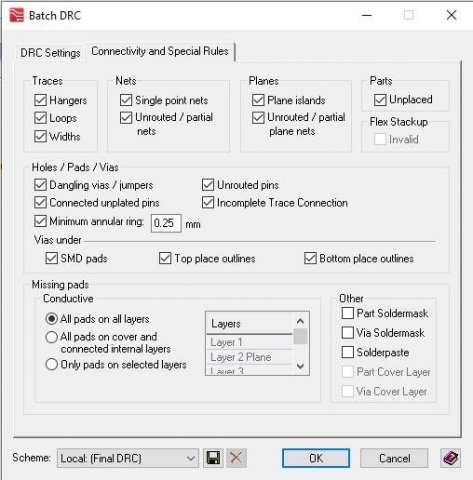

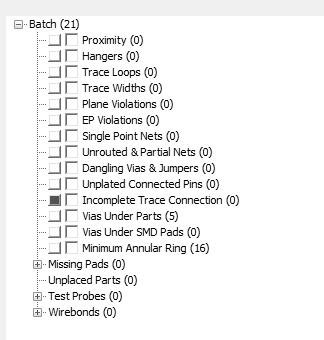

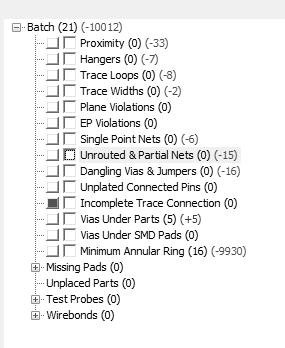

Когда несколько раз запускаю проверку DRC, после некоторых запусков вижу что в Hazard Explorer исчезают ошибки. При этом в скобках показаны количество ошибок которые удалены из сообщений. Что это такое и как этим пользоваться?

Как сделать так чтоб при запуске Batch DRC отображалась только актуальная информация?