-

Постов

622 -

Зарегистрирован

-

Посещение

-

По AD8353

Vladimir_T ответил Vladimir_T тема в RF & Microwave Design

Здравствуйте, причина отсутствия сигнала была в том, что был не пропаян вход! Плата с горячим лужением, видно пастой не пропаялась, после ручной пропайки - все пошло. Но вопрос согласования импедансов требует тщательного подхода... -

По AD8353

Vladimir_T ответил Vladimir_T тема в RF & Microwave Design

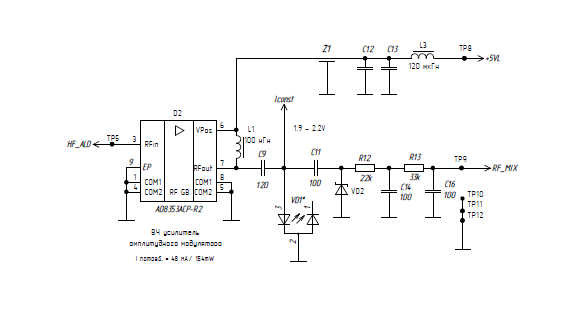

Вопрос согласования - это шибко сложный, параметры можно получить только косвенно. Сигнал Iconst задает постоянный ток 58 - 62 мА. Сигнал подается через дроссель, при отладке ВЧ-модулятора, она отпаяна. -

По AD8353

Vladimir_T ответил Vladimir_T тема в RF & Microwave Design

Благодарю за критику и желание помочь. Разделительный конденсатор по входу есть, он на выходе синтезатора ФАПЧ. Через фильтры - сигнал контроля. Фильтры - пока отрежу. Позже номиналы пересчитаю. Это же фотоника: симбиоз электроники, лазеров и фотоприемников. Поэтому лазеру нужен ВЧ-модулятор на ВЧ-усилителе. Многие решения из радиоприема применяются: гетеродинирование, смесители, обработка сигналов. Это все работает в образце, сделал сделал следующий вариант - получился пока нерабочий. -

По AD8353

Vladimir_T ответил Vladimir_T тема в RF & Microwave Design

Нельзя же быть таким категоричным... -

По AD8353

Vladimir_T ответил Vladimir_T тема в RF & Microwave Design

Благодарю за внимание к моему вопросу. Прикрепил файлы проекта. Плата 2-х сторонняя на обоих слоях сплошные полигоны. Два варианта плат сделаны, одна - как копия из КИТа, вторая для встраивания в узел, топологии однотипные. -

По AD8353

Vladimir_T опубликовал тема в RF & Microwave Design

Здравствуйте, уважаемые коллеги, подскажите по AD8353. Сделал плату, питание 5В, частота на входе 400 - 600 МГц, потребление в норме, трассировка из тех. описания. Сигнала на выходе - нет (есть автогенерация на уровне - 2МГц/ 100 мВ). В описании написано, что индуктивность не нужна (стр. 15). Figure 40 shows the schematic of the AD8353 evaluation board. Note that L1 is shown as an optional component that is used to obtain maximum gain only when VP = 3 V Что ей не хватает для работы? -

Про TIM8 STM32F722

Vladimir_T ответил Vladimir_T тема в STM

Благодарю за критику! Это только отладочный момент. Проект перетек из 4-го семейства на 7-е. На 4-м пользовался SPL. Для 7-го библиотеку SPL не нашел. Если есть, то пришлите ссылку. У TIM8 CH4 комплементарного выхода, потому регистр BDTR игнорировал, беспечность подвела. TIM8->BDTR |= TIM_BDTR_MOE; // Main output enable. OC output are enabled if their respective enable bits are set Теперь работает. -

Про TIM8 STM32F722

Vladimir_T ответил Vladimir_T тема в STM

C CubeMX также не работает. Думал, что комплементарность нужно настроить, но CubeMX тоже без нее обходится. -

Про TIM8 STM32F722

Vladimir_T опубликовал тема в STM

Здравствуйте, уважаемые коллеги, подскажите в чем может быть дело. Настраиваю TIM8 CH4 на выход через PC9, а на выходе сигнала нет. В отладчике KEIL проверил: периферия конфигурируется, таймер стартует, счет идет, но на выходе порта - сигнала нет. Какую еще инициализацию нужно TIM8 для формирования простого миандра? void MX_TIM8_Init(u32 Period) { htim8.Instance = TIM8; htim8.Init.Prescaler = 0; htim8.Init.CounterMode = TIM_COUNTERMODE_UP; htim8.Init.ClockDivision = TIM_CLOCKDIVISION_DIV1; HAL_TIM_Base_Init(&htim8): // RCC peripheral clock enabling TIM8->CR1 |= TIM_COUNTERMODE_UP; TIM8->CR1 |= TIM_CLOCKDIVISION_DIV1; TIM8->CCMR2 |= TIM_CCMR2_OC4M_0 | TIM_CCMR2_OC4M_1 | TIM_CCMR2_OC4M_2; TIM8->PSC = 0; TIM8->CCER |= TIM_CCER_CC4E; TIM8->ARR = Period; TIM8->CCR4 = Period / 2; TIM8->SR = 0x0000; HAL_TIM_MspPostInit(&htim8); TIM8->CR1 |= TIM_CR1_CEN; } // MX_TIM8_Init(void) void HAL_TIM_MspPostInit (void) { __HAL_RCC_GPIOC_CLK_ENABLE(); GPIO_InitStruct.Pin = GPIO_PIN_9; // PC9 ------> TIM8_CH4 GPIO_InitStruct.Mode = GPIO_MODE_AF_PP; GPIO_InitStruct.Pull = GPIO_NOPULL; GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW; GPIO_InitStruct.Alternate = GPIO_AF3_TIM8; HAL_GPIO_Init(GPIOC, &GPIO_InitStruct); } // HAL_TIM_MspPostInit (void) -

Вопрос по монтажу экранов на печатные платы

Vladimir_T опубликовал тема в Пайка и монтаж

Здравствуйте, уважаемые специалисты, в фирме "ПСБ - технологии" имеются экраны для ВЧ-модулей для пайке их на печатных платах. Это полезные изделия, но как их паять на плате (чем), а также требования к плате (посадочному месту) - нигде не найду: 1. Можно ли паять их в туннельной печи вместе с остальными компонентами на пасту? 2. Возможно ли их паять экраны легкоплавким припоем после настройке модуля феном? 3. Возможно ли их паять экраны жидким припоем (галистаном) после настройке модуля? Пробные эксперименты подтвердили эту идею, но прочность соединения - не высокая. Заранее благодарен за советы из практики и статьи. -

Какие они молодцы! Далеко продвинулись. А я буду пробовать установить управляемую транзистором нагрузку для ЛФД. Должно получиться, по результатам напишу.

-

Благодарю за ответы. Разварить ТИУ вместе с кристаллом ЛФД мне не осилить, а без этого приема у меня ТИУ возбуждался, ведь приходится работать с полезным сигналом на уровне темновых токов ЛФД. Поэтому принята схема оптоэлектронного смесителя: принимается модулированный сигнал, подводится сигнал гетеродина (1 - 1.2 ГГц), а на выходе сигнал ПЧ (100 кГц). Поэтому при грамотном согласовании ЛФД с нагрузкой, думаю, что удастся поднять уровень полезного сигнала ПЧ. Сам ЛФД имеет емкостной характер, думаю, что если его скомпенсировать, тогда на нагрузке сигнал бы вырос ?!

-

Видимо я не четко сформулировал вопрос. Мне нужно согласовать ЛФД, на которые нет рекомендаций, в отличие от HSMS-286.

-

Благодарю за статью, но без регистрации ее не дадут прочесть.

-

Как правильно нагрузить лавинный фотодиод?

Vladimir_T опубликовал тема в RF & Microwave Design

Здравствуйте, уважаемые коллеги, фирма Avago для своих диодов HSMS-286 приводит наглядные примеры для согласованных нагрузок детекторов на этих диодах. Когда лавинный фотодиод (ЛФД) работает в качестве оптоэлектронного смесителя, при работе с малыми оптическими (ВЧ-модулированными) сигналами, очень важно точно согласовать его с нагрузкой, чтобы получить максимальный полезный сигнал. Нет ли статей, чтобы разработать управляемую нагрузку для компенсации реактивной составляющей ЛФД?