Поиск

Показаны результаты для тегов 'lengh matching'.

-

Выравнивание длинн проводников для углового разъема DVI

mitro опубликовал тема в Схемотехника

Добрый вечер! Понадобилось сделать плату - переходник от FPGA Development board (разъем IDC-40) на DVI. Предполагается передавать данные lvds-ом, 4 дифференициальных бита данных, один дифференциальный такт. Хотел при разводке выравнять длины проводников. Но у меня вопрос - а что делать с угловым разъемом DVI? Таким, как на рисунке. У него же, наверное, разная длина проводника от пина до разъема для разных рядов? Как это учитывать? Где найти эту информацию (длины для разных рядов?). Или он так сделан, что длины одинаковые???- 13 ответов

-

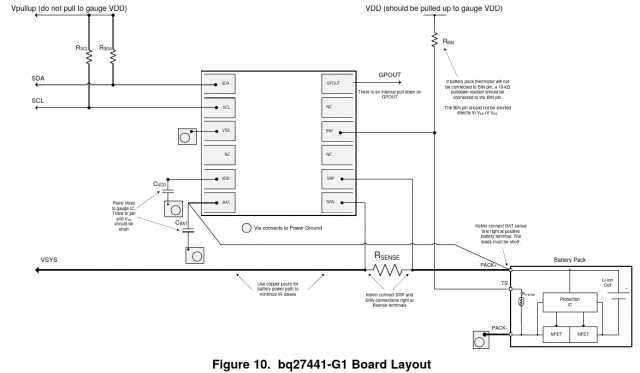

Всем привет! Возник вопрос, можно-ли в Expedition автоматически проконтролировать отдельные длины цепей для отдельных Pin pair в цепях питания? Эта задача связана с разводкой цепей подключения шунта для микросхемы fuel gauge LiPol аккумулятора. Пример схемы: Линии подключения к контактам SPR/SRP должны иметь равную длину. Т.е. длины отрезков цепей для Pin pair SPR-Rsense(1) и SPN-Rsense(2) должны быть равны. Цепи VSYS и PACK+ на плате разводятся с использованием полигонов и определены в CES как Power-цепи. При этом, как я понимаю, задать Pin Pair для этих цепей возможности нет. Ок, думаю я, делаем их обычными цепями, задаем Custom тип топологии, автоматически создаем пары пинов в CES и формулу для обеспечения равенства длин указанных пар пинов. Но почему-то после Data=>Actuals=>Update All никаких Formula Violation не выдается, в редакторе PCB в Hazards тоже нет предупреждений о нарушении требований выравнивания длин. Я пробовал повторить этот эксперимент с другими цепями проекта, без полигонов, и для них правила выравнивания длин между парами пинов, заданные через формулу, применяются и при нарушениях выдаются Hazards и отображаются Violations в CES. Поэтому основная гипотеза в том, что обнаруживая полигоны Expedition считает эту цепь "не совсем сигнальной" и перестает контролировать длины. Может быть я что-то делаю не так и есть способ контролировать подобные цепи? Или всё только вручную?

- 39 ответов