Поиск

Показаны результаты для тегов 'цикл рекурсии архитектуры'.

-

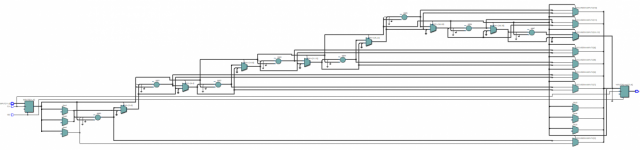

Мотивация проста, в архитектуре DSP блоки конечны и приходится ловчить... Получил(заимствовано из интернета) в лоб архитектуру на 12 разрядов, которая изначальное, чисто комбинационно, достаточно симпатична в RTL просмотре, но как следствие,- медленная. Вставить регистр на половине структуры в имеющейся парадигме проблемно. Как бы это сделать изящнее? --^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^ -- FILE: SQRN.VHD -- PROJECT: Square Unit -- AUTHOR: Anatoli Sergiyenko -- Email: [email protected] -- FUNCTION: - calculating the square function https://kanyevsky.kpi.ua/ru/статьи/вычисление-квадрата/ -- from the STD_LOGIC_VECTOR, -- which represent the natural integer data. -- CONSTRAINTS: the input data bit number is equal to -- bit_num, where bit_num >4 is a generic value, -- the output data bit number is equal to 2*bit_num, -- respectivelYYPUT. --^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^ library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_ARITH.all; entity SQRN is generic(bit_num: integer:=12); port(CLK: in STD_LOGIC; RST: in STD_LOGIC; XXPUT:in STD_LOGIC_VECTOR(bit_num-1 downto 0); YYPUT:out STD_LOGIC_VECTOR(bit_num*2-1 downto 0)); end entity SQRN; architecture STR of SQRN is signal XXPUTR:STD_LOGIC_VECTOR(bit_num-1 downto 0); signal XXPUT0:STD_LOGIC_VECTOR(3 downto 0); signal YYPUT0:STD_LOGIC_VECTOR(7 downto 0); signal XXPUT2:STD_LOGIC_VECTOR(2*bit_num-1 downto 0); begin XXPUT_REGISTER: process(CLK,RST,XXPUT) begin if RST='1' then XXPUTR<=(others=>'0'); elsif CLK='1' and CLK'event then XXPUTR<=XXPUT; end if; end process; --initial square function XXPUT0<=XXPUTR(3 downto 0); SQR4:process(XXPUT0) begin case XXPUT0 is when "0000"=> YYPUT0<="00000000"; when "0001"=> YYPUT0<="00000001"; when "0010"=> YYPUT0<="00000100"; when "0011"=> YYPUT0<="00001001"; when "0100"=> YYPUT0<="00010000"; when "0101"=> YYPUT0<="00011001"; when "0110"=> YYPUT0<="00100100"; when "0111"=> YYPUT0<="00110001"; when "1000"=> YYPUT0<="01000000"; when "1001"=> YYPUT0<="01010001"; when "1010"=> YYPUT0<="01100100"; when "1011"=> YYPUT0<="01111001"; when "1100"=> YYPUT0<="10010000"; when "1101"=> YYPUT0<="10101001"; when "1110"=> YYPUT0<="11000100"; when "1111"=> YYPUT0<="11100001"; when others => null; end case; end process; --calculating the recursion RECURSION:process(XXPUTR,YYPUT0)is variable XXPUT2I: STD_LOGIC_VECTOR(2*bit_num-1 downto 0); variable Varble:STD_LOGIC_VECTOR(bit_num-1 downto 0); variable SM1:STD_LOGIC_VECTOR(bit_num-1 downto 0); variable aaa:STD_LOGIC; variable iii: integer; begin XXPUT2I:=(others=>'0'); XXPUT2I(7 downto 0):=YYPUT0; for iii in 1 to bit_num-4 loop Varble(iii+2 downto 0):= XXPUTR(iii+2 downto 0); aaa:=XXPUTR(iii+3); if aaa='0' then SM1(iii+3 downto 0):= "00"&XXPUT2I(2*iii+5 downto iii+4); else SM1(iii+3 downto 0):= UNSIGNED('0'& aaa & XXPUT2I(2*iii+5 downto iii+4)) + UNSIGNED(Varble(iii+2 downto 0)); end if; if iii /= 5 then --вставка попытка PUN_REG: XXPUT2I(2*iii+7 downto iii+4):=SM1(iii+3 downto 0); else PUT_REG: process(CLK) begin if CLK='1' and CLK'event then XXPUT2I(2*iii+7 downto iii+4):=SM1(iii+3 downto 0); end if; end process PUT_REG; -- XXPUT2I(2*iii+7 downto iii+4):=SM1(iii+3 downto 0); --было вначале end if; end loop; XXPUT2<=XXPUT2I; end process; YYPUT_REGISTER: process(CLK,RST,XXPUT2) begin if RST='1' then YYPUT<=(others=> '0'); elsif CLK='1' and CLK'event then YYPUT<=XXPUT2; end if; end process; end architecture STR; Что я только не пробовал! ...или туплю? Спасибо!!! Вот так выглядит изначальное построение, где необходимо, как минимум, поместить регистр...