IgorMov

-

Постов

14 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные IgorMov

-

-

11 hours ago, _4afc_ said:

Выпишите из матлаба в файл нужные вам заголовки и коэффициенты в нужном формате печатью в файл.

Я так и сделал, но мой вопрос все равно к Xilinx остается:

Но как то странно в Vivado или в Xilinx нет нормального creator и/или преобразователь bin2coe или hex2coe... -

MatLab c помощью функции coewrite что-то похожее попрождаеь, но IP Memory Generator ругается на этот формат.

Ему нужен заголовок:

memory_initialization_radix=10;

memory_initialization_vector=

0,

1,

...Но как то странно в Vivado или в Xilinx нет нормального creator и/или преобразователь bin2coe или hex2coe...

-

Кто нибудь может помочь с созданием *.coe файла для инициализации ROM в Vivado, Xilinx?

Из hex, bin или из MatLab. В MatLAb есть функция "coewrite", но то чтор она прождает Vivaldo "не нравится". -

6 minutes ago, MegaVolt said:

Вот букварик по памяти.

http://cdn.gowinsemi.com.cn/UG285E.pdf

На счёт 2:0 это и есть 8 слов как вы и запросили.

Если хотите чтобы было 7:0 просите 256 слов ширину памяти.Спасибо. Да в самом деле "Address depth" это не количество бит в шине адреса, как в "Data Width", а количество слов "Data Width".

-

Всех приветствую.

Может кто-нибудь подскажет, как корректно создать простой блок памяти 8 адресов, 8 бит данных в Gowin?

GOWIN FPGA Designer Version 1.9.8.05 build(57076). _Tools > IP Core Generator > Memory > Block Memory > SP 1.0

Address Depth:8 Data Width: 8Получается

//--------Copy here to design--------

test_RAM_ad8b_d8b your_instance_name(

.dout(dout_o), //output [7:0] dout

.clk(clk_i), //input clk

.oce(oce_i), //input oce

.ce(ce_i), //input ce

.reset(reset_i), //input reset

.wre(wre_i), //input wre

.ad(ad_i), //input [2:0] ad

.din(din_i) //input [7:0] din

);//--------Copy end-------------------

Почему " .ad(ad_i), //input [2:0] ad" , а не [7:0] ? Вроде, 1 блок памяти 18Kb...

-

Спасибо за информацию. Похоже пробился и получилось просиммулировать.

Основное, что я хотел провести симмуляцию без Квартуса.

Первый шаг попробовал с квартусом. Болше помогла ссылка https://adelectronics.ru/2018/06/03/запускаем-modelsim-с-quartus-prime-и-без/ (спасибо new123).

Тоже пришлось осуществить танцы с бубнами. Почему то при запуске МоделСима из под Квартуса,МоделСим не находил файл с моим созданным pll *.vo. Этот файл был в другом каталоге, не там где его искал МоделСим. Перенес в тот и заработало.

После этого шага я понял, что кроме файла моего pll *.v нужен еще *.vo.

Вернулся к работе в МоделСиме без квартуса добавил в проект файл *.vo. Все равно МоделСим не компилирует и ругается:

# ** Error: (vsim-3033) D:/svn/ModelSim/tmp/pllTestNew/pll200MHz.vo(46): Instantiation of 'altera_pll' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /pll200MHz_tb/pll200MHz_inst File: D:/svn/ModelSim/tmp/pllTestNew/pll200MHz.vo

# Searched libraries:

# C:/intelFPGA/17.0/modelsim_ase/altera/vhdl/altera_mf

# D:/svn/ModelSim/tmp/pllTestNew/work

Тогда я рещил поискать, а где же этот либ элемент 'altera_pll'. Начинаю поиск в моем МоделСимовском каталоге c:\intelFPGA\17.0\modelsim_ase\altera\ текста 'altera_pll' и нахожу в каталогах \altera_lnsim\.

Снова запускаю симуляцию и добавляю либ altera_Insim и все стало симмулироваться.

Еще раз спасибо new123 и des00

-

Да. Вы правы. Я не написал, что модел сим у меня не соответствовал Quartus Lite 17.0. Поставил моделсим, который соответствует. Те же ошибки

# ** Error: (vsim-3033) D:/svn/ModelSim/ml/adcLtc2387/pll_newModelSim/pll200MHz_0002.v(78): Instantiation of 'altera_pll' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /pll200MHz_tb/pll200MHz_inst/pll200mhz_inst File: D:/svn/ModelSim/ml/adcLtc2387/pll_newModelSim/pll200MHz_0002.v

# Searched libraries:

# C:/intelFPGA/17.0/modelsim_ase/altera/vhdl/altera_mf

# D:/svn/ModelSim/ml/adcLtc2387/pll_newModelSim/work

# Error loading design

Т.е. без квартуса, как я работал раньше, cиммулировать отдельно в моделсиме с pll из IP catalog не получится. Изучаю ваши ссылки. Зараннее спасибо. -

Как я понимаю, простым копированием файлов .v .sv и созданием нового отдельного проекта в МоделСиме с использованием pll, созданного в IP catalog не получится.

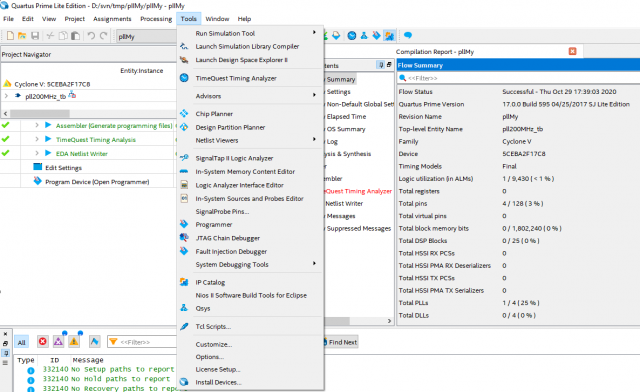

Вернулся к проекту в Квартусе. Согласно вашей ссылке выполнил п.1.2 и начал выполнять п.1.3. Processing > Start Compilation выполнил. Пытаюсь выполнить Tools > Generate Simulator Setup Script for IP. В моем Quartus Prime Version 17.0.0 Build 595 04/25/2017 SJ Lite Edition не вижу Tools > Generate Simulator Setup Script for IP. Десктоп квартуса:Пытался попробовать разобраться с примером из

https://www.intel.com/content/www/us/en/programmable/support/support-resources/design-examples/design-software/simulation/modelsim/exm-pll-simulation.html

Но там проект для Stratix II. А мой Quartus Prime Version 17.0.0 Build 595 04/25/2017 SJ Lite Edition не поддерживает...

Error (20005): Cannot compile your design for one of the devices in the Stratix II family of devices. A license file is required

-

"C:/intelFPGA_pro/18.1/modelsim_ase/altera/verilog/altera_mf"

Да есть

Моделсим открываю отдельно от квартуса.

Создаю для проекта testbench. В отдельную папку копирую файлы для pll (созданные в квартусе).

В квартусе в папке \simulation\modelsim\ создаются файлы.

Требуется в моделсиме проверить логическую работоспособность проекта с pll. Для проектов со старыми чипами типа Cyclone III, достаточно было скопировать pll верилоговский файл созданный старым квартусом 13.0 (мегавизард) и все без проблем симмулировалось в моделсиме.

-

Пытаюсь симмулировать проект в ModelSim Altera c PLL. Проект для Cyclone V E. Файлы для симмулирования PLL созданы MegaWizard c помощью Quartus Prime Lite из каталога: Installed IP>Library>Clocks,...>PLL>Altera PLL.

При симуляции ModelSim ругается:

# Start time: 14:23:36 on Oct 26,2020

# Loading sv_std.std

# Loading work.pll200MHz_tb

# Loading work.pll200MHz

# Loading work.pll200MHz_0002

# ** Error: (vsim-3033) D:/svn/ModelSim/ml/adcLtc2387/pll/pll200MHz/pll200MHz_0002.v(78): Instantiation of 'altera_pll' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /pll200MHz_tb/pll200MHz_inst/pll200mhz_inst File: D:/svn/ModelSim/ml/adcLtc2387/pll/pll200MHz/pll200MHz_0002.v

# Searched libraries:

# C:/intelFPGA_pro/18.1/modelsim_ase/altera/vhdl/altera_mf

# C:/intelFPGA_pro/18.1/modelsim_ase/altera/verilog/altera_mf

# D:/svn/ModelSim/ml/adcLtc2387/pll/work

# Error loading design

# End time: 14:23:36 on Oct 26,2020, Elapsed time: 0:00:00

# Errors: 1, Warnings: 0Похоже, что нужно подключить еще какую-нибудь альтеровскую библиотеку или PLL создать, как то по другому.

Но после симмуляции необходимо скомпилировать в Quartus Prime Lite. -

14 hours ago, DmitryR said:

Power Estimator даёт быстрый и относительно точный ответ. У меня в проектах больше пары PLL никогда не использовались, поэтому на 2,5В хватало крошечного LDO.

DmitryR спасибо. Power Estimator еще не освоил. Да и проект полностью еще не готов. Но больше пары PLL использовать не планирую.

-

т.е. раз в мануале написано, что ноги VCCA_FPLL, VCC_AUX, VCCBAT надо подключать к 2,5В, то так и надо делать. От 3,3В могут быть проблемы. А может у кого то есть опыт или информация: Какое потребление по этим ногам "питания", которые функционально в проекте не учавствуют?

-

В проекте используется чип Альтеры CycloneV E 5CEBA4F17. Трансиверы и никакой другой экзотики не используются. Можно ли запитать микросхему только 1,1В и 3,3В. По датащиту, даже если не используется, надо запитать VCCA_FPLL, VCC_AUX, VCCBAT на 2,5В. Можно ли запитать эти ноги на 3,3В? Очень не хочется устанавливать дополнительное питание... Если все таки надо, кто поделиться информацией о потреблении по этим ногам? VCCIO по всем банкам планируется подключить к 3,3В.

Xilinx создание coe file

в Языки проектирования на ПЛИС (FPGA)

Опубликовано · Пожаловаться

coe файл в Xilinx это данные инициализации памяти ROM. У меня это не коэффициенты фильтров, а управляющие биты, которые формируются не в МатЛабе.