Al_Jumper

-

Постов

79 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Al_Jumper

-

-

До 30 шт.

Возможно еще ICX249AL подойдут.

Вариант Б/У тоже рассмотрю.

-

Куплю ATMega64A-MU или ATMega64L-8MU

Нужны именно в корпусе QFN

С окончанием MQ тоже подойдут.

-

Куплю ПЛИС Xilinx XC6SLX9-2CSG225 (-3 тоже подойдут, С или I) новые или БУ, можно даже запаянные в плату. Главное рабочие. До 20 шт.

-

1 hour ago, Raven said:

Так чему удивляться, если вы отказались провернуть имплементацию (но не синтез) с только что внесенными изменениями (по добавлению вывода сигнала на пин). В этом месте надо было позволить имплементировать заново.

Пробовал.

И тогда VIVADO начинает имплементацию с начала. Опять 30 минут ждать чтобы вытащить одну цепь на пин.

Это жесть... В ISE-шном FPGA Editor'е это занимало считанные секунды.

Неужели по-другому никак?

Ведь, как я понимаю, когда скрипт отработал, цепь уже выведена на пин, т.е. разводка уже сделана.

Нужно только сгенерировать битстрим из нее. Или я ошибаюсь?

4 hours ago, andrew_b said:Спасибо, буду вникать...

-

Всем доброго времени суток.

Начинаю осваивать VIVADO, поэтому заранее извиняюсь за возможно чайницкий вопрос.

Дизайн отстнтезирован, имплементирован и получен bitstream.

Хочется вытащить внутренний сигнал на свободный пин и посмотреть осциллом.

Нашел, что для этого есть скрипт add_probe, установил его, и, вроде, он работает.

Команда выглядит так:

xilinx::debugutils::add_probe -net datapath_inst/iserdes_array_inst/iserdes_sync_ch1/data_in_from_pins_int -port PR_F5 -iostandard LVCMOS25 -loc F5

В device view я вижу, что мой сигнал приходит на нужный пин.

Дальше надо генерить новый bitstream.

При нажатии кнопки "generate bitstream" выдается сообщение что надо сохранить проект - соглашаюсь.

Дальше почему-то предлагается сохранить файл констнейнов .xdc, хотя я его не менял.

Соглашаюсь - других вариантов нет.

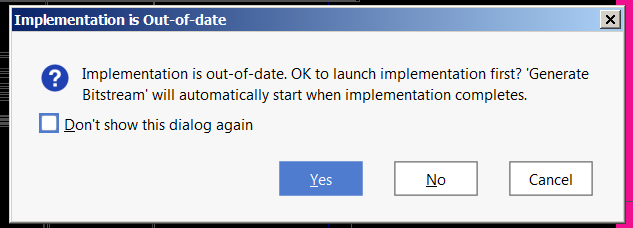

Дальше вот такое сообщение:

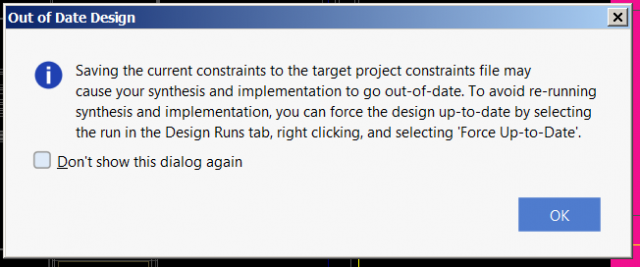

Жму ОК. Дальше выдается:

Закрываю это сообщение и делаю, что говорят - Force Up-To-Date (если этого не сделать, то синтез и имплементация начинаются заново)

Дальше снова жму "generate bitstream"

Выдается

Жму ОК.

Дальше запускается генерация bitstream'а и вроде бы все - бинго!

Однако, после загрузки в ПЛИС (Artix 7) выясняется что в полученном bitstream'е на мой пин F5 ничего не вывелось, он ведет себя как вход...

ВОПРОС - ЧТО Я ДЕЛАЮ НЕ ТАК?

Заранее благодарю за ответы.

-

У меня библиотеки криво становятся. На верилоге не хочет компелироваться, не могу понять в чём дело

А что говорит?

Мне помогло вот что. Запустил менеджер библиотек, выбрал нужную (Spartan6) и по правому клику - Refresh Library. После этого перестал ругаться, что Incompatible format.

-

1. взять сорцы из 14.3, закатать поверх, подправить скрипты сборки и перекомпилировать как отдельные проекты.

2. compxlib

но вообще тема обсуждалась кучу раз

Сорри за чайницкие вопросы, но пока я в затыке.

Прочел инструкцию на сайте у них как это делать на примере unisim.

В папке vlib\unisim\src есть скрипт update_unisim.do.

Открываешь либу как проект в Активе, запускаешь этот скрипт - и вуаля. Готово.

НО. Такой скрипт не во всех папках с либами есть. Например в папке Spartan6 его нет.

Хотел написать сам, но, посмотрев на скрипт из папки Xilinxcorelib, понял, что надо описывать компиляцию каждого элемента библиотеки а их там ....

Спасибо заранее.

-

Подскажите. Нужны либы для ISE 14.3. На местном FTP нету. Или подскажите как правильно перекомпилировать старые (от 9.1) чтоб работали.

-

Проект успешно перевелся, вот сижу альдек изучаю, если я правильно понял то теперь мне вести разработку схемы в альдеке а потом как то импортировать проект в Xilinx ISE? у вас нету ссылки с примерами или какого то руководства как это можно реализовать?

Экспортировать в ISE едва-ли получится. Там есть экспорт только в HTML и PDF. Да и надо-ли? Схемный редактор ISE по-моему намного менее удобен, чем в Активе.

и еще вот вопрос могу ли я свой проект из Foundation который я перевел на альдек транслировать из альдека для плис ACTEL. не могу просто понять как это происходит ведь у нас проект использует библиотеки Foundation... извиняюсь за глупые вопросы.Не знаю, с ACTEL не работал. В Активе есть возможность автоматической замены элементов из одной библиотеки на другую (Design->Change Library). Но названия элементов должны совпадать в обоих библиотеках.

-

Он импортирует проект Foundation целиком. Любая версия это умеет. Предполагаю, что для последних версий в библиотеках (скачиваются с сайта Алдека) не будет Spartan2, но большинство схемных элементов с тех пор не поменялись. Проблемы возникали только с элементами, созданными с помощью LogiBlox. Они вставляются в импортированный проект как Edif-модули, и модифицировать их уже невозможно. Я их переписывал на Верилоге.

-

В ISE Вы схемы автоматически не перенесете. Только если перерисовывать. Можно попробовать Acтive НDL. От понимает схемные файлы Foundation. Только при инсталляции его надо не забыть поставить галку "Аctive-cad import". Только тогда уже придется работать с проектом в нем, а ISE использовать только для имплементации.

-

Объект - диэлектрик (стекло), поэтому индукционный датчик не подойдет. Пролетает в трубке диаметром 10 мм. Измерять ничего не нужно, надо только засечь пролетание. Если работать на отражение, то буду ловить отражение от стенки. Конечно можно (и, видимо, придется) делать в трубке щель или даже разрывать ее на насколько мм. О линзе думал, но как то это сложно все. Проще несколько фотодиодов поставить. Опыта в таких вещах мало, занимаюсь в основном цифрой. Пока экспериментирую с одним фотодиодом. Операционник в качестве усилителя. Получается плохо, очень зависит от фоновой засветки.

Делать модулированный осветитель и фильтр после фотодатчика? Может как-то проще можно?

-

Необходимо создать датчик пролета объекта размером 1-6 мм через зону контроля сечением 10х10 мм. Скорость объекта - до 3 м/с. Первое, что приходит в голову - щелевой осветитель на линейке светодиодов и приемник из линейки фотодиодов. Подскажите, может существуют фотодиоды с прямоугольной геометрией или какие-то еще готовые решения. Есть ли какие-то рекомендации по схемотехнике усилителей сигнала с фотодиодов, позволяющие повысить надежность срабатывания? Заранее спасибо.

-

В этом всё и дело. Так что дальнейший вопрос: есть ли в закромах ломанный synplify с floating license? Что посоветуете?

Откройте свой файл лицензии и посмотрите, есть ли в списке

VENDOR_STRING=.....

слово batch. Если нет, то добавьте. Мне помогло.

-

Есть 2 задачи:

1. Необходимо разработать или найти что-то готовое для создания мини-цветомузыки на светодиодах, подключаемой на колонки МР3-плеера. Устройство должно быть портативным (носимым). Тираж 160 шт, срок -1 месяц

2. Сделать дистанционный беспроводной включатель автомобильного вентилятора (12В 10А). Расстояние - до 5 м (прямая видимость), возможны варианты радио или на ИК лучах. Тираж 42 штуки, срок 3 недели.

С предложениями и вопросами обращаться по мейлу skakun49{@}mail.ru (фигурные скобки убрать)

-

Да, со 128 тоже такая проблема была, но там заметил четкую закономерность - проц не любит быстро растущий VCC. С SUT экспериментировал с разными - безрезультатно. На клок грешить на приходится. Генератор питается от того же источника. Пробовал с кварцем. Только с внутренним RC еще не пробовал. Попробую, но, предполагаю, что ничего не даст. Самое неприятное то, что источник питания находится в системе заказчика, и какое там будет нарастание неизвестно. В общем, похоже, придется сделать что-то похожее на то, что Вы предлагаете с внешним ключом по питанию.

-

Он не только генерит ресет, но и удерживает его, пока не установится нормальное питание (должен по идее), не допуская вставание "враскорячку"

На MSP430 подобная проблема решилась установкой внешнего супервизора на правильное напряжение

Даже если держать ресет вручную (кнопкой) на время поднятия питания с большим запасом, то все равно то же самое. Зависит только от скорости нарастания VCC. Внешний супервизор есть, уже писал, что ресет поднимается через 100 мс после установки питания. Клок от внешнего генератора, его амплитуда тоже устанавливается с запасом раннее, чем отпускается ресет.

-

А какой генератор используете, может он не запускается?

И как определили, что проц встал в раскорячку? Может, он в бутлоадер влез, а вы там ничего не написали?

Лучше всего, конечно, такие ситуации с эмулятором отлавливать. У меня сейчас xmega32 + JTAGICE mkII прекрасно отслеживают пропадание и включения питания проца. При включении программа идет по вектору ресета (у меня в бутлоадер), так ставим брекпойнт и рассматриваем ситуацию!

Враскорячку, потому чтот ни на ресет ни на попытки обмена с компом по ISP (через AVREAL) он не реагирует. Бутлоадер у меня не используется - отключен фузами. JTAG тоже не используется и отключен.

-

Попробовать встроенный bod ?

Пробовал - бесполезно. BOD генерит RESET , а ресетом процессор из этого раскоряченного состояния не выводится. Никаким. Пока напрашивается только решение сделать ключ, подающий питание на МЕГУ уже после того, как VCC установилось. Но это означает переразводку платы, чего не хотелось бы.

-

При времени нарастания питания от 0 до 3.3В порядка 10-20 мс МЕГА встает враскорячку, не отзывается по ISP и вообще не подает признаков жизни. Ресет хороший, генерится стабилизатором TPS70158, поднимается резко примерно через 100 мс после достижения VCC 3.3 В. При резком нарастании VCC (~1мс) все нормально. При совсем медленном (1-2 секунды) - тоже. Кто с таким сталкивался - HELP!!!

Раньше с мегой103 такого никогда не было.

Раньше с мегой103 такого никогда не было. -

вопрос

Есть 16 входных сигналов - они могут быть расставлены на 16 выводов. Выводы заданы жёстко, а вот расстановка не имеет значения

можно-ли сделать её автоматом, по критерию занимания меньше ресурсов?????

У XILINX для этого достаточно перчислить в UCF номера пинов через запятую. Вот пример (шина адреса):

NET "MA<0>" LOC = p57, p58, p59, p60, p61, p62, p63, p64, p67, p68, p90, p93, p94, p95, p96, p97, p98, p99, p101;

NET "MA<1>" LOC = p57, p58, p59, p60, p61, p62, p63, p64, p67, p68, p90, p93, p94, p95, p96, p97, p98, p99, p101;

NET "MA<2>" LOC = p57, p58, p59, p60, p61, p62, p63, p64, p67, p68, p90, p93, p94, p95, p96, p97, p98, p99, p101;

......................................

NET "MA<18>" LOC = p57, p58, p59, p60, p61, p62, p63, p64, p67, p68, p90, p93, p94, p95, p96, p97, p98, p99, p101;

-

9.6 наконец стал нормально поддерживать INIT для регистров и SRL16 - теперь он транслирует значения INIT в нетлист.

-

Если Ваша задача оттащить USB2 устройстово на десятки-сотни метров от компа то советую посмотреть здесь:

www.icron.com

www.adnaco.com

Правда, там со стороны компа не GigE, а свои устройства.

-

Такая запись

wire save_clk = ((state == READ) && (nextstate == IDLE));

означает, что положительный фронт save_clk сформируется при переходе автомата В состояние READ (когда у Вас данные из памяти еще не считались),

а когда автомат из него выйдет в IDLE , возникнет как раз отрицательный фронт.

Поэтому логичным кажется следующее:

always @(negedge save_clk or negedge sys_rst)

begin

if (!sys_rst) data_bus_out <= 0;

else data_bus_out <= data_out;

end

Но, вообще, так лучше не делать, а, как Вам уже посоветовали, иметь в системе один тактовый сигнал, а логикой формировать разрешение записи.

Куплю СНП401-16ВП21-4-1 или аналог HARWIN M80-50016xx

в Куплю

Опубликовано · Пожаловаться

Куплю СНП401-16ВП21-4-1 или аналог HARWIN M80-50016xx

Подойдут также СНП401-16ВП31-4-1 или HARWIN M80-53016xx