Lutovid

-

Постов

165 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Lutovid

-

-

Всем привет. Возник вопрос при использовании векторных генераторов разных производителей. Есть такая опция генерации AWGN. И у этой опции зачастую есть параметр полосы. То есть мы можем ограничить полосу генерируемого шума.

стр. 311 Scalable low-pass filters are used to produce a noise power with both a broad dynamic range and a broad bandwidth range (from 1 kHz to 60 MHz).

И я не понимаю, что это за фильтр такой, который может от 60MHz до 1kHz менять свою полосу пропускания еще и с маленьким шагом. То есть вот у нас есть AWGN с плоским спектром от -Fs/2 до Fs/2, мы хотим от него получить например 1/60000 часть. Я не супер про в этой области, но мне знакомы такие варианты: 1)FIR интерполятор - для случая узкой полосы будет неадекватно много коэффициентов. 2)CIC интерполятор - разоримся на FIR компенсаторе. 3)Farrow на основе интерполяции Лагранжа - мой первый опыт с ним в моделях - матлаб позволяет максимум 4 порядок для своей внутренней функции, в итоге получается АЧХ с боковиками на 30дБ ниже основного колокола + в итоге полученный шум будет иметь далеко не прямоугольный спектр. При чем это как для 3, так для 4 порядка.

clear all close all frc = dsp.FarrowRateConverter(); frc.PolynomialOrder=3; frc.InputSampleRate = 3; frc.OutputSampleRate = 7; figure; [h,f] = freqz(frc); plot(f,20*log10(abs(h))) hold on frc.PolynomialOrder=4; [h,f] = freqz(frc); plot(f,20*log10(abs(h))) frc.PolynomialOrder=2; [h,f] = freqz(frc); plot(f,20*log10(abs(h)))

4)Какая-то хитрая схема ФВЧ+DDS+ФНЧ+DDS, но я что-то не пойму как эту схему сделать гибкой и чтоб зеркала не вылезли.

Мне слабо верится, что это как-то решается аналоговыми перестраиваемыми YIG фильтрами например.

Буду рад любой полезной информации, спасибо!

-

Кто искал ответ на тот же вопрос что и я - в примере выше dma, но с fifo то же самое

-

https://lwip.fandom.com/wiki/Network_interfaces_management

Как я понимаю если у нас есть уже один рабочий netif, то его не должно выбивать добавление нового

Но я вижу обратное

static struct netif server_netif; static struct netif server_netif2; struct netif *echo_netif; struct netif *echo_netif2; XUartLite UartLite; struct ip_addr ipaddr, netmask, gw; struct ip_addr ipaddr2, netmask2, gw2; /* the mac address of the board. this should be unique per board */ unsigned char mac_ethernet_address[] = { 0x00, 0x0a, 0x35, 0x00, 0x01, 0x02 }; unsigned char mac_ethernet_address2[] = { 0x00, 0x0a, 0x35, 0x00, 0x01, 0x03 }; void ProcUartCommand(u8 inp) { if(inp == '1') { xil_printf("adding netif\n\r"); if (!xemac_add(echo_netif2, &ipaddr2, &netmask2, &gw2, mac_ethernet_address2, XPAR_AXI_ETHERNET_1_BASEADDR)) { xil_printf("Error adding N/W interface\n\r"); } } } int main() { u8 UARTRecvBuffer[UART_BUFFER_SIZE]; u8 ReceivedCount = 0; XUartLite_Initialize(&UartLite, XPAR_UARTLITE_0_DEVICE_ID); echo_netif = &server_netif; echo_netif2 = &server_netif2; /* Define this board specific macro in order perform PHY reset on ZCU102 */ init_platform(); /* initliaze IP addresses to be used */ IP4_ADDR(&ipaddr, 192, 168, 7, 10); IP4_ADDR(&netmask, 255, 255, 255, 0); IP4_ADDR(&gw, 192, 168, 7, 1); IP4_ADDR(&ipaddr2, 192, 168, 7, 11); IP4_ADDR(&netmask2, 255, 255, 255, 0); IP4_ADDR(&gw2, 192, 168, 7, 1); print_app_header(); lwip_init(); /* Add network interface to the netif_list, and set it as default */ if (!xemac_add(echo_netif, &ipaddr, &netmask, &gw, mac_ethernet_address, XPAR_AXI_ETHERNET_0_BASEADDR)) { xil_printf("Error adding N/W interface\n\r"); return -1; } // if (!xemac_add(echo_netif2, &ipaddr2, &netmask2, // &gw2, mac_ethernet_address2, // XPAR_AXI_ETHERNET_1_BASEADDR)) { // xil_printf("Error adding N/W interface\n\r"); // return -1; // } netif_set_default(echo_netif); /* now enable interrupts */ platform_enable_interrupts(); /* specify that the network if is up */ netif_set_up(echo_netif); print_ip_settings(&ipaddr, &netmask, &gw); /* start the application (web server, rxtest, txtest, etc..) */ start_application(); /* receive and process packets */ while (1) { if (TcpFastTmrFlag) { tcp_fasttmr(); TcpFastTmrFlag = 0; } if (TcpSlowTmrFlag) { tcp_slowtmr(); TcpSlowTmrFlag = 0; } ReceivedCount += XUartLite_Recv(&UartLite,UARTRecvBuffer,UART_BUFFER_SIZE); if (ReceivedCount != 0) { ReceivedCount=0; ProcUartCommand(UARTRecvBuffer[0]); } xemacif_input(echo_netif); transfer_data(); } /* never reached */ cleanup_platform(); return 0; }

Вот мой участок кода, который я правлю

-

On 11/18/2022 at 8:16 PM, krux said:

ТЗ бестолково написано чтоли* Если есть 2 потока Надо 2 обработчика. Тваюмать, я 64 обработчика делел и что??1

Не понял

-

Всем привет. У меня возникла необходимость подключить 2 axi ethernet subsystem к одному microblaze.

С одним я работал, а вот с двумя не доводилось. Решил танцевать от примера echo, но пока меня интересует только ответ на ping.

Подключил оба интерфейса. Запустил пример - все пингуется. Как только добавляю строки

if (!xemac_add(echo_netif2, &ipaddr2, &netmask2, &gw2, mac_ethernet_address2, XPAR_AXI_ETHERNET_1_BASEADDR)) { xil_printf("Error adding N/W interface\n\r"); return -1; }

Что бы добавить новый netif в lwip, отваливается и первый интерфейс. Кто это реализовывал? может у меня есть какое-то принципиальное недопонимание? Любой подсказке буду рад

-

On 10/25/2021 at 8:43 AM, AVR said:

Удалось решить проблему? Это со всей очевидностью проблема путей. Есть ли файл liblwip где либо в каталогах?

Удалось. В консоли более подробные описания ошибок оказались, так как это проблемы сборки именно библиотеки(до этого смотрел просто эррор репорт) - нужно было еще в паре мест make файлы поправить.

-

Всем привет! Появилась необходимость поднять snmp агент на microblaze. Я полазил в lwip, который в xsdk подключается - там есть функции snmp, но такой опции в gui bsp settings нет.

Среда Vivado17.1/xsdk17.1

Что бы включить этот функционал надо задефайнить LWIP_SNMP в lwipopts.h. Но это автогенерируемый файл - пришлось править скрипт tcl создания этого хедера(https://support.xilinx.com/s/article/35787?language=en_US - вот по этому примеру добавил этот дефайн) прямо в папке библиотеки там где установлен xsdk

После того как дефайн прошел - повалились ошибки:

cannot find -llwip4 main_processing C/C++ Problem

expected expression before ';' token standalone_bsp_0 line 536 C/C++ ProblemКто этот функционал включал? Может этот функционал был частично обрезан? Или я просто делаю что-то не так?

P/S запуллил из гита соответствующую версию lwip/ Ничего там не выпилино вроде как, кроме ppp

-

Ну там действительно должен иметься высокодобротный фильтр пилота, его удобно делать через IIR, но задержки нужно будет конечно учитывать. В общем, можно сделать вывод что функционал не доступен пока, как я понимаю...

-

Привет! Возник вопрос по реализации стерео модулятора/демодулятора. На базе примера из help https://www.mathworks.com/help/comm/ref/comm.fmbroadcastmodulator-system-object.html реализовал коротенький скрипт:

clear all; [y,Fs] = audioread('stereo_file.mp3'); % soundsc(y, Fs) AirFs = 441000; fmbMod = comm.FMBroadcastModulator('AudioSampleRate',Fs, ... 'SampleRate',AirFs, 'Stereo', true); fmbDemod = comm.FMBroadcastDemodulator( ... 'AudioSampleRate',Fs, ... 'SampleRate',AirFs,'PlaySound',true, 'Stereo', true); audioData = y(1:AirFs*2, 1:2); modData = fmbMod(audioData); demodData = fmbDemod(modData);

В результате выполнения проигрывается моно сигнал(взял запись теста стереоэффекта с поочередным появлением звука то в одном канале, то в другом). Если убрать комментарий и проиграть soundsc(y, Fs), то стереоэффект есть.

Еще информация - в исходном стереосигнале есть большая разница между сигналами R и L, после демодуляции разница между каналами на 4 порядка ниже.

Если использовать пример из хелпа, то он не репрезентативный(пример с RBDS) так как там хоть и стоит флаг stereo, но в исходном сигнале нет стереоэффекта(rbds_capture_47500.wav)

Так же пробовал повторить в симулинке - там такая же проблема.

Более того если построить спектр от моделированного сигнала, я ожидал увидеть нечто похожее на картинку из help - то есть L+R, L-R и пилот на 19кГц, я же такой картины не вижу, то есть явно есть какая-то проблема с модуляцией.

Помогите пожалуйста разобраться.

Вот тут этот же вопрос задал, но может на этом форуме мне быстрее помогут. Извините за копипаст

https://hub.exponenta.ru/quest/fmbroadcastmodulator-vopros-po-stereo-demodulyatsii680

-

Вдруг будет полезно - в Vivado в Language templates есть макросы для CDC xpm_cdc_single, xpm_cdc_array_single, xpm_cdc_handshake - для них отдельно задавать тайминг констрэйнты не нужно, если их функционал устраивает.

-

До этого проводил тесты с флешкой 16 гигов fat 32, сейчас 4Гига fat16 - тест прошел, спасибо!

-

10 hours ago, Jury093 said:

а не смущает, что в вашем сишнике в двух местах написано, как должно выглядеть имя файла, типа

* To test logical drive 0, FileName should be "0:/<File name>" or

а у вас

static char FileName[32] = "Test.bin";

и еще - "which is previously formatted with FATFS" - попробуйте в FAT16 раздел отформатировать..

там написано

* To test with different logical drives, drive number should be mentioned in

* both FileName and Path variables. By default, it will take drive 0 if drive

* number is not mentioned in the FileName variable.

Раз я тестирую SD0, то по идее не нужно задавать имя "0:/Test.bin"А Path указан корректно

TCHAR *Path = "0:/";

Я отформатировал с компа sd под fat32. Надо попробовать fat16, но мне как-то это не пришло в голову, раз не написано какой fat

-

Привет всем!

Возникла проблема с sd картой. Решил в качестве тестов использовать пример от xilinx (прикрепил файл).

Плата zc702. Беру в sdk пребилд hw_platform для zc702, в bsp ставлю галку на использование библиотеки xilffs, в качестве исходников софта использую этот файл.

По идее, я полагал, что при настолько дефолтных условиях пример должен работать из коробки.

В итоге фэйлится на f_write - возвращает FR_DISK_ERR. После ряда тестирований начало фэйлиться на f_mkfs - возвращает FR_NOT_READY.Я грешу на то, что SD карта не поддерживается, но линукс с нее стартовал когда-то на этой же плате.

Подскажите пожалуйста, что может быть причиной такого поведения?

P/S Ключ защиты записи на самой карте не стоит, переключатели бута ставил и в положение загрузки с флешки и в положение загрузки по джтаг - это не изменило картины.

-

5 minutes ago, new123 said:

Когда сетка не поддается ни в какую, обычно начинают отлаживать ее петлей, исключая звенья цепи. Можно поставить петлевой sfp, но это стоит денег. Альтера еще разрешает конфигурировать трансиверы, чтобы была перемычка на диф паре и получается отладить сетку самим с собой, наверняка и у вас так можно.

У меня есть возможность оптику из tx в rx в sfp ткнуть.

Попробую спасибо,

-

Всем привет!

Возникла проблема с переводом проекта с меди 1000BASE-T на одномодовую оптику 1000BASE-LX

Отладочный проект состоит из микроблэйза, ядра axi ethernet subsystem и ядра ethernet pcs/pma - стандартные ксаевские. Дифпара от трансиверов идет на sfp. Внешнего фая нет, есть только iic для общения с sfp.

Я полагал, что поддерживаться должна как медь так и оптика, стандарт в pcs/pma выбран sgmii, линк всегда 1Гигабит для обоих режимов.

В итоге для оптики линк поднимается, но данных на gmii с pcs/pma никаких не наблюдается кроме интерфрэйм гэпа(BC50). Подскжите пожалуйста в какую сторону копать? Возможно нужна специфическая инициализация через iic? или для одномодовой оптики есть свое кодирование, fec какой-нибудь?

-

Возникла старая проблема, которую пока накак не получается решить.

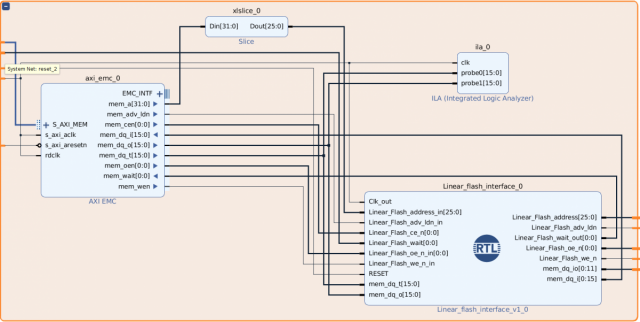

Вставил emc в дизайн согласно примеру.(картинка)

Код rtl блока просто выдран из примера(у них он вставлен во враппер, я вынес отдельно)

library IEEE; use IEEE.STD_LOGIC_1164.ALL; library UNISIM; use UNISIM.VCOMPONENTS.ALL; use unisim.vcomponents.STARTUPE3; entity Linear_flash_interface is port ( Clk_out: in STD_LOGIC; Linear_Flash_address_in : in STD_LOGIC_VECTOR ( 25 downto 0 ); Linear_Flash_address : out STD_LOGIC_VECTOR ( 25 downto 0 ); Linear_Flash_adv_ldn_in : in STD_LOGIC; Linear_Flash_adv_ldn : out STD_LOGIC; Linear_Flash_ce_n : in std_logic_vector (0 downto 0); Linear_Flash_wait : in STD_LOGIC_VECTOR ( 0 to 0 ); Linear_Flash_wait_out : out STD_LOGIC_VECTOR ( 0 to 0 ); Linear_Flash_oe_n_in : in STD_LOGIC_VECTOR ( 0 to 0 ); Linear_Flash_oe_n : out STD_LOGIC_VECTOR ( 0 to 0 ); Linear_Flash_we_n_in : in STD_LOGIC; Linear_Flash_we_n : out STD_LOGIC; RESET : in STD_LOGIC; mem_dq_io : inout STD_LOGIC_VECTOR ( 0 to 11 ); mem_dq_t : in STD_LOGIC_VECTOR ( 15 downto 0 ); mem_dq_i : out STD_LOGIC_VECTOR ( 0 to 15 ); mem_dq_o : in STD_LOGIC_VECTOR ( 15 downto 0 ) ); end Linear_flash_interface; architecture STRUCTURE of Linear_flash_interface is signal dq_o : std_logic_vector (3 downto 0); signal dq_o_e, dq_i_e_int : std_logic_vector (15 downto 0); signal dq_t : std_logic_vector (3 downto 0); signal dq_t_e : std_logic_vector (15 downto 0); signal dq_i : std_logic_vector (3 downto 0); signal dq_i_e : std_logic_vector (0 to 11); --------------------------------------------- constant ADD_PIPELINTE : integer := 8; signal pipe_signal : std_logic_vector(ADD_PIPELINTE-1 downto 0); signal PREQ_int : std_logic; signal PACK_int : std_logic; signal cnt : integer := 0; signal div_temp : std_logic := '0'; signal startupe3_eos : std_logic; signal GPIO_LED_0_LS: STD_LOGIC; signal GPIO_LED_1_LS: STD_LOGIC; signal GPIO_LED_2_LS: STD_LOGIC; signal GPIO_LED_3_LS: STD_LOGIC; signal GPIO_LED_4_LS: STD_LOGIC; signal GPIO_LED_5_LS: STD_LOGIC; signal GPIO_LED_6_LS: STD_LOGIC; signal GPIO_LED_7_LS: STD_LOGIC; --------------------------------------------- begin PREQ_REG_P:process(Clk_out)is begin if(Clk_out'event and Clk_out = '1') then if(reset = '1')then pipe_signal(0) <= '0'; elsif(PREQ_int = '1')then pipe_signal(0) <= '1'; end if; end if; end process PREQ_REG_P; PIPE_PACK_P:process(Clk_out)is begin if(Clk_out'event and Clk_out = '1') then if(reset = '1')then pipe_signal(ADD_PIPELINTE-1 downto 1) <= (others => '0'); else pipe_signal(1) <= pipe_signal(0); pipe_signal(2) <= pipe_signal(1); pipe_signal(3) <= pipe_signal(2); pipe_signal(4) <= pipe_signal(3); pipe_signal(5) <= pipe_signal(4); pipe_signal(6) <= pipe_signal(5); pipe_signal(7) <= pipe_signal(6); if (cnt >= 50000000) then div_temp <= not(div_temp); cnt <= 0; else cnt <= (cnt + 1); end if; GPIO_LED_0_LS <= not(div_temp); GPIO_LED_1_LS <= '0'; GPIO_LED_2_LS <= '0'; GPIO_LED_3_LS <= '0'; GPIO_LED_4_LS <= '0'; --startupe3_eos; GPIO_LED_5_LS <= '0'; GPIO_LED_6_LS <= '0'; GPIO_LED_7_LS <= not (startupe3_eos); end if; end if; end process PIPE_PACK_P; PACK_int <= pipe_signal(7); Linear_Flash_address(25 downto 0) <= Linear_Flash_address_in(25 downto 0); Linear_Flash_adv_ldn <= Linear_Flash_adv_ldn_in; Linear_Flash_oe_n(0) <= Linear_Flash_oe_n_in(0); Linear_Flash_we_n <= Linear_Flash_we_n_in; Linear_Flash_wait_out(0) <= Linear_Flash_wait(0); dq_t_e(15 downto 0) <= mem_dq_t(15 downto 0); mem_dq_i <= dq_i_e( 0 to 11) & dq_i; dq_o_e(15 downto 0) <= mem_dq_o; STARTUPE3_inst : component STARTUPE3 ----------------------- generic map ( PROG_USR => "FALSE", -- Activate program event security feature. SIM_CCLK_FREQ => 0.0 -- Set the Configuration Clock Frequency(ns) for simulation. ) port map ( CFGCLK => open, -- 1-bit output: Configuration main clock output CFGMCLK => open, -- 1-bit output: Configuration internal oscillator clock output DI => dq_i, -- 4-bit output: Allow receiving on the D input pin EOS => startupe3_eos, -- 1-bit output: Active-High output signal indicating the End Of Startup PREQ => open, -- 1-bit output: PROGRAM request to fabric output DO => dq_o_e(3 downto 0), -- 4-bit input: Allows control of the D pin output DTS => dq_t_e(3 downto 0), -- 4-bit input: Allows tristate of the D pin FCSBO => Linear_Flash_ce_n(0), -- 1-bit input: Contols the FCS_B pin for flash access FCSBTS => '0', -- 1-bit input: Tristate the FCS_B pin GSR => '0', -- 1-bit input: Global Set/Reset input (GSR cannot be used for the port) GTS => '0', -- 1-bit input: Global 3-state input (GTS cannot be used for the port name) KEYCLEARB => '1', -- 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM) PACK => PACK_int, -- 1-bit input: PROGRAM acknowledge input USRCCLKO => Clk_out, -- 1-bit input: User CCLK input USRCCLKTS => '0', -- 1-bit input: User CCLK 3-state enable input USRDONEO => '1', -- 1-bit input: User DONE pin output control USRDONETS => '1' -- 1-bit input: User DONE 3-state enable output ); mem_dq_iobuf_4 : IOBUF port map ( I => dq_o_e(4), IO => mem_dq_io(0), O => dq_i_e(11), T => dq_t_e(4) ); mem_dq_iobuf_5 : IOBUF port map ( I => dq_o_e(5), IO => mem_dq_io(1), O => dq_i_e(10), T => dq_t_e(5) ); mem_dq_iobuf_6 : IOBUF port map ( I => dq_o_e(6), IO => mem_dq_io(2), O => dq_i_e(9), T => dq_t_e(6) ); mem_dq_iobuf_7 : IOBUF port map ( I => dq_o_e(7), IO => mem_dq_io(3), O => dq_i_e(8), T => dq_t_e(7) ); mem_dq_iobuf_8 : IOBUF port map ( I => dq_o_e(8), IO => mem_dq_io(4), O => dq_i_e(7), T => dq_t_e(8) ); mem_dq_iobuf_9 : IOBUF port map ( I => dq_o_e(9), IO => mem_dq_io(5), O => dq_i_e(6), T => dq_t_e(9) ); mem_dq_iobuf_10 : IOBUF port map ( I => dq_o_e(10), IO => mem_dq_io(6), O => dq_i_e(5), T => dq_t_e(10) ); mem_dq_iobuf_11 : IOBUF port map ( I => dq_o_e(11), IO => mem_dq_io(7), O => dq_i_e(4), T => dq_t_e(11) ); mem_dq_iobuf_12 : IOBUF port map ( I => dq_o_e(12), IO => mem_dq_io(8), O => dq_i_e(3), T => dq_t_e(12) ); mem_dq_iobuf_13 : IOBUF port map ( I => dq_o_e(13), IO => mem_dq_io(9), O => dq_i_e(2), T => dq_t_e(13) ); mem_dq_iobuf_14 : IOBUF port map ( I => dq_o_e(14), IO => mem_dq_io(10), O => dq_i_e(1), T => dq_t_e(14) ); mem_dq_iobuf_15 : IOBUF port map ( I => dq_o_e(15), IO => mem_dq_io(11), O => dq_i_e(0), T => dq_t_e(15) ); end STRUCTURE;

Дальше ноги идут непосредственно на выход.

В такой конфигурации все работает хорошо, но как только я убираю ila читаться из флешки перестает...

В превую очередь я грешил на констрэйнты, но они заданы согласно даташиту

#### Max Tco -- Clock to input delay for flash set tco_max 5.5 set tco_min 5.5 #### Trace delays for VCU108 board set tdata_trace_delay_max 0.25 set tdata_trace_delay_min 0.25 set tclk_trace_delay_max 0.2 set tclk_trace_delay_min 0.2 set startup_delay_max 7.000 set startup_delay_min 1.350 set board_del_max 1.000 set board_del_min 0.500 set_input_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tco_max + $tdata_trace_delay_max+ $tclk_trace_delay_max + $startup_delay_max + $board_del_max] [get_ports {mem_dq_io[*]}] set_input_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tco_min + $tdata_trace_delay_min+ $tclk_trace_delay_min + $startup_delay_min + $board_del_min] [get_ports {mem_dq_io[*]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tdata_trace_delay_max -$tclk_trace_delay_min + $startup_delay_max + $board_del_max] [get_ports {mem_dq_io[*]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tdata_trace_delay_min -$tclk_trace_delay_max + $startup_delay_min + $board_del_min] [get_ports {mem_dq_io[*]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tdata_trace_delay_max -$tclk_trace_delay_min + $board_del_max] [get_ports {Linear_Flash_address[*]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tdata_trace_delay_min -$tclk_trace_delay_max + $board_del_min] [get_ports {Linear_Flash_address[*]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tdata_trace_delay_max -$tclk_trace_delay_min + $board_del_max] [get_ports {Linear_Flash_oe_n[0]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tdata_trace_delay_min -$tclk_trace_delay_max + $board_del_min] [get_ports {Linear_Flash_oe_n[0]}] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tdata_trace_delay_max -$tclk_trace_delay_min + $board_del_max] [get_ports Linear_Flash_we_n] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tdata_trace_delay_min -$tclk_trace_delay_max + $board_del_min] [get_ports Linear_Flash_we_n] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tdata_trace_delay_max -$tclk_trace_delay_min + $board_del_max] [get_ports Linear_Flash_adv_ldn] set_output_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tdata_trace_delay_min -$tclk_trace_delay_max + $board_del_min] [get_ports Linear_Flash_adv_ldn] #### Input delay constraints (max/min) for Linear_flash_wait[0] set_input_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -max [expr $tco_max + $tdata_trace_delay_max + $tclk_trace_delay_max + $board_del_max] [get_ports {Linear_Flash_wait[0]}] set_input_delay -clock [get_clocks clk_50MHz_vzr_top_clk_wiz_0_0] -min [expr $tco_min + $tdata_trace_delay_min + $tclk_trace_delay_min + $board_del_min] [get_ports {Linear_Flash_wait[0]}] set_input_delay -max [expr $tdata_trace_delay_max + $tclk_trace_delay_max + $board_del_max] [get_ports RESET] set_input_delay -min [expr $tdata_trace_delay_min - $tclk_trace_delay_max + $board_del_min] [get_ports RESET]

Так же я с такими проблемами сталкивался когда есть кривые комбинационные схемы или есть тайминг игнор на некоторые цепи и он некорректен. Но в данном случае этого нет.

Попробовал зафиксировать положение блока в констрейнтах - это так же результата не дало. Так же попробовал перейти на более новую вивадо - тоже без результата. Частоты выставил как в примере - так что тут тоже проблем вроде не должно быть.

Подскажите пожалуйста, где может быть проблема?

-

6 minutes ago, one_eight_seven said:

А зачем куда-то копать? Размер AXI Slave 4k. Границу слейва транзакция пересекать не должна.

Я посмотрел в стандартах на ограничение размера берста и не посмотрел на максимальный объем данных в берсте спасибо, глупо получилось

-

Здравствуйте! Появилась необходимость верифицировать самописный AXI мастер, хочу научться работать с AXI Verification IP. Попробовал покопаться в примерах. В итоге написал такой модуль:

`timescale 1ns / 1ps import axi_vip_v1_0_1_pkg::*; import axi_vip_0_pkg::*; module tb_vip_top( ); tb_with_vip DUT ( ); axi_vip_0_slv_t slv_agent; initial begin //Create an agent slv_agent = new("slave vip agent",DUT_wrapped_bd.axi_vip_0_inst.inst.IF); // set tag for agents for easy debug slv_agent.set_agent_tag("Slave VIP"); // set print out verbosity level. slv_agent.set_verbosity(0); //Start the agent slv_agent.start_slave(); end endmodule

у него дочерний модуль это

`timescale 1ns / 1ps module tb_with_vip( ); parameter PERIOD = 4; reg clk; always begin clk = 1'b0; #(PERIOD/2) clk = 1'b1; #(PERIOD/2); end wire [31 : 0] s_axi_awaddr; wire [7 : 0] s_axi_awlen; wire [2 : 0] s_axi_awsize; wire [1 : 0] s_axi_awburst; wire [0 : 0] s_axi_awlock; wire [3 : 0] s_axi_awcache; wire [2 : 0] s_axi_awprot; wire [3 : 0] s_axi_awqos; wire s_axi_awvalid; wire s_axi_awready; wire [511 : 0] s_axi_wdata; wire [63 : 0] s_axi_wstrb; wire s_axi_wlast; wire s_axi_wvalid; wire s_axi_wready; wire [1 : 0] s_axi_bresp; wire s_axi_bvalid; wire s_axi_bready; wire [31 : 0] s_axi_araddr; wire [7 : 0] s_axi_arlen; wire [2 : 0] s_axi_arsize; wire [1 : 0] s_axi_arburst; wire [0 : 0] s_axi_arlock; wire [3 : 0] s_axi_arcache; wire [2 : 0] s_axi_arprot; wire [3 : 0] s_axi_arqos; wire s_axi_arvalid; wire s_axi_arready; wire [511 : 0] s_axi_rdata; wire [1 : 0] s_axi_rresp; wire s_axi_rlast; wire s_axi_rvalid; wire s_axi_rready; reg m00_axi_init_axi_txn; wire [639 : 0] tdata; wire tready; wire tlast; wire tvalid; input_data_emulator input_data_emulator_inst ( .clk(clk), .rst(m00_axi_init_axi_txn), .data_size(32'h50), .zeros(0), .dv_in(tready), .data_out(tdata), .dv_out(tvalid), .tlast_out(tlast) ); initial begin m00_axi_init_axi_txn <= 1; #50; m00_axi_init_axi_txn <= 0; #50; m00_axi_init_axi_txn <= 1; end // Add user logic here axi_ddr_data_master # ( .INTERFACE_NUMBER(0) ) axi_ddr_data_master_inst ( //INPUT AXIS INTERFACE .s_axis_DSP_tdata(tdata), .s_axis_DSP_tvalid(tvalid), .s_axis_DSP_tready(tready), .s_axis_DSP_tlast(tlast), //INPUT AXIS INTERFACE .m_axis_out_tdata(), .m_axis_out_tvalid(), .m_axis_out_tready(1), .m_axis_out_tlast(), // User ports ends // Do not modify the ports beyond this line // Ports of Axi Master Bus Interface M00_AXI .m00_axi_aclk(clk), .m00_axi_aresetn(m00_axi_init_axi_txn), .m00_axi_awaddr(s_axi_awaddr), .m00_axi_awlen(s_axi_awlen), .m00_axi_awsize(s_axi_awsize), .m00_axi_awburst(s_axi_awburst), .m00_axi_awlock(s_axi_awlock), .m00_axi_awcache(s_axi_awcache), .m00_axi_awprot(s_axi_awprot), .m00_axi_awqos(s_axi_awqos), .m00_axi_awvalid(s_axi_awvalid), .m00_axi_awready(s_axi_awready), .m00_axi_wdata(s_axi_wdata), .m00_axi_wstrb(s_axi_wstrb), .m00_axi_wlast(s_axi_wlast), .m00_axi_wvalid(s_axi_wvalid), .m00_axi_wready(s_axi_wready), .m00_axi_bresp(s_axi_bresp), .m00_axi_bvalid(s_axi_bvalid), .m00_axi_bready(s_axi_bready), .m00_axi_araddr(s_axi_araddr), .m00_axi_arlen(s_axi_arlen), .m00_axi_arsize(s_axi_arsize), .m00_axi_arburst(s_axi_arburst), .m00_axi_arlock(s_axi_arlock), .m00_axi_arcache(s_axi_arcache), .m00_axi_arprot(s_axi_arprot), .m00_axi_arqos(s_axi_arqos), .m00_axi_arvalid(s_axi_arvalid), .m00_axi_arready(s_axi_arready), .m00_axi_rdata(s_axi_rdata), .m00_axi_rresp(s_axi_rresp), .m00_axi_rlast(s_axi_rlast), .m00_axi_rvalid(s_axi_rvalid), .m00_axi_rready(s_axi_rready) ); axi_vip_0 axi_vip_0_inst ( .aclk(clk), // input wire aclk .aresetn(1'b1), // input wire aresetn .s_axi_awaddr(s_axi_awaddr), // input wire [31 : 0] s_axi_awaddr .s_axi_awlen(s_axi_awlen), // input wire [7 : 0] s_axi_awlen .s_axi_awsize(s_axi_awsize), // input v .s_axi_awburst(s_axi_awburst), // input wire [1 : 0] s_axi_awburst .s_axi_awlock(s_axi_awlock), // input wire [0 : 0] s_axi_awlock .s_axi_awcache(s_axi_awcache), // input wire [3 : 0] s_axi_awcache .s_axi_awprot(s_axi_awprot), // input wire [2 : 0] s_axi_awprot .s_axi_awqos(s_axi_awqos), // input wire [3 : 0] s_axi_awqos .s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid .s_axi_awready(s_axi_awready), // output wire s_axi_awready .s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata .s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb .s_axi_wlast(s_axi_wlast), // input wire s_axi_wlast .s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid .s_axi_wready(s_axi_wready), // output wire s_axi_wready .s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp .s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid .s_axi_bready(s_axi_bready), // input wire s_axi_bready .s_axi_araddr(s_axi_araddr), // input wire [31 : 0] s_axi_araddr .s_axi_arlen(s_axi_arlen), // input wire [7 : 0] s_axi_arlen .s_axi_arsize(s_axi_arsize), // input wire [2 : 0] s_axi_arsize .s_axi_arburst(s_axi_arburst), // input wire [1 : 0] s_axi_arburst .s_axi_arlock(s_axi_arlock), // input wire [0 : 0] s_axi_arlock .s_axi_arcache(s_axi_arcache), // input wire [3 : 0] s_axi_arcache .s_axi_arprot(s_axi_arprot), // input wire [2 : 0] s_axi_arprot .s_axi_arqos(s_axi_arqos), // input wire [3 : 0] s_axi_arqos .s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid .s_axi_arready(s_axi_arready), // output wire s_axi_arready .s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata .s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp .s_axi_rlast(s_axi_rlast), // output wire s_axi_rlast .s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid .s_axi_rready(s_axi_rready) // input wire s_axi_rready ); endmodule

По сути это подобие DMA

Симуляция запускается, проходит до начала первой транзакции в слэйв и останавливается со следующим сообщением:

XilinxAXIVIP: Found at Path: tb_vip_top.DUT_wrapped_bd.axi_vip_0_inst.inst Fatal: [AXI_WMON0_0] (axi_vip_v1_0_1_pkg.axi_transaction::create_data_array) 462000 : Attempted to generate a DATA array greater than 4K in size ( 4416) Time: 462 ns Iteration: 0 Process: /axi_vip_v1_0_1_pkg/axi_monitor(C_AXI_WDATA_WIDTH=512,C_AXI_RDATA_WIDTH=512,C_AXI_HAS_REGION=0)::aw_channel/AW_LOOP File: /wrk/2017.1/nightly/2017_04_14_1846317/packages/customer/vivado/data/ip/xilinx/axi_vip_v1_0/hdl/axi_vip_v1_0_vl_rfs.sv $finish called at time : 462 ns : File "/wrk/2017.1/nightly/2017_04_14_1846317/packages/customer/vivado/data/ip/xilinx/xil_common_vip_v1_0/hdl/xil_common_vip_v1_0_vl_rfs.sv" Line 100 WARNING: [Simulator 45-29] Cannot open source file /wrk/2017.1/nightly/2017_04_14_1846317/packages/customer/vivado/data/ip/xilinx/xil_common_vip_v1_0/hdl/xil_common_vip_v1_0_vl_rfs.sv: file does not exist. INFO: [USF-XSim-96] XSim completed. Design snapshot 'tb_vip_top_behav' loaded. INFO: [USF-XSim-97] XSim simulation ran for 1000ns launch_simulation: Time (s): cpu = 00:00:11 ; elapsed = 00:00:07 . Memory (MB): peak = 6378.914 ; gain = 10.691 ; free physical = 23880 ; free virtual = 61100

Я так понял размер транзакции слишком большой для дефолтного буфера, но покопавшись в автогенерируемых файлах исходников мне показалось, что resize должен быть автоматический.

Параметры у меня такие:

parameter integer C_M00_AXI_BURST_LEN = 128; parameter integer C_M00_AXI_ID_WIDTH = 1; parameter integer C_M00_AXI_ADDR_WIDTH = 32; parameter integer C_M00_AXI_DATA_WIDTH = 512; parameter integer C_M00_AXI_AWUSER_WIDTH = 0; parameter integer C_M00_AXI_ARUSER_WIDTH = 0; parameter integer C_M00_AXI_WUSER_WIDTH = 0; parameter integer C_M00_AXI_RUSER_WIDTH = 0; parameter integer C_M00_AXI_BUSER_WIDTH = 0;

Подскажите пожалуйста куда копать?

-

24 minutes ago, des00 said:

SV for verification, Writing testbenches, Universal Methodology Manual изучите, потом, если останутся темные места, можно будет обсудить :)

Спасибо!

-

19 minutes ago, des00 said:

Почитайте лучше Writing Testbenches using SV, полезнее будет.

Спасибо, он тоже на очереди.

ЗЫ Что-то я не понял - если генератор норм, хотя там то же самое блокирующее присвоение, почему в остальных местах не норм... Но видимо стоит сначала изучить описанные вами материалы, перед тем как задавать такие вопросы:)

+ как тогда использовать fork join any или join all если блокирующих операций нет в теле...

-

4 hours ago, des00 said:

@Lutovid а использовать блокирующие присваивания и не использовать clocking block этот же самый учебник рекомендует?

В учебнике расписана разница блокирующего и не блокирующего и почему они так называются. Представленный файл - не синтезируемый и в нем я решил использовать этот тип присвоений исходя из логики работы симулятора. Вполне мог ошибиться, но если вы про тезис - что во всех модулях always должны использоваться неблокирующие присвоения, то в синтезируемых модулях у меня так и есть. про clocking block мне ничего не известно и в учебнике такого не припомню=/

Аааа, если вы про initial, который генерит клок, то это из ксаевского language template

23 hours ago, Nick_K said:Я лично ООП в тестбенчах не использую и скорее всего не буду - мне хватает головной боли в синтезируемом проекте, чтобы ещё разбираться где какой класс не работает или другие "прелести" вылазят. Упрощайте себе жизнь ;)

Я не использовал, но хочу попробовать, все это эксперимент, который я провожу в свободное от работы время

-

32 minutes ago, Nick_K said:

Случайно не "Логическое проектирование и верификация систем на SysytemVerilog"? В таком случае советую забыть об этой книге. Хотя бы на год-два. И почитать что-то более полезное и вразумительное. Обрести понимание конструкций и функционала языка. Книга написана плохо и с кучей ошибок (русский вариант, английский всё ещё не нашёл, чтобы проверить). Да там есть полезные вещи, но только в случае если Вы понимаете конструкции и видите где есть ошибки, чтобы их не повторять у себя.

Да, эта книга. Я читал ее с целью - структурировать свои знания и узнать новые возможности, про которые я не знал. Очевидные ошибки ака опечатки я в этой книге встречал, как и в любой другой. Подскажите пожалуйста какие принципиальные ошибки вы там увидели? Или вы увидели их у меня в коде?

P/S об ошибках кстати можно написать в издательство - они как раз об этом упоминают в книге, если бы я увидел - я бы наверное написал бы им:)

-

5 hours ago, nice_vladi said:

Возможно, гуру верификации будут бить меня ногами, но тащить task в interface - как-то не логично. Интерфейсы должны просто соединять модули, классы и т.д. А вот внутри этих модулей и классов должны изменяться сигналы.

Я осваиваю этот функционал по учебнику Дональда Томаса - здесь представлено довольно удобно - если есть задача протестировать именно интерфейс, то можно поступить так как описано. То есть внутри интерфейса есть таск по его проверке/

-

Привет всем!

Осваиваю новые конструкции языка и столкнулся с проблемой

Написал Вот такой блок симуляции

Spoiler`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 11/16/2019 01:40:03 PM // Design Name: // Module Name: TestBench // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// import gmii_router_definitions::*; //clock generation class class clkParameters; int period = 8; rand int clk_pahse_delay [3:0]; constraint phase_values { foreach (clk_pahse_delay[i]) { clk_pahse_delay[i]<period && clk_pahse_delay[i]>=0;}} endclass : clkParameters //frame generation class and package package frameTypePKG; typedef enum {BROADCAST_P=0, UNICAST_P=1} frameType; endpackage import frameTypePKG::*; class frameParameters; typedef enum {BROADCAST_P=0, UNICAST_P=1} frameType; rand logic shrinked_preamble; rand int frame_length; rand frameType frame_type; constraint frame_length_constr {frame_length inside {[64:1500]};} constraint frameTypeConstr { frame_type dist { BROADCAST_P := 2, UNICAST_P := 8 }; } endclass : frameParameters //gmii interface interface gmii_interface_io (); logic [7:0] rxd; logic rx_dv; logic rx_err; logic [7:0] txd; logic tx_en; logic tx_err; modport master (input rxd, input rx_dv, input rx_err, output txd, output tx_en, output tx_err); modport slave (output rxd, output rx_dv, output rx_err, input txd, input tx_en, input tx_err); endinterface: gmii_interface_io // //switch inner interfaces(generate acks on rxd lanes) // interface gmii_interface_io_inner (input clk2, input clk3, gmii_interface_io.slave port2, gmii_interface_io.slave port3); // logic [47:0] port2_device_MAC = 48'h22AABBCCDDAA; // logic [47:0] port3_device_MAC = 48'h33AABBCCDDAA; // // modport sendData(import send_frame); // // task send_frame(int data_size); // // endtask : send_frame // endinterface: gmii_interface_io_inner //switch inner interfaces(generate data on txd lanes) interface gmii_interface_io_outer (input clk, gmii_interface_io.master port); modport sendData(import send_rx_frame); task send_rx_frame(input logic [47:0] MAC_SRC_VAL, input logic [47:0] MAC_DST_VAL); frameParameters fT = new(); fT.randomize(); $display("Shrinked = %d, Size = %d", fT.shrinked_preamble, fT.frame_length); port.rx_dv = 0; port.rx_err = 0; port.rxd = 8'h00; for(int i=0;i<12;i++)begin : send_interframe @(posedge clk); port.rx_dv = 0; port.rx_err = 0; port.rxd = 8'h55; end for(int i=0;i<(6+fT.shrinked_preamble);i++)begin : send_preamble @(posedge clk); port.rx_dv = 1; port.rx_err = 0; port.rxd = 8'h55; end @(posedge clk);//end of preamble port.rx_dv = 1; port.rx_err = 0; port.rxd = 8'hD5; for(int i=0;i<6;i++)begin : send_MAC_dst @(posedge clk); port.rx_dv = 1; port.rx_err = 0; if (fT.frame_type==BROADCAST_P) begin port.rxd = 8'hFF; end else begin port.rxd = MAC_DST_VAL[i*8+:8]; end end for(int i=0;i<6;i++)begin : send_MAC_src @(posedge clk); port.rx_dv = 1; port.rx_err = 0; port.rxd = MAC_SRC_VAL[i*8+:8]; end for(int i=0;i<fT.frame_length;i++)begin : send_payload @(posedge clk); port.rx_dv = 1; port.rx_err = 0; port.rxd = $urandom(); end @(posedge clk);//end of packet port.rx_dv = 0; port.rx_err = 0; port.rxd = 8'h55; endtask : send_rx_frame endinterface: gmii_interface_io_outer module TestBench( ); //clock generation logic sys_clk, clk[3:0]; clkParameters clk_param = new(); event sys_clk_start, clk_start; logic [3:0] clk_start_trg; initial begin assert (clk_param.randomize()) else $error("rand didn't work"); $display("Phase delays:%p",clk_param.clk_pahse_delay); #10->clk_start; end initial begin sys_clk = 1'b0; @clk_start;//wait phase initialize forever begin sys_clk = #(clk_param.period/2) ~sys_clk; end end initial begin clk_start_trg=0; @clk_start;//wait phase initialize fork for (int i = 0; i < 4; i++) begin clk_start_trg[i] = #(clk_param.clk_pahse_delay[i]) 1'b1; end join end genvar clk_inst; generate for (clk_inst=0; clk_inst < 4; clk_inst++) begin: clock_distrib always begin if (clk_start_trg[clk_inst]) begin clk[clk_inst] = 1'b0; #(clk_param.period/2) clk[clk_inst] = 1'b1; #(clk_param.period/2); end else #1 clk[clk_inst] = 1'b0;; end end endgenerate //dut instantiating gmii_interface_io gmii_interface_io_port0(); gmii_interface_io gmii_interface_io_port1(); gmii_interface_io gmii_interface_io_port2(); gmii_interface_io gmii_interface_io_port3(); gmii_interface_io_outer gmii_flow_0(clk[0], gmii_interface_io_port0); gmii_interface_io_outer gmii_flow_1(clk[1], gmii_interface_io_port1); initial begin : sender_0 @clk_start;//wait phase initialize gmii_flow_0.sendData.send_rx_frame(20,40); end // initial begin : sender_1 // @clk_start;//wait phase initialize // gmii_flow_1.sendData.send_rx_frame(20,40); // end gmii_switch_2x2 dut ( .arp_table_clk(sys_clk), .clk_port0(clk[0]), .clk_port1(clk[1]), .clk_port2(clk[2]), .clk_port3(clk[3]), .rst(1'b0), .gmii_rxd_0 (), .gmii_rx_dv_0 (), .gmii_rx_err_0(), .gmii_txd_0 (), .gmii_tx_dv_0 (), .gmii_tx_err_0(), .gmii_rxd_1 (), .gmii_rx_dv_1 (), .gmii_rx_err_1(), .gmii_txd_1 (), .gmii_tx_dv_1 (), .gmii_tx_err_1(), .gmii_rxd_2 (), .gmii_rx_dv_2 (), .gmii_rx_err_2(), .gmii_txd_2 (), .gmii_tx_dv_2 (), .gmii_tx_err_2(), .gmii_rxd_3 (), .gmii_rx_dv_3 (), .gmii_rx_err_3(), .gmii_txd_3 (), .gmii_tx_dv_3 (), .gmii_tx_err_3() ); endmodule : TestBench

Если в нем закомментить строку

gmii_interface_io_outer gmii_flow_1(clk[1], gmii_interface_io_port1);

То симуляция стартует без ошибок, при том, что строка

gmii_interface_io_outer gmii_flow_0(clk[0], gmii_interface_io_port0); останется

Но если присутствуют обе эти строки, то появляется ошибка:

INFO: [Vivado 12-4795] Using compiled simulation libraries for IPs INFO: [SIM-utils-51] Simulation object is 'sim_1' INFO: [USF-XSim-7] Finding pre-compiled libraries... INFO: [USF-XSim-11] File '/home/xakstreet/XilinxDistr/Vivado/2017.1/data/xsim/ip/xsim_ip.ini' copied to run dir:'/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/xproject/gmii_switch.sim/sim_1/behav' INFO: [SIM-utils-54] Inspecting design source files for 'TestBench' in fileset 'sim_1'... INFO: [USF-XSim-97] Finding global include files... INFO: [USF-XSim-98] Fetching design files from 'sim_1'... INFO: [USF-XSim-2] XSim::Compile design INFO: [USF-XSim-61] Executing 'COMPILE and ANALYZE' step in '/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/xproject/gmii_switch.sim/sim_1/behav' xvlog -m64 --relax -L xil_defaultlib -prj TestBench_vlog.prj INFO: [VRFC 10-2263] Analyzing Verilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/ip/data_combiner_fifo/sim/data_combiner_fifo.v" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module data_combiner_fifo INFO: [VRFC 10-2263] Analyzing Verilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/ip/mac_info_clock_converter/sim/mac_info_clock_converter.v" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module mac_info_clock_converter INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/gmii_router_definitions.sv" into library xil_defaultlib INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/MAC_table_writer.sv" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module MAC_table_writer INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/gmii_data_combiner.sv" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module gmii_data_combiner INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/gmii_router.sv" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module gmii_router INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/gmii_switch.sv" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module gmii_switch_2x2 INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/mac_source_parser.sv" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module mac_source_parser INFO: [VRFC 10-2263] Analyzing SystemVerilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/TestBench.sv" into library xil_defaultlib WARNING: [VRFC 10-2167] variable fT must explicitly be declared as automatic or static [/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/TestBench.sv:80] INFO: [VRFC 10-311] analyzing module TestBench INFO: [VRFC 10-2263] Analyzing Verilog file "/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/xproject/gmii_switch.sim/sim_1/behav/glbl.v" into library xil_defaultlib INFO: [VRFC 10-311] analyzing module glbl xvhdl -m64 --relax -prj TestBench_vhdl.prj INFO: [USF-XSim-69] 'compile' step finished in '0' seconds INFO: [USF-XSim-3] XSim::Elaborate design INFO: [USF-XSim-61] Executing 'ELABORATE' step in '/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/xproject/gmii_switch.sim/sim_1/behav' Vivado Simulator 2017.1 Copyright 1986-1999, 2001-2016 Xilinx, Inc. All Rights Reserved. Running: /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab -wto 9b9d5eb16de34b8c975b93350c2304c7 --debug typical --relax --mt 8 -L fifo_generator_v13_1_4 -L xil_defaultlib -L axis_infrastructure_v1_1_0 -L axis_data_fifo_v1_1_13 -L axis_clock_converter_v1_1_13 -L unisims_ver -L unimacro_ver -L secureip -L xpm --snapshot TestBench_behav xil_defaultlib.TestBench xil_defaultlib.glbl -log elaborate.log Using 8 slave threads. Starting static elaboration WARNING: [VRFC 10-278] actual bit length 10 differs from formal bit length 16 for port s_axis_tdata [/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/gmii_data_combiner.sv:82] WARNING: [VRFC 10-278] actual bit length 10 differs from formal bit length 16 for port m_axis_tdata [/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/src/rtl/gmii_data_combiner.sv:86] WARNING: [VRFC 10-1783] select index 2 into rrst_reg is out of bounds [/wrk/2017.1/nightly/2017_04_14_1846317/packages/customer/vivado/data/ip/xilinx/fifo_generator_v13_1/simulation/fifo_generator_vlog_beh.v:4885] WARNING: [VRFC 10-597] element index -1 into num_read_words_dc is out of bounds [/wrk/2017.1/nightly/2017_04_14_1846317/packages/customer/vivado/data/ip/xilinx/fifo_generator_v13_1/simulation/fifo_generator_vlog_beh.v:5490] WARNING: [VRFC 10-597] element index -1 into num_write_words_dc is out of bounds [/wrk/2017.1/nightly/2017_04_14_1846317/packages/customer/vivado/data/ip/xilinx/fifo_generator_v13_1/simulation/fifo_generator_vlog_beh.v:5540] Completed static elaboration Starting simulation data flow analysis Completed simulation data flow analysis ERROR: [XSIM 43-3316] Signal SIGSEGV received. Printing stacktrace... [0] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x6fd754] [1] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x75e249] [2] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x75e377] [3] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x75e377] [4] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x76a21b] [5] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x71838b] [6] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x46783c] [7] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x476c54] [8] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x44b9ef] [9] /lib/x86_64-linux-gnu/libc.so.6(__libc_start_main+0xe7) [0x7ffa5160db97] [10] /home/xakstreet/XilinxDistr/Vivado/2017.1/bin/unwrapped/lnx64.o/xelab() [0x465621] Done INFO: [USF-XSim-69] 'elaborate' step finished in '1' seconds INFO: [USF-XSim-99] Step results log file:'/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/xproject/gmii_switch.sim/sim_1/behav/elaborate.log' ERROR: [USF-XSim-62] 'elaborate' step failed with error(s). Please check the Tcl console output or '/home/xakstreet/Documents/Xilinx_projects/Vivado17_1/gmii_switch/xproject/gmii_switch.sim/sim_1/behav/elaborate.log' file for more information. ERROR: [Vivado 12-4473] Detected error while running simulation. Please correct the issue and retry this operation. ERROR: [Common 17-39] 'launch_simulation' failed due to earlier errors.

Я вот не пойму - это вивадо симулятор (17.1) так не дружит с систем верилогом или я что-то не так делаю

В файле лога продублирована информация про SIGSEGV - я не знаю что это за сигнал =/

(https://github.com/xakstreet/gmii_switch - вот сам проект для которого этот файл симуляции)

как-то я много понаписал лишнего - суть вопроса в том - использует ли кто в вивадо task в интерфейсах и вызывал ли параллельно 2 task через 2 interface одного типа? Ест ли это симулятор вивадо или надо перейти на моделсим?

P/S Проблема выявлена - нельзя class.randomize делать внутри процесса, который внутри интерфейса. Если вынести класс из task, а операцию randomize проделывать отдельно не в interface, то вроде как все работает

interface gmii_interface_io_outer (input clk, gmii_interface_io.master port); frameParameters fT = new; modport sendData(import send_rx_frame); task send_rx_frame(input logic [47:0] MAC_SRC_VAL, input logic [47:0] MAC_DST_VAL); $display("Shrinked = %d, Size = %d", fT.shrinked_preamble, fT.frame_length); port.rx_dv = 0; port.rx_err = 0; port.rxd = 8'h00; for(int i=0;i<12;i++)begin : send_interframe @(posedge clk); port.rx_dv = 0; port.rx_err = 0; port.rxd = 8'h55; end for(int i=0;i<(6+fT.shrinked_preamble);i++)begin : send_preamble @(posedge clk); port.rx_dv = 1; port.rx_err = 0; port.rxd = 8'h55; end @(posedge clk);//end of preamble port.rx_dv = 1; port.rx_err = 0; port.rxd = 8'hD5; for(int i=0;i<6;i++)begin : send_MAC_dst @(posedge clk); port.rx_dv = 1; port.rx_err = 0; if (fT.frame_type==BROADCAST_P) begin port.rxd = 8'hFF; end else begin port.rxd = MAC_DST_VAL[i*8+:8]; end end for(int i=0;i<6;i++)begin : send_MAC_src @(posedge clk); port.rx_dv = 1; port.rx_err = 0; port.rxd = MAC_SRC_VAL[i*8+:8]; end for(int i=0;i<fT.frame_length;i++)begin : send_payload @(posedge clk); port.rx_dv = 1; port.rx_err = 0; port.rxd = $urandom(); end @(posedge clk);//end of packet port.rx_dv = 0; port.rx_err = 0; port.rxd = 8'h55; endtask : send_rx_frame endinterface: gmii_interface_io_outer initial begin : sender_0 @clk_start;//wait phase initialize gmii_flow_0.fT.randomize; gmii_flow_0.sendData.send_rx_frame(20,40); end initial begin : sender_1 @clk_start;//wait phase initialize gmii_flow_1.fT.randomize; gmii_flow_1.fT.randomize; gmii_flow_1.sendData.send_rx_frame(20,40); end

Извиняюсь за сумбур, проблему-то решил, но причины возникновения не понял

Лимитирование полосы AWGN

в Алгоритмы ЦОС (DSP)

Опубликовано · Пожаловаться

Спасибо! Помоделировал - действительно результаты хорошие, буду знать теперь