Halfback

-

Постов

424 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Halfback

-

-

Опубликовано · Изменено пользователем Halfback

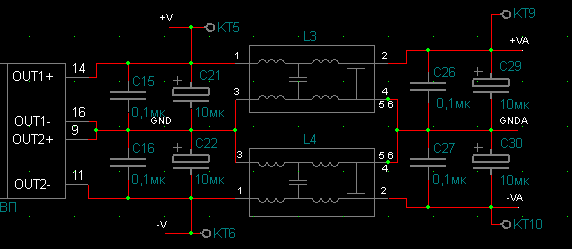

корр · ПожаловатьсяВсем доброго дня!

Как BNX026 правильно подключать в цепи отрицательного напряжения питания?

То как нарисовано на схеме это правильно? А то есть сомнения.... Заранее спасибо!

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

В 09.01.2023 в 09:30, dimka76 сказал:Документ для нагрузки токовых выходов рекомендует резисторы сопротивлением 50 Ом. У вас в два раза выше.

Поставьте 50 Ом вместо ваших 100 Ом. Уберите операционник. И посмотрите, что будет на выходе ЦАП (на нагрузочных резисторах).

Если все нормально, то тогда вернетесь к операционнику.

на выходе ЦАПа и так всё нормально. Номинал токовых резисторов всего лишь отвечают за размах выходного сигнала, поскольку выход ЦАПа токовый.

Plain , тау

спасибо что разжевали, буду ставить AD8054, подходит пин2пин, у него 145В/мкс, резисторы которые сейчас 10к тоже сильно уменьшу.

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

Спасибо что откликнулись.

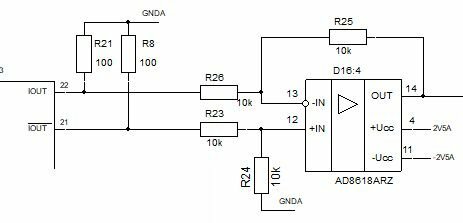

ЦАП DAC904, в даташите на дифф усилитель у него OPA680 нарисован c полосой 300МГц. Я поставил ОУ с полосой более чем в 10 раз меньше.

В общем попробую заменю 10к на 100 Ом. Если не поможет то буду думать что ставить на замену из soic14 и pin2pin.

И вот всё равно до конца не могу понять на счет ОУ - с какой полосой надо брать ОУ если заранее известно синусоиду какой частоты надо пропускать с усилением =1? Какой запас брать? В 10 раз? ))

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

Всем доброго времени суток.

Не могу понять в чем проблема: с выхода ЦАП подаю пачку 5МГц синуса на вход дифф. усилителя ОУ с Ку=1 по схеме.

На выходе 21 и 22 ЦАП постоянный уровень 1В и синус 20 периодов по 5Мгц (в противофазе), амплитудой 1В, период повторения пачки каждую секунду.

На 12 ноге виду только постоянную составляющую = 0,5В. Синуса нет.

На 13 ноге какие-то постоянные автоколебания.

На 14-й ноге вообще непойми что.

Не понимаю с чего вдруг. По описанию ОУ вроде как быстрый, частота единичного усиления аж 24МГц.

Такое подозрение что ОУ по скорости не справляется. Но почему?

-

В 02.12.2022 в 15:56, byRAM сказал:

У нас даже такой финт ушами не прокатил бы, если изделие уже в серии и прошло все испытания.

Мне кажется, что лучше сразу определиться с производителем резисторов, дабы не было проблем с ВП.

Изделие разрабатывается, пока даже литеры нет.

ситуация в том, что

-Р1-8В быстрее производятся, они в целом получше чем Р1-12, но Р-12 есть заполненный склад;

-с керамикой вообще ситуация ох и ах. На чипы К10-79 и К10-83 заявки уже давно не принимают, поставляют только белорусы монолит свои К10-84В где есть куча "НО!"

такая же ситуация к танталами. lowESR заявки также не принимают. На выставке в сентябре их представитель жалостливо жаловался на нелегкую жизнь. Интересно, а кто этим паразитам мешал в последние жирные годы освоения ОКР самим научиться делать материалы а не привозить из-за кардона.

В новое изделие хочется заложить максимум возможностей для маневра в части мелких ПКИ. Но так чтобы это выглядело адекватно.

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

В 02.12.2022 в 12:18, byRAM сказал:Всё зависит от того, насколько серьёзный у вас на предприятии нормоконтроль, если он есть.

Где его нет, всё просто: типоразмер, мощность, номинал, допуск и другие характеристики, если нужно.

НК есть но не сильно образованный в гост 2.7ХХ

но есть ВП который в случае каких-то вопросов может посмотреть КД, и в этой связи хотелось бы чтобы было написано что-то вменяемое.

Сейчас у каждого резистора сделана запись в примечании, внизу в примечании написал что допускается установка с резистора с таким же номиналом, типоразмером и процентовкой, а остальные параметры - не хуже.

ВОпрос в том есть ли способ описать сей момент более изящным способом.

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

У кого есть опыт как в ПЭ3 лучше/правильно сделать запись, например, что по всем резисторам что допускается замена на "аналогичные" по характеристикам?

Дело в том, что писать на каждый резистор Р1-12 допустимую замену Р1-8В (а то может и еще какие, в т.ч. импорт) это мне видится не самым рациональным решением.

Понятно, что замену со 100% совпадением характеристик в случае необходимости применить не получиться. Т.е. у чип-резистора такие характеристики как номинал, процентовка отклонения сопротивления и тип корпуса у аналога должны совпадать, а вот скажем ТКС д.б. не хуже, на тип упаковки и наличие маркировки - пофигу.

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

А есть что-нибудь отечественное вменяемое MII/RMII -> PHY Eth10/100 на один канал?

До этого с применяли 1986ВЕ1, теперь шиш

-

Разобрался самостоятельно.

По непонятным причинам была установлена галочка "Promote critical warnings messages to error messages" в меню Квартуса Tools->Options->Messages

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

Камень Cyclone III EP3C16

Год назад собирал проект. Сохранил, заархивировал. Да, были проблемы с таймингами но проект собирался и даже более-менее работал в железе.

Открыл намедни данный проект - собираться перестал.

Квартус по прошествии времени не трогал.

Но решил его переустановить. После переустановки всё абсолютно также.

Стал писать вот такую тему:

Error (332148): promoted from Critical Warning: Timing requirements not met

Error: Quartus II 64-Bit TimeQuest Timing Analyzer was unsuccessful. 2 errors, 3 warnings

Error: Peak virtual memory: 4893 megabytes

Error: Processing ended: Mon Oct 10 14:05:12 2022

Error: Elapsed time: 00:00:12

Error: Total CPU time (on all processors): 00:00:18

Error (293001): Quartus II Full Compilation was unsuccessful. 4 errors, 36 warnings

Вопрос в президиум - как такое может быть? Вмешательство в проект исключены.

-

Всем доброго времени суток.

Вопрос следующий: допустим в ВЧ схеме есть соотв. ВЧ узлы: смесители, УПЧ, синтезаторы для ПЧ. Видел вскрытые трансиверы именитых производителей, функциональные узлы на плате сделаны в виде отдельных зон, по периметру каждой зоны сделан "земляной" слой с открытой маской. При этом в верхней стыкуемой с платой металлической крышке корпуса сделана фрезеровка т.о., что внутренние стенки жёстко касаются тех самых открытых от маски земляных слоев. Таким образом выполнено экранирование конкретных функциональных узлов. ОК.

Но что не понятно - как правильно делаются "земляные" контура в подобных платах? Земляной контур, получается, заливается общий на всю плату?

Опыта в таких делах нет, литературы "правильной" не нашел.

Прошу дать рекомендации по моему вопросу.

-

Есть желание использовать один пьезодиск как на прием так и на передачу. Вот интересно крепить пьезодиск с учетом обеспечения механического демпфера (как выше изложил г-н Plain , для уменьшения остаточных колебаний) - так вот видел в некоторых иностранных подводных проборах: пьезодиск диаметром ~15мм залит/запрессован на самом краю некоего цилиндра диаметром ~20мм длиной ~40мм, вещество из которого сделан цилиндр на ощуп напоминает оргстекло. Что это мб за материал? Может какой-то хитрый компаунд?

-

7 минут назад, vladec сказал:

Пьезоэлектрика хорошо работает на резонансных частотах, представляется, что при таких расстройках она работать хорошо не будет.

спасибо что откликнулись. Я понимаю что на границах полосы резонанса будут завалы.

Мне пока не понятно какой сигнал подавать на пьезопластину. По Вашей ссылке микрочиповский драйвер высоковольтных импульсов. Хотелось бы увидеть временные диаграммы отклика ультразвуковой пьезопластины на импульс/импульсы. Я планирую научиться генерировать импульс вполне определенной длительности, желательно без остаточных затуханий и т.п. Хотелось бы еще понять можно ли на пьезопластине сгенерировать ультразвук с изменяющейся на 180 градусов фазой. Я к тому что может на высоковольтных импульсах этого не получиться сделать, а понадобиться ЦАП, ФНЧ и что-то вроде звукового усилителя но на мегагерцы.

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

Всем доброго дня.

Хочу попробовать кое что смастерить по гидроакустике, сделать свой простенький сонарчик )))

Есть керамическая пъезопластина на резонанс 2,4 МГц, с али.

Вопрос - каким образом с нее можно получить ультразвуковой импульс определенной длительности на резонансной частоте? А если надо получить ЛЧМ на 2.4МГЦ +/- 400кГц ?

Измеряемая дальность - десятки сантиметров.

Как это вообще работает? К пьезопластине припаяно 2 провода. Какое воздействие надо подать что получить то что мне нужно?

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

23 минуты назад, mantech сказал:А за нас не переживайте, Китай никуда не делся, работаем и не жужжим...

А я как вижу все не жужжат, зачастую переплачивая китайским перекупам. Вот в РФ парни заложили в проект STM32L4xx по 400р/шт (прайс на пол года назад) - а теперь (точнее месяц назад) китайские друзья предлагают его за 90$/шт и с непонятными перспективами при дальнейшем серийном производстве. Хошь не хошь а отечку придётся теперь рассмотреть.

-

Господа, есть кто использует данный МК? Как впечатления?

А то 8 страниц флуда по теме цены и импортозамещения. Интересно как сейчас поют разработчики из РФ когда импортные МК либо не купить либо за них ломят 10-кратно, в лучшем случае.

Интересует вот еще что - МК производиться, как я понял, с 2016 года. Эррата последняя датируется 2017 годом. В выпускаемых/продаваемых сейчас образцах исправлены ошибки? Или НИЭТ забил на это болт? А то прочитал про USB EndPoint 3,4 и как-то даже улыбнуло )))

-

19 часов назад, x893 сказал:

MPU-9250 и пишете программу для DMP

Спасибо за вариант.

Но хотелось бы реализацию попроще и с меньшим потреблением.

Разве нет таких вариантов мемс датчиков, где просто говоря - записываешь в регистр значение угла наклона при котором возникнет прерывание и всё работает...

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

Доброго времени суток.

Нужно чтобы датчик сам смог бы вычислять угол наклона и формировать импульс (прерывание):

-либо по превышению какого-либо (заранее заданного) угла наклона. Точность высокая не нужна, 1-2град будет достаточно.

-либо по определенной (заранее заданной) силе удара.

Такие датчики вообще бывают? Понимаю что можно поставить малошумящий акселлерометр и подцепить к нему МК но к сожалению нет возможности чтобы все время работал МК и вычислял эти события.

Заранее спасибо!

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

18 часов назад, Zig сказал:Options - Selection Mask... - Block Selections - Clear All - Галку в поле Cu Pour - Outside Block - Set All (Layers) - Ok

Ctrl + 1, ЛКМ за пределами платы со смещением мыши (слегка), ПКМ - Pour/Repour

Круто, спасибо! Идею я понял. ТОлько не понятно что делает Ctrl + 1

Я так понимаю на это дело можно сделать макрос записать. Где можно взять справочник по ключевым комбинация клавиш?

-

Всем доброго времени суток.

PCAD 2006SP2, есть плата, на которой куча контуров Copper Pour на разных слоях.

После наложения нетлиста каждый раз приходиться контурам делать Pour/Repour. Причем в определенной последовательности.

Можно ли как-то этот неинтересный процесс автоматизировать? Если можно то как? Заранее спасибо!

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

11.11.2021 в 09:55, des00 сказал:ЗЫ. Скачайте учебник по ЦОС от альтеры, там в разделе фильтров много крайне полезной информации

Не поделитесь ссылкой или как в гугле поискать? Пока в поисковике вижу только Altera DSP Builder, но как я понимаю это не то что мне нужно...

10 часов назад, Maverick_ сказал:обратите внимание еще на

обратил. У меня для Cyclone III (Quartus 13.0.1) нет такого примера, но есть вот такой темплейт для DSP Features/Sum of Four Multipliers (Stratix V, Arria-V, Cyclone-V and later device families)

Мне не совсем понятно чем эта реализация отличается от моей. Если разница есть то ткните пожалуйста.

Скрытый текст// Quartus II Verilog Template // Sum of four multipliers // For use with the Stratix V, Arria-V, Cyclone-V and later device families module sum_of_4(a1, b1, a2, b2, a3, b3, a4, b4, p); //This template is applicable to sum-of-4 18x18 mode on Stratix-V parameter a_width = 18; parameter b_width = 18; input [a_width-1:0] a1; input [b_width-1:0] b1; input [a_width-1:0] a2; input [b_width-1:0] b2; input [a_width-1:0] a3; input [b_width-1:0] b3; input [a_width-1:0] a4; input [b_width-1:0] b4; output [a_width+b_width+1:0] p; wire signed [a_width-1:0] a1; wire signed [b_width-1:0] b1; wire signed [a_width-1:0] a2; wire signed [b_width-1:0] b2; wire signed [a_width-1:0] a3; wire signed [b_width-1:0] b3; wire signed [a_width-1:0] a4; wire signed [b_width-1:0] b4; wire signed [a_width+b_width+1:0] p; //Static add/sub is supported assign p = a1 * b1 + a2 * b2 - a3 * b3 + a4 * b4; endmodule

есть еще вот такой темплейт Sums of Multipliers (я так понял для плис помедленнее). Я таким образом тоже реализовывал - умножение с суммированием в виде отдельного модуля, где то-же самое делалось по клоку. Но ситуация со слеками никак не изменилась. Еще непонятно - целенаправлено ли скобки т.о. расставлены или нет.

Скрытый текст// Quartus II Verilog Template // Sum of four multipliers module sum_of_four_multipliers #(parameter WIDTH=18) ( input clk, ena, input [WIDTH-1:0] dataa, datab, datac, datad, input [WIDTH-1:0] datae, dataf, datag, datah, output reg [2*WIDTH+1:0] dataout ); always @ (posedge clk) begin if (ena == 1) begin dataout <= (dataa * datab + datac * datad) + (datae * dataf + datag * datah); end end endmodule

-

Опубликовано · Изменено пользователем Halfback · Пожаловаться

Всем доброго времени суток!

Реализовал полифазный децимирующий фильтр на 70 точек (на выходе каждая 10-я точка относительно входа), в моделсиме показывает всё как надо, в железе на столе тоже работает, но квартус валит слэки по Setup (Slow 1200mV 0C и +85С, по Fast - слэков нет).

Причем в sdc когда ставлю 80МГц - слэков нет, на 100МГц еже есть.

Буду очень признателен если поможете найти плохое место в коде. Может есть возможность что-то поправить/улучшить?

Скрытый текстmodule PoliPhaseFilter_70 ( input clk, input signed [15:0] datain, input nreset, output signed [15:0] dataout, output clkDec // выходной клок синхр. данных ); localparam BANK_NUM = 10; localparam VALUE_NUM = 7; //регистры с входными данные reg signed [15:0] BANK_D0[BANK_NUM-1:0]; reg signed [15:0] BANK_D1[BANK_NUM-1:0]; reg signed [15:0] BANK_D2[BANK_NUM-1:0]; reg signed [15:0] BANK_D3[BANK_NUM-1:0]; reg signed [15:0] BANK_D4[BANK_NUM-1:0]; reg signed [15:0] BANK_D5[BANK_NUM-1:0]; reg signed [15:0] BANK_D6[BANK_NUM-1:0]; reg signed [15:0] BANK_C [BANK_NUM-1:0][VALUE_NUM-1:0]; //коэффициенты полифазного фильтра reg signed [31+3+4:0] RESSUMM = 0; // промежуточная сумма reg signed [31+3+4:0] RESSUMM_out = 0; // итоговая сумма -> на выход фильтра reg rclkDec = 0; integer i; reg [3:0] step=0; // 10 шагов //результаты перемножений значений данных на коэфф фильтра wire signed [15:0] mult0_1, mult0_2, mult1_1, mult1_2, mult2_1, mult2_2, mult3_1, mult3_2, mult4_1,mult4_2,mult5_1,mult5_2,mult6_1,mult6_2; //сумма результатов перемножений wire signed [31+3:0] resmult1; assign resmult1 = mult0_1*mult0_2 + mult1_1*mult1_2 + mult2_1*mult2_2 + mult3_1*mult3_2 + mult4_1*mult4_2 + mult5_1*mult5_2 + mult6_1*mult6_2; initial begin //обнуление всех регистров, формирование коэффициентов for(i = 0; i < BANK_NUM; i=i+1) begin BANK_D0[i]<=0; BANK_D1[i]<=0; BANK_D2[i]<=0; BANK_D3[i]<=0; BANK_D4[i]<=0; BANK_D5[i]<=0; BANK_D6[i]<=0; end RESSUMM <= 0; RESSUMM_out <= 0; BANK_C[0][0]= -16'd293; BANK_C[0][1]= -16'd1513;BANK_C[0][2] = 16'd3442; BANK_C[0][3] = 16'd16735;BANK_C[0][4] = 16'd15664;BANK_C[0][5] = 16'd2358; BANK_C[0][6] = -16'd1445; BANK_C[1][0]= -16'd278; BANK_C[1][1]= -16'd1518;BANK_C[1][2] = 16'd4646; BANK_C[1][3] = 16'd17631;BANK_C[1][4] = 16'd14446;BANK_C[1][5] = 16'd1407; BANK_C[1][6] = -16'd1331; BANK_C[2][0]= -16'd396; BANK_C[2][1]= -16'd1446;BANK_C[2][2] = 16'd5952; BANK_C[2][3] = 16'd18326;BANK_C[2][4] = 16'd13114;BANK_C[2][5] = 16'd596; BANK_C[2][6] = -16'd1185; BANK_C[3][0]= -16'd534; BANK_C[3][1]= -16'd1279;BANK_C[3][2] = 16'd7340; BANK_C[3][3] = 16'd18800;BANK_C[3][4] = 16'd11702;BANK_C[3][5] = -16'd74; BANK_C[3][6] = -16'd1022; BANK_C[4][0]= -16'd688; BANK_C[4][1]= -16'd1003;BANK_C[4][2] = 16'd8781; BANK_C[4][3] = 16'd19041;BANK_C[4][4] = 16'd10247;BANK_C[4][5] = -16'd604; BANK_C[4][6] = -16'd854; BANK_C[5][0]= -16'd854; BANK_C[5][1]= -16'd604; BANK_C[5][2] = 16'd10247;BANK_C[5][3] = 16'd19041;BANK_C[5][4] = 16'd8781; BANK_C[5][5] = -16'd1003;BANK_C[5][6] = -16'd688; BANK_C[6][0]= -16'd1022;BANK_C[6][1]= -16'd74; BANK_C[6][2] = 16'd11702;BANK_C[6][3] = 16'd18800;BANK_C[6][4] = 16'd7340; BANK_C[6][5] = -16'd1279;BANK_C[6][6] = -16'd534; BANK_C[7][0]= -16'd1185;BANK_C[7][1]= 16'd596; BANK_C[7][2] = 16'd13114;BANK_C[7][3] = 16'd18326;BANK_C[7][4] = 16'd5952; BANK_C[7][5] = -16'd1446;BANK_C[7][6] = -16'd396; BANK_C[8][0]= -16'd1331;BANK_C[8][1]= 16'd1407; BANK_C[8][2] = 16'd14446;BANK_C[8][3] = 16'd17631;BANK_C[8][4] = 16'd4646; BANK_C[8][5] = -16'd1518;BANK_C[8][6] = -16'd278; BANK_C[9][0]= -16'd1445;BANK_C[9][1]= 16'd2358; BANK_C[9][2] = 16'd15664;BANK_C[9][3] = 16'd16735;BANK_C[9][4] = 16'd3442; BANK_C[9][5] = -16'd1513;BANK_C[9][6] = -16'd293; end //initial always @ (posedge clk) begin if(nreset==1'b0) begin RESSUMM <= 0; RESSUMM_out <= 0; step <= 0; for(i = 0; i < BANK_NUM; i=i+1) begin BANK_D0[i]<=0; BANK_D1[i]<=0; BANK_D2[i]<=0; BANK_D3[i]<=0; BANK_D4[i]<=0; BANK_D5[i]<=0; BANK_D6[i]<=0; end end else begin //формирование строба для чтения выходного регистра if(step==0) rclkDec <= 1; if(step==5) rclkDec <= 0; BANK_D0[step] <= datain; // // сдвигаем данные BANK_D6[step]<=BANK_D5[step];BANK_D5[step]<=BANK_D4[step];BANK_D4[step]<=BANK_D3[step]; BANK_D3[step]<=BANK_D2[step];BANK_D2[step]<=BANK_D1[step];BANK_D1[step]<=BANK_D0[step]; case (step) 0,1,2,3,4,5,6,7,8: begin step <= step + 4'd1; RESSUMM <= RESSUMM + resmult1; end 9: begin step <= 4'd0; RESSUMM_out <= RESSUMM + resmult1;// формируем выход RESSUMM <= 0; end endcase end //else if end //always assign clkDec = rclkDec; assign mult0_1 = BANK_D0[step]; assign mult0_2 = BANK_C[step][6]; assign mult1_1 = BANK_D1[step]; assign mult1_2 = BANK_C[step][5]; assign mult2_1 = BANK_D2[step]; assign mult2_2 = BANK_C[step][4]; assign mult3_1 = BANK_D3[step]; assign mult3_2 = BANK_C[step][3]; assign mult4_1 = BANK_D4[step]; assign mult4_2 = BANK_C[step][2]; assign mult5_1 = BANK_D5[step]; assign mult5_2 = BANK_C[step][1]; assign mult6_1 = BANK_D6[step]; assign mult6_2 = BANK_C[step][0]; assign dataout = RESSUMM_out[33:18]; // обрезаем выходной регистр сверху и снизу для получения нужных 16 бит endmodule

-

разобрался, то что LVDS имеет только 5578ТС104 и 5578ТС064.

ВОпрос к счастливым обладателям 5578ТС104 - возможна ли работа LVDS на прием на скорости 120МГц ? ЧТо с регистрами LVDS приемника? Будет всё работать как в Cyclone III ?

-

Всем доброго дня. Скажите пожалуйста, плис 5578ТС084 имеет LVDS ?

И еще вопрос в догонку - где можно взять документацию на 5578ТС084 ? Надо платку под эту плис спроектировать...

Замена э/м реле на твердотельное для низковольтовых сигналов

в Схемотехника

Опубликовано · Пожаловаться

Всем доброго дня.

Для коммутации низковольтовых сигналов (до -30дБ) использовал обычные релюшки. Сейчас есть мысль попробовать твердотельные реле. Посмотрел даташит омрон, G3VM - там в обвязке полевика с изолированным затвором стоят встречные диоды. Это напрягло.

МОжет есть твердотельные реле как раз предназначенные для коммутации слабеньких сигналов с гальванически-развязанным управлением? Э/м реле всем устраивает, но есть желание идти в ногу со временем.