vitaly_n

Участник-

Постов

103 -

Зарегистрирован

-

Посещение

-

Проблема с Zynq HP

vitaly_n опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую! Дано: Zynq 7010. Сделано простенькое тренировочное приложение RTL на VHDL, реализующее AXI4-Lite slave (регистры, через которые задаётся управление) и AXI3 master для прямого доступа к DDR памяти через HP. И вот в чём проблема. Запрос на чтение уходит. Через положенное время прилетает ответ. Сколько слов (по 64 бита) просил - столько и прилетает, вот только все они одинаковые и равны первому слову. Выглядит всё так, как будто ARBURST=00 (что означает FIXED), хотя он точно =01 (INCR). Что за напасть и как её победить? -

Импортозамещение

vitaly_n ответил vitaly_n тема в Компоненты

Заказал на AliExpress несколько штук отладочных плат nRF52832 - вот на них и обнаружил. Ещё там оказался глюк с SPI/TWI - он нормально не отключается, продолжает жрать 1 ма, впрочем, в errata описано, как это потом отключить через недокументированные регистры. -

RDI specification

vitaly_n опубликовал тема в Cредства разработки для МК

В связи с тем, что я не смог найти в интернетах RDI драйвер для Digilent HS2 (под Windows), предположительно, потому что такого никто ещё не делал, возникла у меня дурацкая мысль самому его написать. Однако, несмотря на то, что спецификация на RDI вроде бы открытая, я не смог её найти. Поэтому просьба к уважаемому собранию - кто может поделиться оной спецификацией? Хотя бы чтобы оценить трудоёмкость задачи... -

ECC с "подсказкой"

vitaly_n ответил vitaly_n тема в Математика и Физика

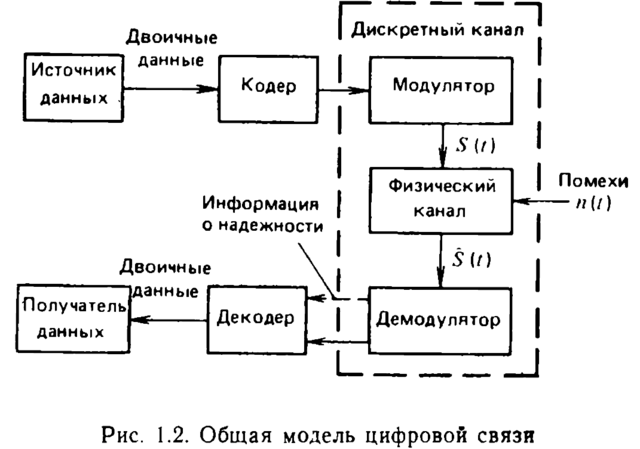

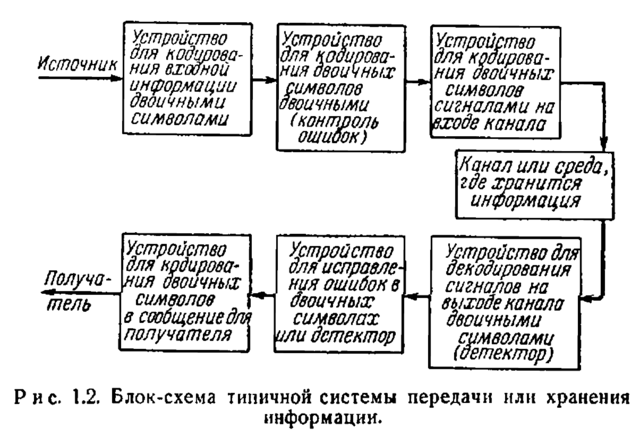

Решил вернуться к этой теме, чтобы закрыть её. В общем, вот две картинки. Первая - стандартная модель системы передачи или хранения информации, которая идёт в книжках по помехоустойчивому кодированию начиная чуть ли не с самого Шеннона, конкретно эта - из книги У.Питерсона "Коды, исправляющие ошибки", М., "Мир", 1964. Вторая - из книги Дж.Кларк, Дж.Кейн "Кодирование с исправлением ошибок в системах цифровой связи", М. "Радио и связь", 1987. Если внимательно присмотреться, то можно заметить, что во втором случае от демодулятора к декодеру идут две стрелочки - одна сплошная обозначает основной поток информации, а вторая пунктирная обозначает дополнительную информацию, которую я и имел в виду в первом сообщении про "подсказку". Как я правильно ощущал, я таки пытался "изобрести велосипед", и этот "велосипед" в данном случае называется код Рида-Соломона. В этом коде дополнительная информация называется "стирание", и обозначает она то, что демодулятор сразу помечает, что принятый символ был настолько плохого качества, что сразу понятно, что его проще выбросить, чем пытаться декодировать. А польза тут вот в чём. Например, возьмём код Рида-Соломона (15,9) (информация передаётся пакетами из 15 символов по 4 бита в каждом, из которых 9 - символов информационные, а 6 - проверочные). Согласно учебнику, этот код может исправлять до 3 ошибок, если у нас нет дополнительной информации от демодулятора. Однако, если у нас есть информация от демодулятора о том, в каких именно символах точно будут ошибки, то помеченных стираний этот код может исправить вдвое больше - скажем, 2 ошибки и 2 стирания или 1 ошибку и 4 стирания. -

Самое простое - взять любой блочный шифр и использовать его в counter mode. Как вариант - использовать криптографический хэш от номера блока и ключа. Дальше можно либо последовательно выдавать биты получившегося блока в канал, либо вообще использовать только младший или старший бит от блока.

-

При чём тут NRZ? Помехоустойчивость достигается прежде всего за счёт Eb/N0, и только потом уже работает кодирование, когда вероятность приёма ошибочного бита и так невелика. Синхронизация вообще всему этому ортогональна, причём, битовая синхронизация и блоковая достигаются и поддерживаются разными способами.

-

Вот тут у меня и возникает вопрос - можно ли вот так расширять понятие "систематического кода"...

-

Лучше скажите мне, кто как полагает, этот код можно назвать "систематическим"? С одной стороны, если подходить формально именно на уровне отдельных битов, то такой четвёрки битов, чтобы однозначно соответствовала номеру кодового слова, тут нету. Однако, если смотреть на триплеты как троичные символы, то тогда первые два триплета прямо задают кодовое слово, а третий и четвёртый однозначно вычисляются из первого и второго триплета... В общем, непонятки.

-

Покорнейше благодарю за благожелательный отзыв!

-

Корректирующий равновесный код 4B12B с синхронизацией

vitaly_n опубликовал тема в Алгоритмы ЦОС (DSP)

Вниманию почтеннейшей публики предлагается код 4B12B. Как легко догадаться из названия, длина кодового слова 12 бит. Мощность кода - 18 слов, т.е. можно передавать 4 бита на слово плюс ещё два комма-слова (назовём их K0 и K1) для синхронизации. Rate = 1/3, что не так уж и плохо по сравнению с комбинациями кодов, чтобы набрать такой же набор свойств. Свойства: 1) DC-free. Количество 0 и 1 в потоке одинаковое - это для возможности пользоваться гальваноразвязкой. 2) RLL = 4. В потоке не встречается более 4 одинаковых бит подряд. Это полезно для поддержания битовой синхронизации. 3) Running Disparity <= 2 и каждые 6 бит баланс восстанавливается. Это тоже полезно для гальваноразвязки. 4) Кодовое расстояние = 6, т.е. корректирует до 2 ошибок в слове, обнаруживает 3 ошибки, некоторые слова с 3 ошибками можно однозначно исправить. 5) Конкатенация K0 и K1 имеет минимальное расстояние Хэмминга 4 до любого стыка любых других кодовых слов, т.е. её можно использовать для блоковой синхронизации даже с одним ошибочным битом. 6) Ошибок синхронизации (потери бита или вставки бита) не исправляет, но позволяет потерю блоковой синхронизации достаточно быстро обнаруживать. 7) При реализации в FPGA скромен по части ресурсов. Конструкция равновесных корректирующих кодов с синхронизацией -

Импортозамещение

vitaly_n ответил vitaly_n тема в Компоненты

Вот тут не соглашусь. В первую очередь - организационные. Пока начальство не может, не хочет и не понимает, никакие технические проблемы не могут быть решены, даже если ИТР могут и хотят. -

Импортозамещение

vitaly_n ответил vitaly_n тема в Компоненты

Тогда и сейчас - две огромные разницы, объяснение которой тут лютый оффтопик. -

Импортозамещение

vitaly_n ответил vitaly_n тема в Компоненты

BMTI http://www.casc-bmti.com/n1926/n1930/n1932/index.html http://www.casc-bmti.com/n1927/n1940/n1978/index.html -

Импортозамещение

vitaly_n ответил vitaly_n тема в Компоненты

Зря Вы делаете такие предположения, ровным счётом ничего о КНДР не зная. Во-первых, климат там заметно суровее, чем в Южной Корее. Во-вторых, местность гористая. Сельскохозяйственных земель в КНДР очень мало - если поделить на население получается 12 соток на душу населения. В-третьих, КНДР находится в крайне жёсткой торговой блокаде - ни одна страна в мире в таких условиях и года бы не прожила, а КНДР не только много лет выживает, но и ракету с ядерным зарядом сделала, а это венец целого букета весьма продвинутых технологий. https://felix-edmund.livejournal.com/570256.html Пардон за оффтопик.