videoscan

Участник-

Постов

58 -

Зарегистрирован

-

Посещение

Весь контент videoscan

-

Ошибка а Cosimulation (Vivado, HLS)

videoscan опубликовал тема в Среды разработки - обсуждаем САПРы

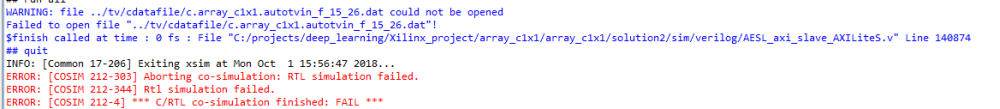

Народ! Имеется следующая ситуация. В Vivado, на HLS (Си), написана некая программа. Simulation и Synthesis проходит нормально. На этапе Cosimulation происходит ошибка (см. аттач). В тексте ошибки (см. выше) говорится, что не может открыть файл. Я проверил, файл есть, ничем от других подобных не отличается. Методом тыка определил, что Cosimulation не нравится большое число объявленных блоков памяти. Если его уменьшить (границы не нашел, но где-то около 500), все срабатывает. Кто-нибудь сталкивался с этим? Как бороться? У меня Vivado 2017.4 и Windows 7. Ресурсы FPGA не превысил. Чип - XCVU9P. -

Вы совершенно правы! Этот AXI BRAM Controller решает нашу проблему. Спасибо! Прошу прощения за дальнейший поток сознания.

-

Но если он создаст 3 экземпляра Function4, то к каждому их них он присоединит по одному экземпляру kernel и все останется по-прежнему. Но будет время - попробую.

-

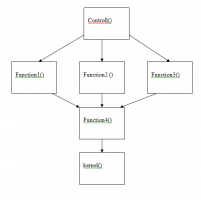

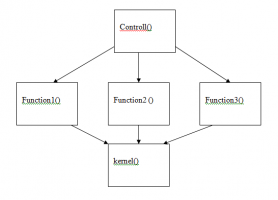

Т. е. так как на рис? А что помешает Vivado создать заодно и 3 экземпляра Function4 ? На самом деле решение есть: слить все 3 функции Function1-Function3 в одну здоровую и там сказать с помощью ALLCATION, что kernel нужен один, но как это некрасиво! И зачем мы Октябрьскую революцию делали, Си используем?

-

Народ! Проблема следующая. Есть программа на Vivado HLS со структурой как на рисунке: Верхняя функция - controll, в вызывает 3 разные подпрограммы function1, function2 и function3. Те в свою очередь обращаются к одной функции kernel, где происходит обработка данных. Функция kernel должна быть одна (на уровне RTL), потому как ресурсов она жрет немерено (1024 одних DSP блоков). Vivado HLS на этапе Sinthesis делает 3 RTL копии этой функции. Директива Allocation не помогает, она видит только функции в той подпрограмме, в которую вставлена. Кто-нибудь с этой проблемой сталкивался? Это решаемо?

-

Получается из HLS модуля торчит 6 * 32 ap_memoty интерфейсов 2Kx16 каждый из которых цепляется к своему модулю BRAM объявленному снаружи HLS. Пошли разбираться. Спасибо!

-

Имеется 6 буферов памяти 256*256 слов по 2 байта. Каждый из этих буферов делится директивой ARRAY_PARTITION на 32 куска (с опцией cyclic). В эту память нужно очень быстро принимать данные из DDR4. Обработка данных производится на модуле, написанном на HLS. Память организована с внешним интерфейсом ap_memory. На уровне ощущений мне кажется, что использование AXI в интерфейсе памяти затормозит работу вычислителя (а это для нас критично). Однако мы попробовали. При попытке организовать интерфейс этой памяти как AXI (директивами INTERFACE с опцией s_axi) Synthesis делается очень долго (реально я не дождался его конца, ждал 4 часа). С использованием ap_memory Synthesis проекта делается за 2-5 минут. Вот и получается, что нам нужно прочесть данные с DDR4 (они идут на AXI) и записать их в память (ap_memory).

-

ap_memory торчит. Сама память объявляется в внешнем VeryLog. С этим пока не разобрался. Думал, может есть какой ip, который это делает или я что-то совсем не понимаю.

-

Я же написал, что использовать AXI BRAM controller не могу. Дело в том, что этих самых контроллеров на блоках BRAM в проекте очень много (около 200) и Vivado HLS не смог мне оттранслировать программу с памятью с интерфейсом AXI при таком их количестве.

-

Народ! Вводные данные: - проект на Xilinx UltraScale+ (боард VCU118); - часть содержимого пишется на HLS, часть на VeryLog. Имеется следующая проблема: - в проекте реализована связь с SDRAM DDR4 с использованием интерфейса AXI (на самом деле пока не реализована, но IP такой функции в Vivado есть); - после того, как мы получили данные с DDR4 нам нужно передать их в память BRAM с обычным внешним интерфейсом (адрес, данные, запись, клок); - сразу скажу использовать в памяти, на которую надо передать данные, интерфейс AXI невозможно, по ряду причин. Пролистал библиотеку IP с AXI - нужного перехода не нашел. Что делать? Есть ли какие мысли? Как вообще данные, живущие в Xilinx на AXI переходят в обычные? Одно решение вроде как есть - использовать в интерфейсе c DDR4 не AXI, а параллельный интерфейс, но в будущем в проект будет добавлен PCI-e, а он только на AXI и работает, так что эту проблему все равно решать надо.

-

В общем я сейчас к этому и склоняюсь.

-

С симулинком не знаком, в МатЛабе не работал.

-

С System Generator совсем не знаком. Боюсь разбрасываться, сейчас что-то стал понимать в HLS, а тут опять куча новой информации. Времени для этого совсем нет. Я наверное попробую продолжать копать в сторону С.

-

В сети нашел видеозаписи вебинаров предыдущих лет (надеюсь ничьих авторских прав не нарушил). Посмотрел. В общем все что там сказано уже освоил, а для совсем начинающих - да полезно.

-

Спасибо. Поучаствую.

-

Решили попробовать на HLS ради ускорения. Алгоритм достаточно сложный, используется практически вся память чипа (ее там 20МБ), нужно чтобы это все тарахтело на хорошей частоте (не менее 100 МГц). Кроме этого алгоритм "живой" в смысле сырой и будет меняться в процессе разработки. Ну и используемый чип огромен, можно плюнуть на ресурсы (кроме памяти).

-

Спасибо за ответ. Полезно поговорить даже с самим собой, а тем более с умным человеком. Решение нашлось. Пришлось производить чтение и запись во внешний блок памяти только в одной функции, используя промежуточную глобальную переменную для передачи данных на запись из другой функции. Начинаю потихоньку понимать требуемый стиль программирования. Директиву DATAFLOW в главной программе оставил и vivado перестал выдавать предупреждения, т.к. видел, что запись и чтение в блок памяти происходят при выполнении разных условий. Исходники не привожу, потому, как описал я проблему в очень упрощенном виде, функций там не 2, а 4 , связаны через память они крест-на крест, блоков памяти не 2 или 4, а штук 50. Такой исходник разобрать сложно. Спасибо. Одна функция обрабатывает данные и передает их другой в качестве входных данных для последующей обработки. Все функции имеют по 2 блока памяти, с одним работают сами, а в другую в это время пишет сосед, потом они переключаются. Для переключения используется глобальная переменная, общая для всех. На самом деле будет массив из 100 функций (10*10), работающих параллельно. Такой требуется алгоритм обработки. Я пришел не из программистов, а из железячников, и писал на VHDL, и привычки, конечно приходится менять.

-

Тогда сформирую вопрос. Возможно в процессе этого и сам пойму. Упрощенно: Есть 2 функции на С. Мне надо чтобы они работали одновременно. Но дело в том, что есть блок памяти (глобальный), используемый обеими функциями. Я сделал так, чтобы использование общей памяти функциями происходило в разные моменты времени и не пересекается, однако vivado этого не понимает и запускает функции последовательно. В головной программе, которая вызывает эти функции я поставил директиву DATAFLOW. Не помогло. При Sythesis выдается предупреждение: WARNING: [XFORM 203-713] All the elements of global array 'b1_1_1' should be updated in process function 'kernel1_0' (kernel_array.c:272), otherwise it may not be synthesized correctly. И после C/RLT Cosimalation симулятор показывает, что функции выполняются последовательно. Бьюсь, ставлю разные директивы - не помогает. Буду благодарен за любые мысли и обсуждение.

-

Народ! Есть ли на форуме спецы по программированию на HLS? Имеется в наличии: - Xilinx Virtex UltraScale+ FPGA VCU118 Evaluation Kit (https://www.xilinx.com/products/boards-and-kits/vcu118.html#hardware); - vivado 2017.4. Нужно написать программу на Си, которая реализует алгоритм расчета, с большой степенью параллелизма. Начинаю осваивать, возникли непонятки. Хочется посоветоваться. Понимаю, что это сплошная экзотика, но может есть живые спецы по этой части.

-

Тоже самое на Altera. Побеждается ссылками на сайт своей фирмы, причём адрес почты должен быть фирменный (нельзя использовать yandex, google и т.д. ящики). Возможно проводится проверка на отсутствие предприятия в списке санкционных.

-

Знак комментария # На остальные вопросы отвечать недостаточно компетентен. Я бы порекомендовал другие статьи этого же автора (много общего, но есть и отличия)

-

Скажите, а у Verylog HDL по этой части по другому?

-

Сегодня до вечера занят. Только после 20 или завтра с утра. Можно, нужно только перейти в режим отображения, который называется Expended time deltas mode.

-

Блок-схему, я конечно нарисовал, но соглашение о названии сигналов подписать забыл. Сейчас разбираюсь.

-

Не всегда это удобно и даже возможно, но что делать. Сейчас как раз этим и занялся.