Поиск

Показаны результаты для тегов 'registers'.

-

Синхронизаторы и Gowin

makc опубликовал тема в Работаем с ПЛИС, области применения, выбор

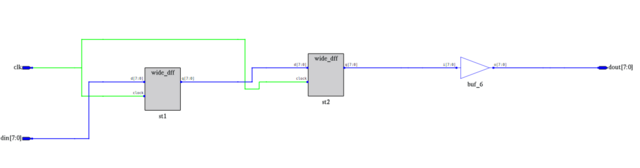

Всем привет! Обнаружилась досадная особенность при синтезе совершенно элементарной конструкции синхронизатора для параллельной шины у Gowin: вместо пары регистров Gowin Synthesis для ПЛИС GW1N-UV9LQ100C6/I5 и других из этого семейства генерирует память и управляющий триггер. При этом, например, для GW1N-LV1LQ100C6/I5 этого не наблюдается. Вот как выглядит пример описания для повторения эксперимента:bus_sync.v RTL после синтеза выглядит красиво и вроде бы мы получили ровно то, что хотели и планировали: Но как бы не так. В нетлисте, генерируемом параллельной с красивой картинкой RTL всё выглядит уже не так безобидно: По сути генерируется память с организацией 2х8 и Т-триггер, который перебирает адрес этой памяти, имитируя поведение сдвигового регистра, которым и является синхронизатор. Всё бы ничего, но это не синхронизатор. Это подтверждает и отчёт об используемых ресурсах, получаемый после синтеза: Hierarchy Module Resource MODULE NAME REG NUMBER ALU NUMBER LUT NUMBER DSP NUMBER BSRAM NUMBER SSRAM NUMBER bus_sync (src/bus_sync.v) 1 - 1 - - 2 В котором SSRAM NUMBER равен двум, а триггеров только один вместо 16 и это само по себе уже наводит на нехорошие мысли, что что-то здесь не так. Поправьте меня, если я не прав да и вообще интересны ваши комментарии по теме синтезатора у Gowin. Я не хочу сказать, что это какая-то ошибка в синтезаторе. Формально он прав, т.к. принял решение сэкономить на триггерах и это неплохо. Но проблема в другом: в штатном асинхронном FIFO IP от Gowin именно через такие "псевдосинхронизаторы" передаются между тактовыми доменами счётчики, считающие в коде Грея. Соответственно из этого я делаю вывод, что разработчики забыли поставить атрибуты syn_srlstyle для этих синхронизаторов и тем самым совершили ошибку.