Поиск

Показаны результаты для тегов 'place'.

-

Vivado P&R. Особенности и подходы

dxp опубликовал тема в Среды разработки - обсуждаем САПРы

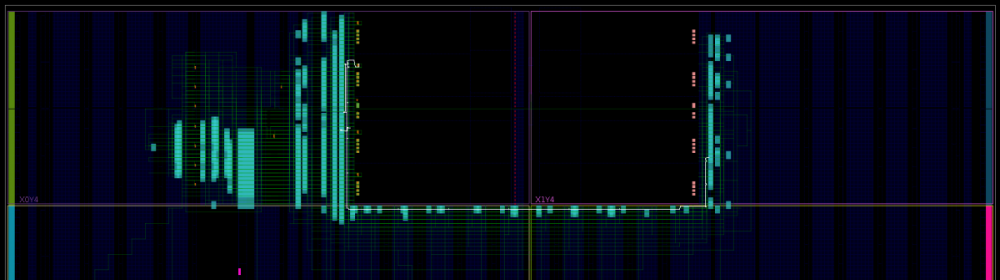

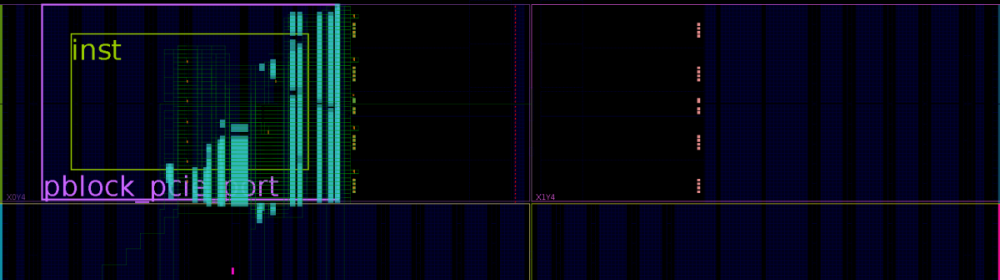

Всем привет! С Xilinx ранее работать серьёзно не приходилось, всё больше была Altera, поэтому нахожусь в процессе набора опыта и познания особенностей FPGA Xilinx и её САПР Vivado. Текущий проект: Artix-7 xc7a200t, Vivado 2018.2. По результатам очередной сборки развалились времянки: тактовый домен 4 нс (250 МГц), слак по сетапу порядка 0.8 нс. Смотрю, на чём просело, вижу, задержку пути на логике 1.269 нс, на трассировке 3.229. Логики там реально немного, поэтому и странно, что не уложилось. Открываю Device, и вижу, что вивада утащила часть логики модуля в другой Clock Region, отсюда и такая конская задержка (плоховато, но видно беленьким показан путь). Никакими изменениями стратегий ситуацию исправить не удалось. Вообще, ситуация представляется достаточно простой - кристалл почти пустой, и места для логики в левом Clock Region и под ним полно. Зачем же плейсер рассовал логику так, что трассировщик потом уже ничего не может исправить? Ну, делать нечего, пришлось применить ручное назначение потрохов модуля в pblock. После этого всё получилось, времянки сошлись и на дивайсе всё выглядит компактно, логично и красиво. Собственно вопрос: это правильный подход и нормальная практика для Xilinx/Vivado или это костыльно и правильно всё же как-то вызвать интеллект САПР из сумрака, чтобы она сама соображала, как размещать, чтобы проект разводился без фейлов? Просто на Altera/Quartus не помню случая, чтобы приходилось фиксить работут фиттера - он всегда сам справлялся лучше (а попытки лезть к нему напрямую только мешали). P.S. Вдогонку штрих: без констрейна на pblock длительность сборки: синтез: 0:33 P&R: 2:19 и в итоге времянка не сходится. с pblock'ом: синтез: 0:33 P&R: 1:38 и времянка в норме.