Поиск

Показаны результаты для тегов 'ad9122'.

-

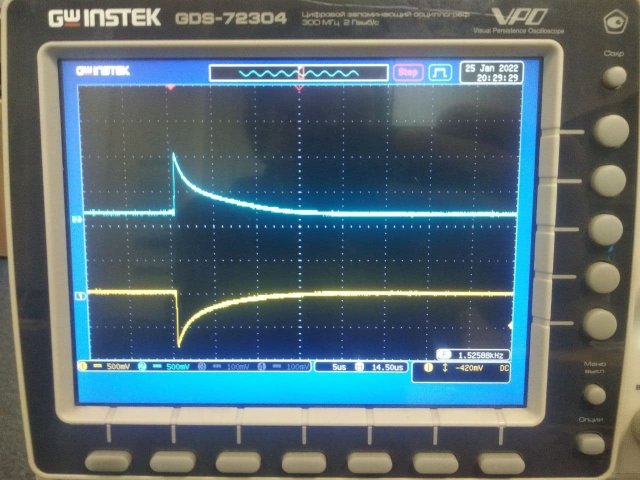

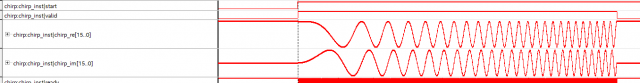

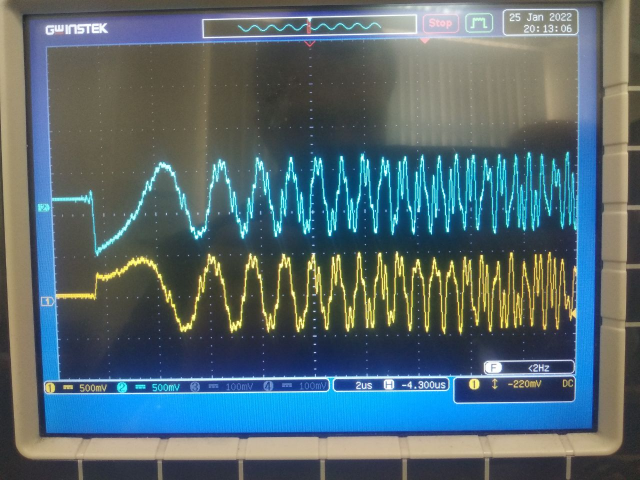

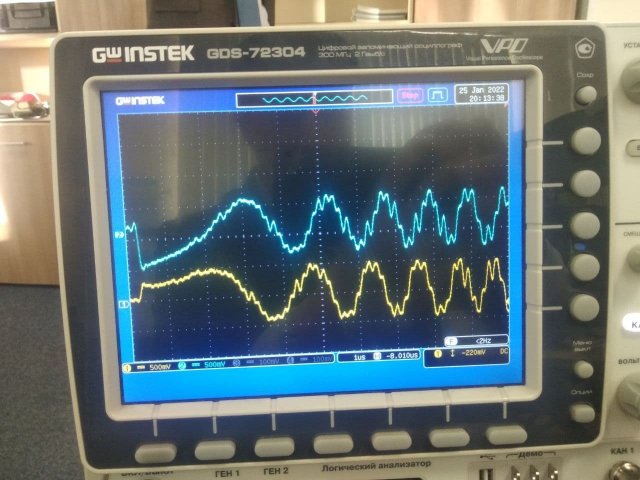

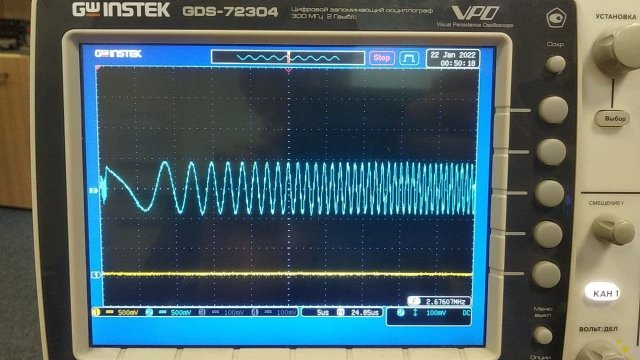

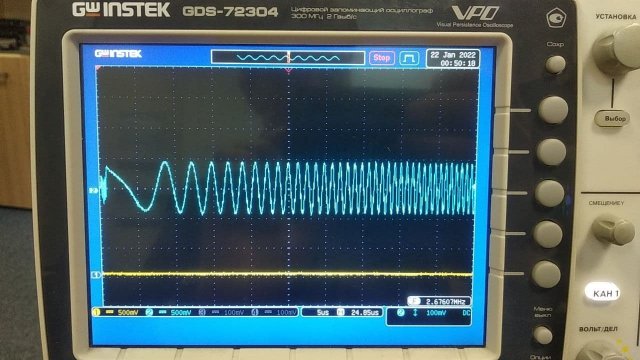

Здравствуйте, уважаемые форумчане необходимо генить синусоиду через ЦАП AD9122 на данный момент написан тестовый модуль, который генерирует ее вот в таком виде: Сделал IP модуль ЦАПа AD9122, который принимает 32х разрядные данные и затем в байтовом режиме выдает данные на ЦАП, причем реализацию сделал 2х модулей : 1. ALTDIO_OUT стоит только на данных, а DCLK и FCLK генятся через логику и выдаются на пинdac_ddr_phy_only_data_ddr.sv 2. ALTDIO_OUT стоит на данных, DCLK и FCLK, все тактируются от одного клокаdac_ddr_phy_all_ddr.sv написал констрейны: #************************************************************** # DAC_DDR #************************************************************** post_message -type info "READ dac_ddr.sdc" set dac_ddr_phy_clk { main_pll_inst|main_pll_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk } set Tco_max 0.65 set Tco_min -0.05 post_message -type info "CLOCK_FREQ_DCLK_HZ = $dac_ddr_phy_clk" post_message -type info "Output Max Delay = $Tco_max" post_message -type info "Output Min Delay = $Tco_min" # Create the external virtual PHY clock create_generated_clock \ -name dac_ddr_dclk \ -source [get_pins "$dac_ddr_phy_clk"] \ [get_ports {DAC_DIC}] #*********************** OUTPUT ************************* set_output_delay -clock [get_clocks {dac_ddr_dclk}] -max $Tco_max [get_ports {DAC_D*}] set_output_delay -clock [get_clocks {dac_ddr_dclk}] -min $Tco_min [get_ports {DAC_D*}] #*********************** GROUP ************************* set_clock_groups -exclusive -group [get_clocks {dac_ddr_dclk}] все пины определены, как LVDS_E_3R в Quartus на Си реализовал HAL уровень dac_ad9122.rar функция инициализации: - spi_dac_ad9122_setup_nav - без фильтров - spi_dac_ad9122_setup - с фильтрами, пример от AnalogDevices проблема в том, что генится с ЦАП вот такой сигнал: При это я использовал код инициализации ЦАП, который рекомендован AnalogDevices с включенными фильтрами, если просто настроить на байтовый режим с выключенными фильтрами, то картинка вот такая: неясно откуда берется эта пила, скорее всего искажение данных, но в каких битах или порядке байтов не могу понять.... При этом в самой схемотехнике перепутаны диaпары данных и FCLK при подключении к ПЛИС, я это решаю для: - 1го варианта модуля инвертированием данных до ALTDDIO_OUT, FCLK просто инвертирую на выходе - 2го варианта модуля инвертированием данных и FCLK до ALTDDIO_OUT пробовал запускать тест, чтобы проверить принимаемые данные ЦАПом 1. если генить DCLK постоянно, а данные и FCLK подставлять, когда данные валидны, то выдаются ошибки постоянно во всех битах 2. если генить DCLK только в сопровождении валидных данных, то ошибок нет, даже когда посылаю 0x0 в ЦАП и в Im и Qre, а в COMPARE REG записаны допустим 0xaa55aa55, если подать верные данные, то таже тема Пробовал кидать одиночные данные и смотреть их прямо на выходе ЦАПа, то видно что выдаются 2а импульса, хотя данные посылаю 1 раз, при этом со времянкой все верно сделано Пробовал выдавать счетчик, который считает от 0 до 0хFFFF, потом сбрасывается и опять считает, на каждый канал Im и Qre, при этом вижу следующее на осциле: Без фильтров: c фильтрами: синий луч Im, желтый луч Qre Не понятно, почему вообще выдает не нарастание линейное, а резкий всплеск по амплитуде и угасание по экспоненте Бьюсь уже 2ю неделю, пока мыслей нет, в каком направлении двигаться Может есть у кого пример реализации.... Буду рад любой помощи, спасибо

.thumb.jpg.d0ede0a2f08d2628b97a8335de59a919.jpg)