Поиск

Показаны результаты для тегов 'матлаб'.

-

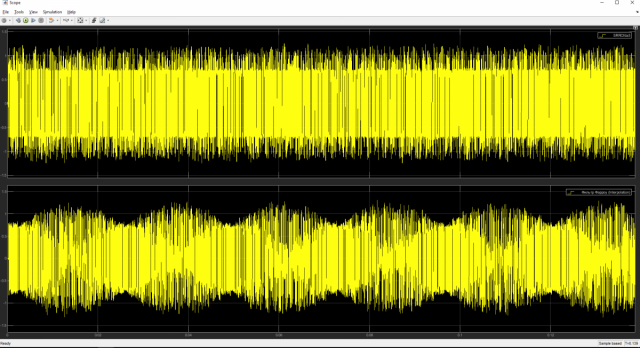

Опишу проблему Как понятно из заголовка пытаюсь сделать символьную синхронизацию для QPSK системы Основываясь на информации из книги "Michael Rice - Digital Communications: A Discrete-Time Approach", символьную синхронизацию делал по принципу: 1) Interpolator - Piecewise структура фильтра Фарроу 2) Timing Error Detector - Детектор Гарднера 3) Loop Filter 4) Interpolation Control - структура "Modulo-1 Counter" В чем проблема ? Проблема в том, что система символьной синхронизации одновременно работает и нет, то есть периодически повторяется следующий процесс: 1) Система находит оптимальный момент выборки (максимального раскрытия глазка) 2) Система теряет оптимальный момент выборки На осциллограмме input и output фильтра Фарроу наблюдается картина как на скриншоте ниже

-

Распознавание нот

Skryppy опубликовал тема в Алгоритмы ЦОС (DSP)

Здравствуйте. Решил научиться программно распознавать ноты на гитарном грифе. Нашел таблицу частот, где по горизонтали - номера ладов, по вертикали- номера струн: Получается, что частота, например, 330 Гц встречается 5 раз на грифе. Каким образом я могу распознать конкретное место на грифе если они звучат одинаково? -

1. Санкт-Петербург (помощь при релокации из других городов); 2. Метро Площадь Мужества; 3. Зарплатная вилка: 100-150 000р. Net. Наш клиент, компания, более 15 лет занимающаяся производством средств и комплексов радиоконтроля, находится в поиске Разработчика систем цифровой обработки сигналов на ПЛИС. Выпускаемая организацией продукция эксплуатируется во всех регионах Российской Федерации и ближнем зарубежье. Предприятие сотрудничает со многими научными и промышленными предприятиями северной столицы. Чем нужно будет заниматься: - Цифровая обработка сигналов на базе ПЛИС (FPGA); - Разработка новых и перенос существующих алгоритмов из Matlab/С/С++ на архитектуру ПЛИС; - Участие в разработке аппаратно-программных комплексов для систем радио мониторинга, радиолокации, имитации сигналов; - Разработка дизайна для ПЛИС Xilinx Kintex 7, Ultrascale, SOC Zynq Ultrascale+ с использованием System Verilog, Verilog и VHDL; - Работа с высокоскоростными микросхемами АЦП и ЦАП, интерфейсами SRIO, PCIe, JESD204, DDR4, Ethernet и др.; - Разработка с использованием современных методологий разработки: трекер задач, билд-сервер, автоматический прогон тестов, гит.; - Написание тестбенчей и документации к своим разработкам; - Развитие и рефакторинг уже написанных модулей. Требования к профессиональным знаниям кандидата: - Опыт разработки под ПЛИС Xilinx в среде Vivado; - Знание языков описания аппаратуры: SystemVerilog, VHDL; - Опыт работы с высокоскоростными АЦП и ЦАП; - Опыт оптимизации по таймингам; - Опыт верификации (псевдослучайные тестовые воздействия, написание эталонных моделей алгоритмов на языке Matlab, симуляция в QuestaSim). Дополнительным плюсом будет: - Знание C/C++, опыт работы в Linux и SOC Zynq, написание скриптов на TCL; - Знание алгоритмов цифровой обработки сигналов (фильтрация (дециматоры, интерполяторы, дробные ресамплеры), бпф, гребёнки фильтров, корреляторы, обнаружители сигналов (CFAR и др), смесители, параллельная обработка сигналов (частота дискретизации выше клока обработки), обработка в плавающей точке и др.). Условия работы: - Оформление по ТК РФ с первого дня работы; - Зарплата "белая" - обсуждается по итогам собеседования; - Комфортный офис недалеко от ст. метро Пл. Мужества; - Возможность гибкого графика (с 9..11 до 18..20); - Поощрения после успешных сдач работ; - 13-я заработная плата по итогам года; - Испытательный срок 1-3 месяца; - Интересные задачи и быстрое внедрение и воплощение Ваших идей; - Дружный и надежный коллектив; - Кандидатам из других городов РФ можем помочь с переездом.