Поиск

Показаны результаты для тегов 'цос'.

-

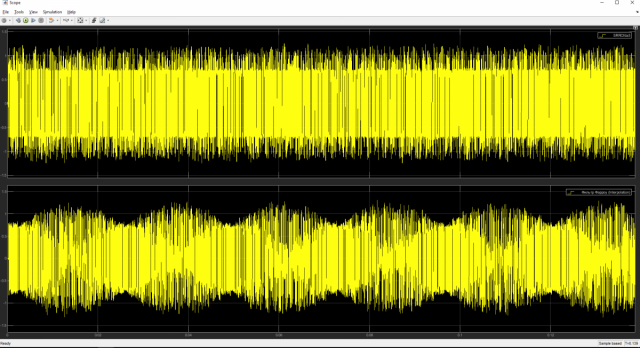

Опишу проблему Как понятно из заголовка пытаюсь сделать символьную синхронизацию для QPSK системы Основываясь на информации из книги "Michael Rice - Digital Communications: A Discrete-Time Approach", символьную синхронизацию делал по принципу: 1) Interpolator - Piecewise структура фильтра Фарроу 2) Timing Error Detector - Детектор Гарднера 3) Loop Filter 4) Interpolation Control - структура "Modulo-1 Counter" В чем проблема ? Проблема в том, что система символьной синхронизации одновременно работает и нет, то есть периодически повторяется следующий процесс: 1) Система находит оптимальный момент выборки (максимального раскрытия глазка) 2) Система теряет оптимальный момент выборки На осциллограмме input и output фильтра Фарроу наблюдается картина как на скриншоте ниже

-

Ищем ведущего специалиста разработки проектов на ПЛИС. Проекты средней и высокой сложности, по обработке сигналов и с поддержкой скоростных интерфейсов. Работа в команде разработчиков. Заработная плата от 90 000 до 180 000 на руки, определяется по результату собеседования с руководителем. Адрес офиса: г. Санкт-Петербург, Пискарёвский проспект, д. 150, к. 5, «Ручьи». Действует развозка от ст.м. Гражданский пр., Площадь Мужества, Комендантский пр., Пр. Просвещения, Ул. Дыбенко. График работы: 5/2, с 9:00 до 18:00 или с 10:00 до 19:00. Формат: полностью офисный (не дистанционка и не гибрид). Официальное оформление, ДМС после испытательного срока. Требования к кандидатам: ▶ высшее техническое образование; ▶ уверенные знания Verilog; ▶ опыт работы с DSP; ▶ инициативность; ▶ умение работать в команде; ▶ навыки организации работ. Навыки работы с ПО: ▶ Xilinx Vivado; ▶ желательно уметь самостоятельно создавать модели по обработке сигналов на С++, Python, Matlab или других языках. О компании: Специальный технологический центр (сайт компании, хабр). Занимаемся разработкой и производством: ⠀ ▶ систем в сфере информационной безопасности ▶ систем сбора и анализа больших данных с применением методов машинного обучения и искусственного интеллекта ▶ телекоммуникационных систем спутниковой связи ▶ беспилотных летательных аппаратов и квадрокоптеров семейства «Орлан», спутниковых комплексов и систем управления ими ▶ телекоммуникационного оборудования, включая комплексы радиомониторинга, различной военной техники наземного, воздушного и морского базирования Контакты для связи: +7 911 700-09-66 (звонки, Telegram) 8 (812) 244-33-13, доб. 2664 [email protected]

-

Есть кадр определённого размера M x N, который сжимается алгоритмом JPEG (YUV 4:2:0). Есть выходной буфер, максимальный размер которого лимитирован (для передачи по эфиру) = V байт. Зная M, N, V, как определить параметр сжатия JPEG (% качества или QP), чтобы выходной сжатый фрейм уместился в буфере? Условие вместиться в буфер - более приоритетное, чем наилучшее качество картинки.

-

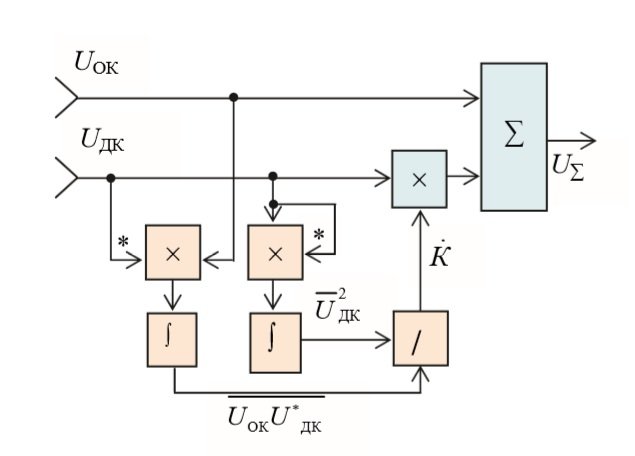

автокомпенсация

eddir опубликовал тема в Алгоритмы ЦОС (DSP)

Доброго времени суток. Реализую алгоритм автокомпенсации по схеме. Но никак не могу понять, что такое интегратор.... прошу помощи. -

Всем привет! Требуется разработчик FPGA со знанием ЦОС в беспилотные автомобили Яндекса. Группа занимается разработкой лидара - https://vc.ru/transport/97355-yandeks-razrabotal-sobstvennye-lidary-dlya-bespilotnyh-avtomobiley Ссылка на вакансию - https://yandex.ru/jobs/vacancies/dev/dev_fpga/ Яндекс хочет сделать перемещение людей более безопасным, доступным и удобным. Мы ставим перед собой масштабную цель: оказаться в числе первых в мире компаний, создавших технологию для беспилотного управления автомобилем. Чтобы воплотить это в жизнь, мы создаем команду увлеченных, умных и целеустремленных профессионалов. Для ускорения процесса обработки информации, поступающей с сенсоров, мы начали использовать FPGA и ищем в нашу команду опытного разработчика. Что нужно делать: строить математические модели обработки потока данных на языке Python; проверять модели и реализовывать их для работы в FPGA на языке SystemVerilog; поддерживать и развивать имеющиеся модули FPGA. Мы ждем, что у вас есть: умение писать под FPGA (Verilog/SystemVerilog); опыт реализации алгоритмов ЦОС (фильтрация, выделение особенностей сигнала, статистика); опыт построения и верификации математических моделей (Python). Будет плюсом: знание С/C++; опыт работы с SOC (Altera/Intel); знание инструментов HLS; опыт работы в Linux. Там есть тестовое - надо его хорошо решить. Это реальная возможность делать продукт в динамично развивающейся отрасли с высокой конкуренцией. С уважением, Иван.

-

Обратная свёртка изображения

shunix опубликовал тема в Математика и Физика

Коллеги, помогите. Предыстория: Возникла необходимость передавать изображения/кадры в сжатом виде, а потом на том конце разворачивать их. На обеих сторонах обработка будет осуществляться с помощью ПЛИС. Я могу получить свёртку изображения через КИХ-фильтр (5х5). Соответственно ядро свёртки у меня есть. Вопрос: Можно ли, и главное как, мне на другом конце по свёртке и ядру получить исходное изображение? Если где-то алгоритм обратной свёртки уже описан, ткните пожалуйста носом в ссылку) PS. Не уверен что угадал с разделом, подходит и сюда и в ЦОС- 13 ответов

-

Программист С++ DSP Санкт-Петербург полная занятость

Варвара опубликовал тема в Предлагаю работу

Наша компания работает над системой передачи данных через КВ радиоканал с минимальной задержкой. Алгоритмы реализованы как на FPGA (первичная обработка) так и на CPU (высокоуровневая часть алгоритма демодуляции). Планируется дальнейший перенос тяжелых алгоритмов на FPGA. Обязанности: - Доработка и улучшение алгоритмов модуляции/демодуляции: синхронизация, эквалайзер, помехоустойчивое кодирование; - Интеграция различных блоков и программных компонентов между собой: радиомодем, программная часть на CPU, GUI, усилители мощности; Требуемые навыки и знания: - С++ 11/14/17 на высоком уровне; - Опыт разработки под Linux; - Опыт работы с сетевыми протоколами (UDP) и бинарными протоколами; - Знание алгоритмов модуляции/демодуляции и цифровой обработки сигналов (DSP); Желательно: - Опыт использования Matlab; - Опыт работы с FPGA Altera, знание Verilog; - Опыт работы с электроникой (как минимум чтение принципиальных схем) и измерительной аппаратурой; - Опыт создания GUI (Java, Web) Мы предлагаем: Панорамный офис с видом на Петербург и Финский залив; Удобные рабочие места, спокойная атмосфера, кондиционеры, кофе, диваны; Бесплатные обеды в офисе; Гибкий график; Заграничные командировки; Инструменты на усмотрение разработчика (любые редакторы/IDE), оборудование и ПО по необходимости; Адекватное и технически грамотное начальство; Неформальное обсуждение задач; Конкурентная заработная плата; Официальное трудоустройство. Ссылка на наш сайт: www.alberblanc.com -

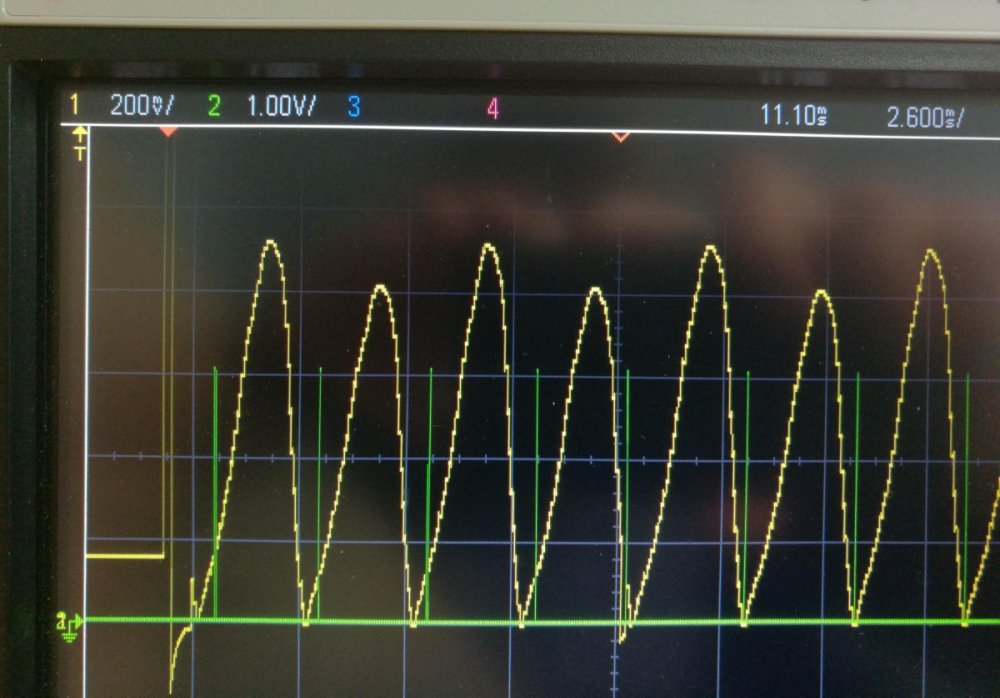

Восстановление синусоидального сигнала после выпрямителя

Mike_sg опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день, товарищи. Подскажите, пожалуйста, есть ли известные алгоритмы для восстановления выпрямленного сигнала обратно в синусоидальный? (скрин во вложении). Сигнал дальше идет на цифровой фильтр для сглаживания, частота стандартная 50 Гц, амплитуда от 20 мВ до 3 В. Буду очень признателен за советы.