AntLip

-

Постов

27 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные AntLip

-

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

Добрый день!

Как и в примере, необходимо настроить синтезатор частоты ( я использую PicoZed FMC Carrier Gen2), но как это сделать я совсем не понимаю, даже не знаю где посмотреть и что почитать. Может кто-нибудь может подсказать дорогу в этом вопросе.

И я дальше разбирался как настроить phy, расковырял lwip до его инициализации. Только заметил, что если есть ядро PCS/PMA то инициализация идет по другой ветке, но все останавливается на phy autonegatination.(Проверял на другой борде) как это правильно необходимо делать.

Спасибо большое за внимание и помощь)))!!!!

-

Доброго дня, Уважаемые форумчане!

Может кто-либо перенаправлял ethernet с eth0(1), в части PS на модуль sfp (xapp 1082) на zynq.

Есть проект, на меди все работает, но очень надо перевести его на оптику. После прочтения документации на ядро (при помощи которого должна и произойти эта магия), а так же вышеупомянутой документации (и только, так как самим проектом еще не разжился) представление весьма смутное. В примере эхо-сервера sfp настраивается с помощью I2C, у меня работать не хочет.

Подскажите, пожалуйста, как этого зверя настроить.

Спасибо большое за внимание и помощь)))!!!!

-

Приведенный выще код для ethernet и есть из примера lwip. Обработку для приема я переписал.

У меня было похожее с UART, но (как ни странно) проблема ушла тогда, когда я поставил объявление прерываний UART между инициализацией прерываний ethernet и их разрешением, дальше разбираться я не стал.

Если ставить в то же место инициализацию для VDMA, прерывания VDMA работают до момента прихода первого сообщения из ethernet, дальше прерывания от VDMA перестают работать, но сообщения от ethernet обрабатываются нормально. Я не до конца понимаю одну вещь, как мне кажется. Перед разрешением прерываний в ethernet, настраивается XScuTimer,а после к нему привязывают XPAR_SCUGIC_SINGLE_DEVICE_ID. И инициализация с помощью XScuGic_DeviceInitialize, а не XScuTimer_LookupConfig -> XScuTimer_CfgInitialize. Может в этом есть нюанс.

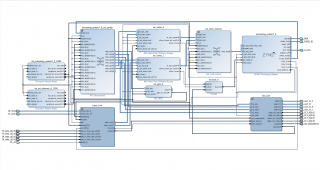

Ниже прикреплен Design

Спасибо за помощь!

-

1. Приоритеты выставить можно, более того, я это делал. все равно при приходе первого сообщения из ethernet работа VDMA прерывается.

2. Да, флаг прерывания я сбрасываю.

Спасибо за ответ.

-

Добрый день!

Делаю проект на Zynq, в проекте есть два VDMA(инициализированы и настроены по примеру в SDK) и ethernet (lwip, echo сервер ).

Проблема заключается в том, что когда настроены и разрешены прерывания VDMA, не работает прием пакетов ethernet ( а очень надо!)) ).

Решение у меня есть, но оно мне не нравиться, так как картинка идет менее качественная (субъективно видео чуть запаздывает). Я отключаю прерывания на VDMA и обрабатываю все в главном цикле. (Мне кажется, что это неправильно)

Подскажите как правильно настроить прерывания в проекте, что бы все работало вместе.

Код настройки прерываний VDMA

int SetupIntrSystem(XAxiVdma *AxiVdmaPtr, u16 WriteIntrId) { int Status; XScuGic *IntcInstancePtr = &Intc; /* Instance of the Interrupt Controller */ XScuGic_Config *IntcConfig; IntcConfig = XScuGic_LookupConfig(INTC_DEVICE_ID); if (NULL == IntcConfig) { return XST_FAILURE; } Status = XScuGic_CfgInitialize(IntcInstancePtr, IntcConfig, IntcConfig->CpuBaseAddress); if (Status != XST_SUCCESS) { return XST_FAILURE; } XScuGic_SetPriorityTriggerType(IntcInstancePtr, WriteIntrId, 0xA0, 0x3); Status = XScuGic_Connect(IntcInstancePtr, WriteIntrId, (Xil_InterruptHandler)XAxiVdma_WriteIntrHandler, AxiVdmaPtr); if (Status != XST_SUCCESS) { return Status; } XScuGic_Enable(IntcInstancePtr, WriteIntrId); Xil_ExceptionInit(); Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_IRQ_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler, IntcInstancePtr); Xil_ExceptionEnable(); XAxiVdma_SetCallBack(&AxiVdma_1, XAXIVDMA_HANDLER_GENERAL, WriteCallBack_1, (void *)&AxiVdma_1, XAXIVDMA_WRITE); XAxiVdma_SetCallBack(&AxiVdma_1, XAXIVDMA_HANDLER_ERROR, WriteErrorCallBack_1, (void *)&AxiVdma_1, XAXIVDMA_WRITE); XAxiVdma_IntrEnable(&AxiVdma_1, XAXIVDMA_IXR_ALL_MASK, XAXIVDMA_WRITE); }Прерывания для ethernet

Xil_ExceptionInit(); XScuGic_DeviceInitialize(INTC_DEVICE_ID); Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_IRQ_INT, (Xil_ExceptionHandler)XScuGic_DeviceInterruptHandler, (void *)INTC_DEVICE_ID); XScuGic_RegisterHandler(INTC_BASE_ADDR, TIMER_IRPT_INTR, (Xil_ExceptionHandler)timer_callback, (void *)&TimerInstance); XScuGic_EnableIntr(INTC_DIST_BASE_ADDR, TIMER_IRPT_INTR); Xil_ExceptionEnableMask(XIL_EXCEPTION_IRQ); XScuTimer_EnableInterrupt(&TimerInstance); XScuTimer_Start(&TimerInstance);

Так же я настаивал прерывания при помощи других функций, по примеру VDMA. Может кто сказать разницу в этих способах настройки прерываний? Как сделать что бы все работало по прерываниям?

Спасибо за внимание!

-

Может кто-нибудь может подсказать как правильно выбрать частоту работы дизайна если известна частота работы камеры?

-

Я нашел ошибку, дело было в неправильных синхросигналах

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

Что-то я не пойму в чем ошибся дальше.

1. На выходе vdma я вижу только 256 пикселей

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA4, 640*16);

в настройках vdma я поменял значение HSIZE( прочитал что может необходимо в битах, хотя есть большие сомнения), после этого стало 256, а ранее на выходе было только 16 пикселей.

Как это исправить, где я накосячил, подскажите пожалуйста?

2. Еще есть вопрос о том, возможно ли передать с помощью vdma по WDATA передать не так как у меня получается (дублируется один и тот же пиксель, видно на изображении, 01000100 ), а так, что бы или бит на транзакцию, а лучше два бита на транзакцию?

3. Про память,я так понимаю, вести речь пока не стоит, ведь там тоже твориться неладное.

Значение HSIZE умножил на 40, тогда получилось что передает все 640 пикселов

-

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

А, до меня, кажется, дошло. Спасибо

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

Посидел я над документацией ядер, над vivado, ila и прочими штуками.

Понял что ничего не понял. Так как информация, данные, через Video In to AXI4-Stream проходят, а сигналы TLAST и TUSER - нет, почему? Не понимаю!

Вот так выглядит времянка на выходе вышеупомянутого ядра ну и design_1_i/axi_vdma_0_M_AXI_S2MM_WDATA[31:0] затесался

Вот так сигналы синхронизации заходят в Video In to AXI4-Stream

Вот так выглядит тестбенч на приблуду, которая иммитирует камеру

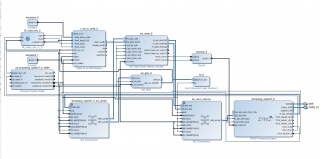

Ну,собственно, проект (сигналы на vblank и hblank поданы тут единожды, в других вариациях они вообще не подключены, разницы я не заметил)

А понять кто виноват и что делать не могу, то ли сигналы неправильно подобраны, то ли чего-то не хватает. Может я смотрю в ila и вижу то, что плохой ученик в книге

Подскажите пожалуйста как это довести до ума!

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

надо вместо XPAR_AXI_VDMA_3_BASEADDR юзать XPAR_AXI_VDMA_0_BASEADDR.прочитайте кусок памяти командой чтения из предыдущего сообщения

Я это сразу поправил, спасибо.

А по сигналам... я сейчас решил посмотреть до конца, как и что формируется Спасибо за информацию.

т.е. после инициализации должна начаться передача данных, правильно я понимаю?

Посмотрел. Не формируются на выходе tlast и tuser нету, а tvalid и tready всегда в единице.

-

Спасибо за ответы.

Я наконец разобрался с ila (по крайней мере, мне удалось увидеть то, что я хотел). Я заметил ошибку и исправил ее, вы были правы, я не выдал там необходимые сигналы.

Теперь информация доходит до vdma. Однако, я хотел бы поинтересоваться

как это проверить, посмотреть данные на выходе S2MM?, дальше смотреть, работает ли сам VDMA, -

Я смотрел это видео, я только не понял как он работал с XMD console, это он симулировал работу SDK? Напрямую писал и читал из памяти?

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

У меня были проблемы на хардварном уровне, на параллельном интерфейсе камеры - сигнал PIXCLK имел резкие фронты, которые порождали высокие гармоники, из-за чего было воспринято большее кол-во фронтов, чем ожидалось. (лечилось индуктивностью на этом сигнале, зарезались высокие гармоники), то есть желательно смотреть осциллографом все сигналы с камеры. Не должно быть сильно заваленных фронтов или сильных колебаний на фронтах.Дальше в Vivado посмотреть с ila сигналы приходящие в само ядро Video In To AXI4-Stream, проверить соответсвуют ли сигналы документам на камеру (длительности, кол-во тактов), желательно проследить несколько раз,в разных местах кадра. Если на этом этапе все хорошо, значит первое звено цепочки можно вычеркивать.

У меня не подключена камера, я имитирую камеру. снизу прикреплю скрин структуры. Возможно , что-то неправильно подключил.

По ila спасибо, буду почитать и пробовать. И еще хотел бы спросить по таймингу, убегают времянки, как с этим бороться, какие причины могут быть?

-

Доброго дня!

Подскажите пожалуйста, правильно ли я понял.

После того как я задал значение VSIZE начинается передача, при условии правильной инициализации и подачи всех сигналов?

И как понять легло ли в память, во вкладке memory я смотрю что лежит по адресам - а там какая-то ерунда.

А вот с ila я пока воюю, не могу нормально наловчиться с ним работать, получается через раз. Может кто-нибудь скинь ссыль, как с ним, ila, работать.

Буду признателен за помощь.

-

2 ilyaprok

Да, все еще актуально. ,

Спасибо большое за информацию!!!

Вашу тему я читал, но как-то там не понял что и как.

Буду пробовать. Еще раз спасибо!

-

Опубликовано · Изменено пользователем AntLip · Пожаловаться

Доброго времени суток, Уважаемые форумчане!

Помогите разобраться с некоторыми вопросами:

1. Нужно ли настраивать (инициализировать) ядро Video In To AXI4-Stream или оно само передает информацию без предварительных настроек.

2. Как лучше (основной критерий простота, наверное) инициализировать VDMA (при помощи описанной Programming Sequence в документации или брать код в examples API-функций)

3. Я пробовал вставить примеры, а именно функцию

int run_triple_frame_buffer(XAxiVdma* InstancePtr, int DeviceId, int hsize,int vsize, int buf_base_addr, int number_frame_count,int enable_frm_cnt_intr);

для инициализации, но данные в память не идут (смотрю по вкладке Memory в режиме Debug)

инициализация по документации

void InitializeVDMA(){ u32 RegVal; //reset AXI DMA RegVal = 0x04; Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x30, RegVal); //wait reset while(RegVal & (1 << 2)) { RegVal = Xil_In32(XPAR_AXI_VDMA_0_BASEADDR + 0x30); } //Инициализируем AXI DMA RegVal = Xil_In32(XPAR_AXI_VDMA_0_BASEADDR + 0x30); RegVal = RegVal | 0x1001; Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x30, RegVal); RegVal = Xil_In32(XPAR_AXI_VDMA_0_BASEADDR + 0x30); xil_printf("AXI DMA control register value: %x\n\r", RegVal); RegVal = Xil_In32(XPAR_AXI_VDMA_0_BASEADDR + 0x34); xil_printf("AXI DMA status register value: %x\n\r", RegVal); //Set start address RegVal = 0x000000; Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xAC, RegVal); //Set Frame Delay ??????? RegVal = 0x0000000; Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA8, RegVal); //Set Horizontal Size 640 RegVal = 0x280; Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA4, RegVal); //Set Vertical Size 480 RegVal = 0x1e0; Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA0, RegVal); }Документацию читал, но пока плохо её понимаю.

Буду рад пояснениям, ссылкам, направлениям на цель

Пример инициализации и работы брал из Adam Taylor's chronicles(part 119)

-

Так в том и дело, что стыдно признаться.

Сидел, ничего не работало. Потом пересмотрел примеры, вставил оттуда куски кода из примеров и заработало.

Что бы толком что-то объяснить или рассказать - нечего.

Еще раз спасибо за помощь!

-

Спасибо всем за помощь! Заработало!)

-

Спасибо за помощь!

Информация пошла, правда нюансы остались))

(к конкретному IP не могу привязать, пакеты идут только при udp_connect(udppcb, IP_ADDR_ANY, tx_port).

Если вместо IP_ADDR_ANY поставить &PCaddr, то картина будет прежней).

Видимо еще какую-то ошибку не могу увидеть.

-

Бродкасты на плату я отправляю, но она не отвечает. Получается что плата не обрабатывает входящие пакеты, вот только как от это решить?

Спасибо за ответы.

-

doom13: Спасибо за советы, сейчас буду пробовать.

PicoZed FMC carrier Card V2 + АЦП через FMC

в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Опубликовано · Пожаловаться

Очень интересен результат, у меня такая же плата и такой же вопрос. Напишите как придёт. Спасибо