-

Постов

215 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные mepavel

-

-

23 hours ago, khach said:

Если вы сейчас перестраивает литографию, то подумайте на счет прямого засвета фоторезиста ( direct laser writing) на базе недавно появившихся ( несколько лет всего) DPSS лазеров 320нм.

В проекте заложен именно такой генератор изображений. Но пока приходится заказывать фотошаблоны на стороне.

-

4 hours ago, semigas said:

Ну не все так просто, к сожалению. Качество ионной имплантации зависит от очень многих факторов и не только от имплантера. Да, сделать можно, нужно и правильно, но не так уж просто и далеко не у всех в России получается.

Понятно, что не так просто. Это целая наука. Нужно точно попасть с профилем и концентрацией, чтобы получить высокое сопротивление при компенсации примесью или дефектами. Так же существуют различные вариации ионов: азот, инертные газы, хром, железо и т.д. У всех свои преимущества и недостатки. С процессом активации есть нюансы.

4 hours ago, semigas said:По поводу кремниевой технологи для затворов на нитриде: это действительно можно сделать (показано на практике, но не российскими предприятиями), но литография просто так не переносится. И дело не в том что там Si3N4, SiO2 или Al2O3.

В России (союзе) с давних пор A3B5 занимаются несколько предприятий. Поэтому там с самого начала затворы делали при помощи электронной литографии. Фотолитография ещё не была тогда сильно развита в субмикронных размерах.

4 hours ago, semigas said:Ну и самый большой вопрос: люди из GaN в России не обладают мощностями кремниевых заводов, а просто придти в Микрон и сделать литографию отдав ФШ не получится, надо отрабатывать процесс. У кого-то есть такая возможность, а у кого-то нет, зависит от предприятия.

Тут больше зависит от желания и денег. Так то Микрон идёт на сотрудничество, но не всегда получается сделать работы по первому требованию. Поэтому мы и строим новый цех с более ли менее актуальной фотолитографией. Сейчас наша старая "проекционка" в типовом режиме позволяет работать по нормам 2 мкм. Иногда ужимаемся до 1,4 мкм, но со всякими ухищрениями.

-

3 hours ago, khach said:

Вы не путайте литорафию по кремнию по собственнному оксиду с литографией по толстому слою Si4N4 или другого диэлектрика на нитриде. Это как говорится две большие разницы.

Зы. Еще забыли упомянуть установку ионной имплантации, чтобы убить 2DEG электронный газ вокруг активной области транзистора. А то травлением слишком поверхность портится и утечки большие.

Еще очень отдельная тема- вопрос металлических контактов к стоку и истоку

Вообще там первый слой нитрида (Si3N4) достаточно тонкий. Никакой там разницы нет. Si3N4 - используется в кремниевой технологии испокон веков. Ионную имплантацию используют для изоляции элементов. Всё стандартно. Надо пролегировать AlGaN n-типа вокруг активной области.

-

14 minutes ago, Maksimka said:

Вам фотошаблон с такой точностью и необходимой дефектностью никто не сделает, плюс сама по себе обычная установка ФЛ будет давать ошибку совмещения такую, что дай бог парочка транзисторов с пластины будет нормально работать.

Тут реально такое ощущение, что одни технологи собрались.

Хм... а как мы даже на наших кремниевых транзисторах делаем затворы 0,3-0,4 мкм на ПАО "Микрон" (длина пальца весьма приличная)? Причём с хорошим качеством. Процент выхода очень высокий даже на большие кристаллы с мощностью 200-300 Вт (периметр 200-300 мм). Сейчас на ПАО "Микрон" уже технологические нормы 65 нм освоили. Вы думаете там электронная литография? У нас тоже готовится новый цех, на котором будет техпроцесс, позволяющий делать затворы 0,25 мкм без электронной литографии.

Ну то что ФШ никто не сделает - это уже совсем интересные утверждения.

14 minutes ago, Maksimka said:Многие думают, что вот они взяли правильную ГС, сделали правильный Т-затвор, транзистор готов. Ребят, так это не работает. У вас будут утечки, плохой Шоттки, низкие пробивные, большие лаги, маленькая крутизна, маленький ток, очень быстрая деградация, малая плотность мощности. И с этим всем вы будете бороться, даже имея в наличии самое крутое оборудование. А когда вы будете думать, что вы что-то побороли, вас ударит по голове при выпуске следующей пластины. А когда решите менять проектную норму, все пойдет по новому кругу.

Ещё забыли про коллапс тока стока.

-

8 hours ago, khach said:

Не рублей, евро лимонов как минимум . Угу, 0.25 затвор на старой литографии, верю. Т.е про T-shape затворы слышать не приходилось? А без них 10 ГГц транзисторы как то не получаются. Вы же не УКВ транзистор изобретете с Ft в районе единиц ГГц? А если нет, то прийдется делать такую структуру как на фото, и ножку буквы Т надо электронолитографией резать, т.к с оптикой даже deep-UV она как то не получается ровной по всей длине. А это значит что транзистор закрываться не будет.

Не понимаю, причём здесь стандартный T-затвор с GFP (Gate Field Plate). Минимальный размер - это как раз ножка "T", т.е. в первом слое нитрида кремния формируется окно с шириной 0,15 - 0,5 мкм. В 2002-2003 году во всю массово делали кремниевые микросхемы по нормам 130 нм. Старые установки фотолитографии позволяют без проблем сделать это окно, так что нет необходимости прибегать к электронной литографии в серийном производстве, хотя можно. Откуда такие данные, что на UV не получается ровным по всей длине окно (это уже в вопрос к качеству ФШ и оборудованию)? Естественно, что ничего идеального не бывает, но это не мешает нормальной работе транзистора. Смысла никакого нет получать окно с отклонением ширины в единицы нанометров.

1 hour ago, K0nstantin said:Где-то кому-то что-то обрежут, или образно станет Суэцкий канал - пойдёт задержка в цепочке. Здесь скорее вопрос в степени "своего", степени независимости от остальных. Да, где от своего только корпус, а иногда и вовсе наклейка - это печаль (

Если так рассуждать, то и оборудование, и материалы должны быть отечественными. Кто этим всем будет заниматься? У нас полно специалистов по разработке оборудования для полупроводникового производства нужной квалификации? Мы в этом безнадёжно отстали. Максимум, что можно сделать - это купить готовую устаревшую технологическую линию. Надо быть реалистами, а не думать, что просто так из воздуха на коленке что-то возникнет своё.

1 hour ago, semigas said:Неужели параметры кристалла Светланы-Рост, пдф которого приведён выше, не сравним (сравнимы, а не в точности равны) с допустим 6П9145Б2 с вашего сайта?

Параметры 6П9145Б2 занижены относительно его реальных характеристик (таковы были требования ТЗ). Так что, если в этом изделии применить кристалл Светланы-Рост, то в принципе транзистор будет удовлетворять нормам ТУ.

Другое дело, что если рассматривать транзисторы 6П9140А, 6П9141А1, 6П9141Б1, 6П9142А2, 6П9143А3, 6П9143Б2, 6П9144А4, 6П9144Б4, 6П9146А1, тот тут уже пока никак, к сожалению, не получится применять отечественные кристаллы.

1 hour ago, semigas said:С таким подходом прогресса не будет никогда: ваши клиенты с вас требуют недостижимых параметров, вы с производителей кристаллов требуете параметров, которые без финансовых вливаний (как вы сами сказали выше) невозможны, в итоге прогресса нет.

Да, в итоге получается замкнутый круг. А всё из-за того, что у нас руководители, министры некомпетентны, и думают (или по крайней мере показывают всем своим видом) что на коленке и без знаний (образования) что-то можно сделать. Сейчас эпоха эффективных менеджеров, которые в технике и физике ни-ни. Мало кого волнует кризис в электронной и других промышленностях. Президент чётко сказал, что денег нет! Держитесь как хотите за счёт продажи гражданской продукции. Например, предложил из ТУ-160 сделать бизнес-джет.

1 hour ago, semigas said:Почему столько обсуждений литографии? Тут все технологи что ли? На UHV затворы на нитридах тоже нормально получаются, но это совсем другая история. Про обычную контактную литографию для затвора 0.25 точно можно забыть, если нужен стабильный техпроцесс.

Да, одни технологи тут собрались) Контактную литографию даже на 2 мкм не используем. Только для керамических плат. Что уж об этом говорить.

-

2 hours ago, oleg_uzh said:

100% процентов чего вы хотите иметь? У вас с математикой проблемы или с пониманием, что такое 100% локализация производства? Вы готовы вложиться в отечественную химоту и оборудование? На весь мир один, два производителя с мировым именем. А это даже не млрды рублей, это триллионы... За чей счет будет банкет? 100% никогда не будет и не надо устраивать Потемкинские деревни.

Да это не ко мне вопросы, автор темы спрашивал про то, как создать GaN HEMT с нуля. А так с Вами полностью согласен)

-

5 hours ago, khach said:

Вот тут вы меня разочаровали. За это время можно было и свой собственный слепить. Говорю это вполне ответственно, потому что видел пример как гораздо меньшая страна чем Россия просто из чувства "что смогем" такой транзистор слепила практически с нуля. Без всякой связи с Cree. По повду техпроцесса- не путайте мягкое с теплым. Почти вся фотолиторафия кроме затворов воплне исполняется по техпроцессу 1-2 мкм. Обычными масками или вообще direct laser writing по фоторезисту. Только сами затворы надо делать электронолитографией с нанометровым разрешением. Будете смеяться- для этого использовался древний электронный микроскоп слегка модернизированный "на коленке".

Мне вот интересно, откуда у Вас такая уверенность, что на коленке можно слепить годный GaN транзистор с высокой подвижностью электронов? Максимум, что Вы на коленке слепите - это кривой диод Шоттки с миллиметровыми размерами. Таких и у нас в России полно из чувства, "что смогём". Я техпроцесс Вам привёл в пример, чтобы наконец спустились с небес на землю, а не писали тут, что за 20 млн. руб. с "нуля" можно слепить высокотехнологичное изделие. За эти деньги Вы купите средненький VNA с зондовой и не более того. Но Вы продолжаете писать про электронную литографию и пресловутый лазер (не даёт он Вам покоя). 0,25 мкм затвор вообще делается на устаревшей более чем на 20 лет обычной установке фотолитографии. Никто в серийном производстве не будет использовать электронную литографию для обсуждаемых GaN HEMT с затвором 0,15 - 0,5 мкм. Да и дело то не только в стоимости установки фотолитографии и генератора изображений. Вся технологическая линейка стоит огромные деньги, размер которых обычному человеку даже сложно представить.

-

5 hours ago, semigas said:

Но мы же и не про кремний сейчас. Ведь oleg_uzh привел мануал транзистора на GaN с конкурентноспособными параметрами? А транзисторы с такими параметрами у Светланы-Рост есть в достаточном колличестве, я думаю)

Кратко, параметры к сожалению пока не очень-то конкурентоспособные. Но не всё так плохо. Я уже около 5-ти лет занимаюсь исследованием GaN-транзисторов, изготовленных Светлана-Рост. Также активно общаюсь с разработчиками и был у них один раз. Первые образцы были совсем плохи. Транзистор через некоторое время просто самопроизвольно открывался и сгорал, не было пробивных напряжений, частотные свойства были хуже кремниевых транзисторов. Но образцы, которые были полученные в прошлом году, действительно прорыв. Они имеют стабильные параметры и, возможно, даже относительно неплохой процент выхода годных. Но по факту есть ещё некоторые проблемы, которые надо решить.

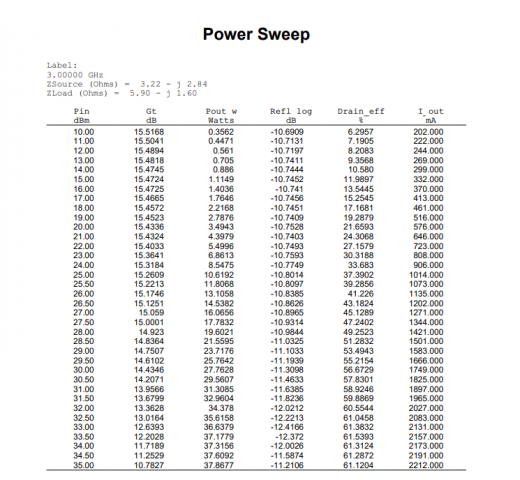

Что касается конкурентоспособности. У меня были образцы с длиной затвора 0,5 мкм и в сравнении с нашими транзисторами (по технологии 0,25 мкм) наблюдался существенный завал КПД и выходной мощности на вдвое меньших частотах. Усиление, естественно, тоже ниже на 4-6 дБ (большая разница в удельной крутизне). Результаты измерений межэлектродных емкостей и вольтамперных характеристик объяснили в чём отставание.

Уже сейчас можно сделать вывод, что по факту у нас есть фабрика, которая позволяет изготавливать неплохие отечественные GaN-транзисторы, но насколько с "нуля" - этого я точно не знаю. Возможно, если Светлана-Рост уйдёт на техпроцесс 0,25 мкм и исправит некоторые проблемы, то мы получим уже что-то на хорошем уровне. Но я уверен, что для этого нужно вкладывать соответствующие средства. Просто так ничего с места не сдвинется.

Вообще кроме Светлана-Рост, есть ещё несколько отечественных контор, которые занимаются изготовлением GaN-кристаллов. Но там пока параметры оставляют желать лучшего.

-

1 hour ago, khach said:

В смысле? Первые уже давно есть. Вот из последнего за 2020 года номера электроники свч.

Pages from Elektronika_Svch_2020_4(1).pdf 333.77 kB · 8 downloads

даже индексы для материала П или 6 давно ввели. 6П9140А или ПП9136А как пример.

Ссылку привели на статью, в которой я соавтор

Я же говорю, что автор темы хочет создать первый на 100 % локализованный транзистор, который на уровне или лучше зарубежных аналогов.

34 minutes ago, oleg_uzh said:

Я же говорю, что автор темы хочет создать первый на 100 % локализованный транзистор, который на уровне или лучше зарубежных аналогов.

34 minutes ago, oleg_uzh said:Вот зачем опять вводить аудиторию в заблуждение, что это отечественный? Кристалл внутри чей стоит? А? Назовите правильно - отверточное производство! Перекроют кислород зарубежные партнеры и поедут все так называемые разработчики отечественного дружно в Магадан.

Бесит эта уже ситуация с псевдоотечественностью. Из-за таких работ в Минпромторге и думают, что все в стране прекрасно и все есть. Ничего развивать не надо. И по итогу все сидят в глубокой ...опе.

Бесит эта уже ситуация с псевдоотечественностью. Из-за таких работ в Минпромторге и думают, что все в стране прекрасно и все есть. Ничего развивать не надо. И по итогу все сидят в глубокой ...опе.

В Минпромторге все знают, что GaN-кристаллы изготовлены по Foundry. По поводу производства. Даже на кремнии у нас нет техпроцесса хотя бы 22 нм, а сейчас требуется элементная база с характеристиками, которые невозможно изготовить по техпроцессу 90 или 130 нм (65 нм только в перспективе).

-

2 hours ago, khach said:

Cree и wolfspeed все таки на одном предприятии делают. Но подложки покупные или с другого производства.

Так Wolfspeed - это подразделение Cree, которое занимается радиочастотной и силовой электроникой (название появилось в 2016 году). Это и есть одно предприятие) Cree - первая в мире сделала монокристаллические подложки SiC хорошего качества и большого размера. И долгое время оставалась монополистом. Кроме того, у Cree своя фабрика полного цикла (включая ростовые операции) и до последнего времени они предоставляли Foundry-услуги.

2 hours ago, khach said:третий- палит лазером виасы в подложке для закорачивания истока,

Лазером палить BackSideVia на GaN не очень хорошо.

2 hours ago, khach said:В принципе " на коленке" сделать можно, но миллионов 20 как минимум желательно иметь на старт. Большие расходы на всякую дополнительную мелочевку- деионизированная вода, прекурсоры типа триметлигалия если растить струкутры CVD или особочистого галлия если MBE. Газырасходники для плазменного травления, полный цикл литографий, обычнй и электронной. Пробстейшн для СВЧ тестов.

20 миллионов чего?) На мелочёвку я бы сказал не большие расходы, а дополнительные. На коленке можно сделать что-то вроде первого сплавного транзистора, а годное изделие не получится. Если стоит задача завладеть обманным путём бюджетными деньгами и в научно-техническом отчёте написать, что был создан первый 100 % отечественный GaN транзистор с характеристиками на уровне лучших зарубежных аналогов за 20 млн. руб. вложений с нуля, то это всё на свой страх и риск.

P.S. Почему то у инженеров-радиоэлектронщиков, которые слабо ориентурются в микроэлектронике, существует байка, что у нас можно создать любой чип, транзистор или микросхему, но только в штучном количестве.)

1 hour ago, khach said:Ни коим образом- проверено на практике. приходилось полность переучивать, иногда с большим трудом чем обучение человека с нуля. Иначе росла такая фигня.....

Так если полностью переучивать, значит есть кому учить? Откуда возьмёте этих самых "учителей"? Максимум научат кнопки нажимать, а для этого и высшего образования не надо. Сомневаюсь, что кто-то будет учить физике твёрдого тела, квантовой механике, кристаллохимии, физико-технологическому моделированию и т.д.. При малейшей проблеме будете каждый раз вызывать зарубежных специалистов за калибровкой и отладкой техпроцесса.

-

7 hours ago, oleg-n said:

Товарищи, поделитесь пожалуйста информацией о разработке и производстве GAN транзисторов с нуля.

С нуля? Начнём с подложки. Для СВЧ GaN в идеале нужен качественный карбид кремния (SiC) нужного политипа и нужной ориентации, и, главное, с малым количеством дефектов.

В мире фирм, которые производят такие подложки, вроде около 3-х. Стоимость таких подложек даже сейчас десятки-сотни $ за штуку (диаметр 100 мм, может сейчас уже 150 мм научились).

Есть альтернатива - обычный кремний, но высокую плотность мощности на нём не получишь из-за плохой теплопроводности. А проблема перегрева на GaN - одна из самых острых.

Далее требуется на этой подложке вырастить сложную эпитаксиальную структуру с очень тонкими слоями (единицы, десятки нм).

Ну а дальше, как уже правильно сказали, идут постростовые операции.

7 hours ago, oleg-n said:Какое финансовое вложение ?

Только для постростовых операций требуются минимальные вложения 5 - 10 млн. $. И это при наличии оборудования для кремниевого кристального производства, стоимость которого, в несколько раз превышает указанную сумму.

Тут вообще вопрос в том насколько нужно локализовать процесс.

7 hours ago, oleg-n said:В какой сфере деятельности искать специалистов и с каким опытом ?

Какие нюансы ?

Специалистов в сфере технологии микроэлектроники, желательно имеющих опыт работы с A3B5. Нюансов множество, если не покупать готовый импортный техпроцесс, который должны отладить зарубежные специалисты на Вашей технологической линии.

7 hours ago, oleg-n said:Существуют ли отечественные производители ?

Риски?

Существует и их количество в последнее время стремительно растёт. В основном все покупают готовые зарубежные эпитаксиальные структуры и пробуют проводить на них постростовые операции.

А вот теперь о рисках. Отечественные специалисты с большим опытом работы в сфере микроэлектроники на A3B5 даже на постростовых операциях не могут до сих пор получить конкурентно способный продукт. Хотя уже имеются дизайн-киты на отлаженный техпроцесс. Т.е. изделия получаются с характеристиками лабораторных образцов 15-ти летней давности. Так что это Вам не отвёрточное производство организовать.

Учтите ещё, что технические требования к отечественной элементной базе пишут совершенно некомпетентные инженеры-конструкторы РЭА. Они хотят GaN транзистор с характеристиками лучших зарубежных образцов ЛБВ. Причём этот транзистор должен работать на бешенных частотах и температуре корпуса +100 °С, а лучше 125 °С и иметь при этом КПД до 70% с усилением 30-40 дБ в непрерывном режиме. Когда их просишь показать даже лучшие зарубежные транзисторы или МИС СВЧ с такими характеристиками (даже при температуре корпуса +25 °С), они говорят - мол на то вы и разработчики, чтобы создать такое.

-

17 hours ago, Turgenev said:

Но 39дБм на входе будет кратковременно, микросекунды или даже наносекунды.

Чтобы пробить затвор микросекунд предостаточно. Это же не резистор какой-нибудь.

Можно, конечно, попробовать ступенчато поднимать уровень входной мощности и измерять ток утечки затвора. Когда затвор пробьется, получим искомую величину мощности.

А дальше уже считать запасы по мощности. Но это всё очень грубо и слабо учитывает деградацию при наработке.

-

4 hours ago, Turgenev said:

Прочитал этот абзац на картинке. Так понял, что вы хотите до меня донести, что при создании лоад пула производитель пытался выжать максимум из транзистора и не факт что выжал, будучи ограниченным в настройке тюнеров или просто не настроив тюнеры идеально под транзистор, а просто выжав сколько надо.

Если производитель не выжал максимум (оптимум) из транзистора при проведении Load Pull будучи ограниченным в настройке тюнера нагрузки (Load Tuner), то такой Load Pull признаётся не состоявшимся. В этом случае подбирается более подходящая оснастка, позволяющая расширить возможности тюнера. С тюнером источника (Source Tuner) такое тоже может быть, но это уже не состоявшийся Source Pull, который никак не влияет на режим работы транзистора. Например, если источника мощности хватает с достаточным запасом, то тюнер источника вообще не используют.

4 hours ago, Turgenev said:Если так, то из этого следует, что можно взять S-параметры транзистора, измеренные при максимальном токе стока и подобрать в CST импедансы входа и выхода таким образом, чтобы S11 было минимально, а S21- максимально. Я понимаю, не обязаны получившиеся импедансы совпасть с теми, что в лоад пуле, хотя бы потому что ток стока в лоад пуле меняется, но должны быть близкими по значению.

Опираться на импеданс выхода по малосигнальным S-параметрам для мощных транзисторов, работающих в нелинейном режиме, категорически неправильно! Я же Вам сразу написал, что это Ваша главная ошибка. Так делают только для линейных устройств. Если бы так можно было, то смысла в проведении дорогостоящего Load Pull не было бы. А вот входной импеданс можете определить и он будет удовлетворительно совпадать с импедансом на большом сигнале. Здесь смысл есть, т.к. тюнер источника на больших КСВ ограничен. И ещё, надо понимать, что входной импеданс нелинеен, т.е. зависит от уровня мощности и активная составляющая может легко меняться в 2-3 раза (особенно резкие изменения происходят в режиме насыщения).

Так что подключаете к S-параметрам оптимальный импеданс нагрузки и измеряете входной.

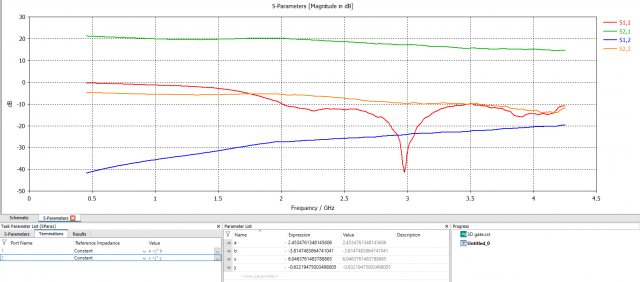

4 hours ago, Turgenev said:У меня на 3 ГГц Zin=4.77-j*1.65 для ПП9138Б при токе стока 750 мА, напряжении сток-исток 28 В. При этом импеданс нагрузки взят из Load Pull данных и равен ZL=5.9 - j*1.6.

-

8 hours ago, Freesom said:

При большом сигнале тюнеры обеспечивают оптимальные характеристики мощности и кпд транзистора, а не выполняют согласование сопряжением по импедансу.

Это Вы говорите про случай, когда имеется только тюнер нагрузки. Обычным делом и необходимостью является наличие тюнера источника. В этом случае тюнер источника выполняет (может выполнить) согласование с сопряжением ко входному импедансу.

Другое дело, что возможности согласования тюнеров не безграничны, поэтому не всегда удаётся получить идеальное согласование. Особенно когда большие КСВ или активная часть входного импеданса отрицательная. Для этого используется Source и Load Pull с векторными приёмниками, который позволяет "видеть" входной импеданс. Для LDMOS транзисторов значения входного импеданса на малом и большом сигнале неплохо совпадают. У GaN HEMT, работающего в стабильном режиме, аналогичная ситуация вплоть до компрессии коэффициента усиления в 1-2 дБ. Так что использование малосигнальных S-параметров для уточнения входного импеданса в большинстве случаев целесообразно. В идеале лучше использовать данные Source и Load Pull с векторными приёмниками.

-

4 hours ago, Turgenev said:

Согласовывал по своему, все сошлось, но только если сопротивление порта в CST ставить 25+j*25, а не указанное вами. Я не прав. Нашел статью почему я так думал, 2й пример там один в один как у меня:

Странно, эту статью много где советуют

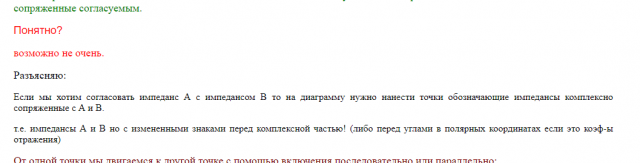

Нагрузка с источником согласованы, когда их импедансы комплексно сопряжены. Рядом с диаграммой Смитта нарисована схема, в которой нагрузке ZL в явном виде задан импеданс источника транзистора из Load Pull данных на транзистор. А это противоречит законам физики, т.к. в общем случае при согласовании импедансы нагрузки и источника комплексно сопряжены, а в Вашем случае получилось, что эти импедансы равны. Поэтому либо поясняющая схема нарисована некорректно, либо ошибочные данные введены в эту программу.

-

5 hours ago, Turgenev said:

Вспомнил свои рассуждения. Таблица лоад пула с указанием импеданса источника:

Если импеданс источника подключаемого к затвору равен 3.22-j*2.84, то импеданс затвора ему комплексно сопряжен и равен 3.22+j*2.84. При согласовании на диаграмме Смита мы указываем импеданс комплексно сопряженный импедансу нагрузки, т.е. импедансу затвора, а значит нанести надо было именно 3.22-j*2.84. Что и сделано на скрине, еще раз продублирую его, чтобы далеко не ходить:

Так программа же работает явно по другому и даже поясняющая схема согласования приведена. Там где нарисовано сопротивление ZL должно быть введено значение входного импеданса 3.22+j*2.84. В точке TP4 измеряется импеданс со стороны 50-омного тракта. При идеальном согласовании должно быть 50 Ом, что мы и видим. У Вас же всё наоборот: нагрузкой согласующей цепи является ей же приводимый импеданс.

Попробуйте поэкспериментировать с нагрузкой по проще, например 25 - j*25. Сравните результаты моделирования с расчётами этой программы. При длинах микрополоска, заметно превышающих его ширину, и при отсутствии резких переходов по ширине результат аналитического расчёта должен близко совпадать с ЕМ-моделированием.

-

On 1/5/2021 at 2:47 AM, Turgenev said:

Из прочитанного (в том числе все рекомендации из этой темы) за все это время наметил и начал реализовывать следующий порядок действий, чтобы разобраться где ошибка (пока пробую на затворе, транзистор под руками только ПП9138Б, с Zsourse на 3ГГц из таблицы лоад пулов 3.22-j*2.84):

1) Создание прототипа схемы согласования по диаграмме Смита, с добротностью в пределах 2; Если интересно, то под катом то, что получилось.

2) Перенос в CST схематик полученных полосков по диаграммам Смита и подгон оптимизатором;

3) Перенос из схематика в MWS CST и подгон оптимизатором. Сейчас понимаю что 2й пункт можно было пропустить.

4) Изготовление получившейся цепи и снятие S-параметров.

5) Моделирование в CST снятых параметров на нужный мне импеданс (3.22+j*2.84 с одной стороны и 50 ом с другой)

На приведённой диаграмме Смитта, вероятно, ошибочно согласование выполняется на нагрузку 3.22-j*2.84, а не 3.22+j*2.84.

-

4 hours ago, Freesom said:

хотя подсказывали во всех темах, где он спрашивал, как умели.

Посмотрел, единственным дельным советом было предложение почитать литературу на эту тему. Хотя это больше не совет, а издевка.

4 hours ago, Freesom said:Как правило при аккуратном проектировании и изготовлении характеристики сходятся. Для того симуляторами и пользуемся. Если не сходятся - что-то не учтено. Выясняли что именно.

Ещё раз повторюсь, что Вы понимаете под критерием схождения характеристик (без субъективизма и философии)? Объективно измеренные и смоделированные характеристики никогда не могут сходиться. Расхождение всегда будет из-за неточной модели, приближённого решения, погрешности измерительного оборудования и измерительной оснастки и т.д. На курсе метрологии для студентов начинают с темы "Истинное, действительное и измеренное значение физической величины".

Я Вам уже приводил пример. Один случай, когда Вы смоделировали и измерили 50-омный микрополосок. А другое дело, когда аналогичные действия провели не с примитивной моделью, а с многозвенной согласующей цепью, которая даже при моделировании "играет параметрами" при небольшом изменении плотности сетки и точности солвера. Вы же пытаетесь мне доказать, что измерив S-параметры макета усилителя, состоящего далеко не из примитивов (согласующие цепи, цепи смещения, SMD), можно судить о неточности модели транзистора. Это всё равно что линейкой поверять микрометр.

Чтобы понять, насколько точная модель усилителя, достаточно было измерить его S-параметры на ХХ и КЗ (вместо транзистора). В идеале впрямую измерить S-параметры входной и входной цепи.

4 hours ago, Freesom said:В предложенной модели после согласующего пада на краю платы стоит отрезок линии шириной 1.2мм и длиной 0.45мм (Lpad_PP9138). Вот мне и стало интересно, это производитель учёл так зазор между платой и корпусом и посадил референсную плоскость на расстоянии 0.45мм от корпуса или нет.

Ранее написал, что референсная плоскость на расстоянии 0,04 (typ) 0,08 (max) мм от тела корпуса транзистора. Все технологические зазоры на усмотрение потребителя и к модели S-параметров не имеют отношения.

4 hours ago, Freesom said:Но даже если нет, то в модели этот момент нарисован, в реальности он есть, а результаты не совпадают. Говорите, это потому что транзистор был померян в 50-омной оснастке при Uds=28V и Id=500mA и практической ценности эти данные не имеют?

Я такого не говорил) S-параметры измерены максимально точно и для данного типа транзистора использовалась прецизионная 50-омная оснастка MT-964C (ф. Maury Microwave), калиброванная по методу TRL. Практическая ценность малосигнальных S-параметров очень велика. Об этом я написал в первом своём посте в этой теме.

P.S. У меня такое ощущение, что Вы внимательно не смотрели на единственную в этой теме картинку с неполными S-параметрами в начале темы. Там много интересного можно увидеть, чтобы быстро найти виновника.

-

On 12/14/2020 at 2:08 AM, Freesom said:

Так человек, создавший тему, изначально так и сделал. И даже модель приложил. А в результате получил то, что получил. Отличия очень большие. В реальности есть ещё взаимодействие края пада с керамическим корпусом транзистора, которое в модели никак не отражается - вместо транзистора воздух.

У меня нет CST, но думаю, что топикстартер смоделировал всё верно, правда совсем не то, что нужно. В папке "Pout vs Pin" написано

3.00000 GHz

ZSource (Ohms) = 4.08 - j 3.82

ZLoad (Ohms) = 11.01 - j 0.20Аналогично для частот 1, 2 и 4 ГГц. С помощью интерполяции можно получить значения оптимальных импедансов в диапазоне частот 1 - 4 ГГц. Благо в каждом симуляторе есть интерполяция в различных вариациях.

Таким образом, с помощью этой информации можно было спроектировать входную и выходную согласующую цепь. Жалко, что никто в этой теме этого не подсказал. Для чего нужны малосигнальные S-параметры я написал в предыдущем посте.

P.S. Вместо этого тут сличали S-параметры одного экземпляра транзистора с целым макетом усилителя мощности, изготовленным методом handmade. А потом как обычно делаются выводы, что либо S-параметры транзистора сняты неверно, либо плохие модели чип-конденсаторов, либо разъёмы неправильно припаяны, да и вообще роджерс - китайская подделка.

Между тем, при неправильном выходном согласовании рискуем получить вообще отрицательную активную часть входного импеданса Re|Zin|<0 => |Гin|>1. В этом случае получим резонансный пик(и), который будет меняться даже при малейшем поднесении руки к макету на расстоянии. Так что говорить о погрешностях в моделировании или измерении я бы не стал. Для начала надо устранить основные недочёты.

On 12/14/2020 at 2:08 AM, Freesom said:В реальности есть ещё взаимодействие края пада с керамическим корпусом транзистора, которое в модели никак не отражается - вместо транзистора воздух.

Такие нюансы надо учитывать при работе с высокими импедансами. В данном случае импедансы низкие, поэтому этим влиянием можно пренебречь. При низких импедансах преобладающую роль играет зазор между платой и корпусом транзистора. Получается, что вносится паразитная последовательная индуктивность (в общем случае отрезок передающей линии с повышенным волновым сопротивлением).

On 12/14/2020 at 2:08 AM, Freesom said:Я так понял, вы киваете в сторону моделирования, т.к. в измерениях производителя/пользователя сомнений нет,

С использованием данной информации о транзисторе были разработаны несколько усилителей мощности. Никаких проблем не возникало. Всё успешно работало без дополнительной подстройки.

On 12/14/2020 at 2:08 AM, Freesom said:в допустимости дээмбеддинга/вставления файла характеристик транзистора в плату с любым импедансом согласователей тоже сомнений не возникло?

Вы слишком идеализируете "любой импеданс". Допустим 50 Ом и в симуляторе, и в реальности воспроизвести не так сложно. А вот импеданс, скажем 1+j300 в реальности и симуляторе интересная задачка.

Ещё более интересная задача, какой критерий выбрать для сравнения? Отношения длины вектора ошибки к длине заданного вектора? Где хорошая сходимость, а где нет? Тут вопросов больше, чем ответов.

На практике на этих частотах хорошо воспроизводятся импедансы в пределах круга с КВСН<5 относительно 50 Ом.

-

On 11/8/2020 at 11:37 PM, Freesom said:

На самом деле это довольно скользкий момент. Где были референсные плоскости при снятии характеристик транзистора производителем мы можем только догадываться, т.к. нет схемы измерений и описания.

On 11/9/2020 at 5:07 PM, Freesom said:Транзистор был померян на другом материале другой толщины, или в другой оснастке и референсные плоскости при вычитании оснастки стояли где-то в другом месте. Где именно - можно уточнить у изготовителя (подозреваю что на концах выводов), вот только если у него был другой материал подложки, то толку от этого будет мало.

On 11/9/2020 at 6:38 AM, K0nstantin said:Да, вот это тоже хотел отметить да забыл, как сказал Freesom.

Местонахождение референсных плоскостей. Иногда в даташите/S-параметрах это указано или НЕ указано. Иногда ещё приводят измерения S-параметров образца с параметрами платы и отдельно S-параметры самой платы на проход (без образца), а дальше типа "вычитайте сами". И вроде бы солидные фирмы, а с измерениями беда...

S-параметры измерялись в плоскости, отстоящей на 0,04 - 0,08 мм от керамической рамки транзистора, т.е. практически вплотную к корпусу с минимальным технологическим зазором. На всех подобных корпусах транзисторов все известные производители делают именно так, поэтому в даташитах уже давно перестали об этом писать, т.к. это вполне очевидно. Есть старые AppNote, где про это напоминают. В любом случае лучше спросить у производителя, чем гадать и тратить время.

On 11/10/2020 at 1:43 AM, Freesom said:А, ну тогда примерно понятно. Измерение они проводят когда ноги транзистора распаяны на 50-омную линию, а в реальной плате ноги транзистора висят над огромным полигоном, а потом над щелью между корпусом и платой, т.е. там нигде 50 омами даже не пахнет. Как думаете, что там будет с адекватностью снятых характеристик?

Измерения проводятся, когда контакты транзистора подключены в линию с 10, 12.5 и 50 Ом. Искажения в измерениях в основном возникают, когда ширина вывода транзистора сильно не соответствует ширине микрополоска оснастки. В данном случае измерялось в 50-омной оснастке, на RO4003C-20 mil (0,508 мм). В этом случае ширина вывода транзистора и микрополоска очень близки к друг другу. Так что говорить о высокой погрешности измерений на этих частотах я бы не стал.

Что касается реальной платы и огромного полигона, так надо рисовать отдельно ввод на этом полигоне с шириной порта равной ширине вывода транзистора.

P.S. Основная ошибка автора темы в том, что для мощных транзисторов, работающих в нелинейном режиме, невозможно рассчитать выходную согласующую цепь по S22 малосигнальных S-параметров.

Алгоритм разработки согласующих цепей таков:

1) Входная и выходная цепь рассчитывается исходя из оптимальных импедансов нагрузки и источника транзистора. Импеданс источника транзистора может быть заменён на входной импеданс, если измерительная установка позволяет его измерить. В этом случае результат расчёта входной цепи будет более точным.

2) С помощью малосигнальных S-параметров дополнительно уточняется входная согласующая цепь, проводится анализ устойчивости. После этого вносятся необходимые корректировки АЧХ усиления и диссипативные цепи для достижения требуемой равномерности АЧХ и необходимого запаса по устойчивости.

Что касается типичного малосигнального |S22| GaN-усилителя на этих частотах, то значение в -3...-1 дБ вполне типично.

-

Если повышать мощность далее, то на графиках появляются крякозябы (не знаю что это за эффект, не это ли проблемы сходимости) На скрине красные линии - это пример.

Значит надо сузить область изменения импеданса в окрестности оптимальной точки.

А вольт амперные хар это ? влияние Vgs на IDS ? Модель прогнал через DC анализ по нему в диапазоне Vgs 2,79V 3,06V ток меняется от 150 мА до 2 А.Выходные вольтамперные (стоковые) характеристики: Id=f(Vds), при Vgs = {0, 0.5...10} V. Интересно увидеть полную картину тока насыщения стока и крутизны.

-

Да действительно мало. Начал заново переосмыслено прогонять симуляции и что то оба и старый и новый маловато мощности выдают. (либо транзистор на этой частоте не тянет, хотя по типовой схеме есть вариант 1800 Вт 230 МГц). Поднял напряжение на затворе до 3,05 В, это около 2 А тока ! И доступную мощность до 40,5 дБм - 11 Ватт и это на один транзистор, в даташите 7 Ватт на пару.

Импеданс источника у вас имеет неправильный знак мнимой части, потому неудивительно, что требуется 11 Ватт. Почему не желаете подать больше мощности на вход? Проблемы со сходимостью?

Импеданс нагрузки 1.35 + j1.7 вроде похож на правду и от изменения напряжения на затворе и входной мощности мало зависит. А гармоники напротив очень сильно влияют, хотя я не знаю какие импедансы должны быть на разных гармониках, просто перебирал варианты около нуля, около килоома, для каждой. Дальше у меня знаний и опыта не хватает.Гармоники так сильно не могут влиять. Выходной мощности почти в 2 раза меньше номинальной. Попробуйте построить выходные вольтамперные характеристики транзистора.

-

Если от академ к инженерии то человек задает критерии, допуски, выбор, подбор меша. К примеру в последних версиях программ меш может быть распределен неравномерно, значительно сокращая время машинного расчета.

Вообще уже очень давно используется алгоритмы генерации динамической сетки разной плотности с автоматической привязкой узлов к моделируемым объектам (адаптивная сетка). Человек, как правило, только может вручную регулировать постоянный коэффициент плотности сетки, и то, если желает усомниться в автоматическом алгоритме.

Вряд ли большинство инженеров будут с понятием относиться к таким настройкам как, например, функции базиса для аппроксимации уравнений Максвелла в единичном элементе и т.д.

Типовой инженер будет моделировать на настройках по умолчанию и для него результат будет восприниматься как истина в последней инстанции. И чем больше времени и машинных ресурсов было затрачено на получении этого результата, тем выше его ценность, значимость и интеллектуальность человека, поставившего такую сложную задачу машине.

-

Не совсем так, все в требуемых допусках, точностях и ими определяется, что задаётя корректным подбором меша.

Что будет являться критерием корректности и точности? Что из себя представляет операция "подбора меша" и кто её должен проводить: человек или машина?

GAN транзистор создание с нуля

в RF & Microwave Design

Опубликовано · Пожаловаться

Чаще всего изоляцию делают ионной имплантацией. Хотя RFMD+Triquint=Qorvo рисуют в учебниках (может только для наглядности), что изоляция выполнена удалением участков проводящего слоя GaN For Dummies. Хотя у них очень специфический техпроцесс, так что вполне может быть и старый способ.

Обычно при нормальной эпи-структуре никто не легирует и не травит. Тем не менее, операция вжигания омических контактов обязательна.

Я смотрю, что уже не первый раз Вы так сожалеете об этом. Не понимаю правда из-за чего. Диффузионная загонка примеси уже и на кремнии давно не используется (лет 20-30+), т.к. крайне малоэффективная, неточная, трудоёмкая и не позволяет получить нужный концентрационный профиль примеси по глубине. Разгонку примести иногда делают в диффузионных печах, предварительно загнав нужную дозу в подложку ионной имплантацией (но это только в специальных задачах).

GaN можно диффузионно пролегировать, но только после таких температур вся эпи-структура расплывётся и азот начнёт улетучиваться)

Лучше всего отверстия делать реактивным ионным травлением - статья, кроме того можно ещё лазером и даже сверлением.

Анизотропное травление происходит обычно до металлического стоп слоя.