doom13

-

Постов

1 575 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные doom13

-

-

8 minutes ago, Pasha said:

А если я прикручу мастер интерфейс axi-lite. Подключу его к интерконекту. А потом к интерфейсу slave axi-lite в процессорной системе. И буду посылать раз в несколько десятков милисекунд 2 слова по 32 байта в нужные мне адреса. А когда передам нужное количество просто дам прерывание. Так будет работать или обязательно нужен axi-dma, что бы он доступ к памяти обеспечивал?

Для случая DMA всё уже сделано за вас. Вам остаётся разобраться с работой DMA со стороны процессорной системы и сформировать из ваших "отчёты по 64бита" AXI4-Stream (разбить ваши данные на пакеты определённого размера, сформировать TLAST).

-

3 hours ago, Pasha said:

А то вручную организовывать AXI4stream master для меня та ещё задачка =)

Там нет ничего сложного, интерфейс с пятью портами реализовать: m_axis_aclk, m_axis_tvalid, m_axis_tready, m_axis_tlast, m_axis_tdata[n-1:0].

Можно и без tready, поставите фифо между вашим ядром и AXI DMA, которое будет буферизировать данные на время перезарядки DMA.

-

Для Zynq UltraScale+ смотрите в сторону High Speed SelectIO.

-

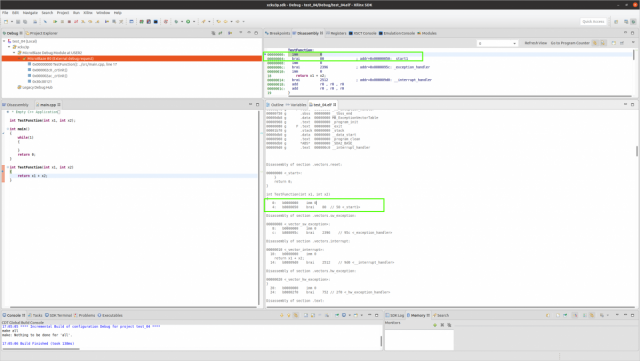

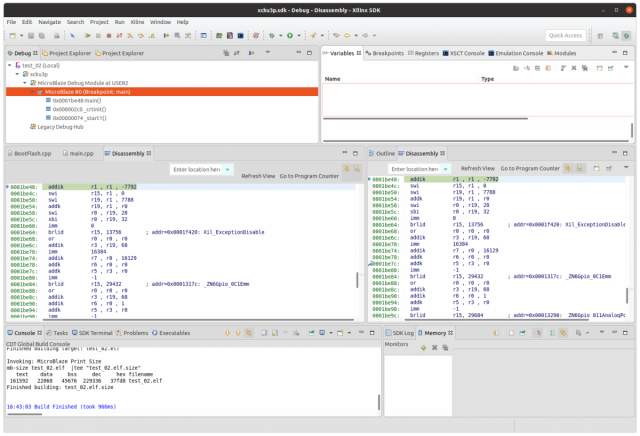

Пока проблему вижу в Xilinx SDK (может быть можно как-то настроить?). В настройках проекта в дефолтном состоянии установлены флаги для компилятора -ffunction-sections -fdata-sections и линкера --gc-sections (Enable garbage collector), которые и приводят к данной проблеме.

Для кода

int TestFunction(int x1, int x2); int main() { while(1) { } return 0; } int TestFunction(int x1, int x2) { return x1 + x2; }

c установленными в опциях проекта галками Enable garbage collector получаем следующее в elf-файле

Disassembly of section .vectors.reset: 00000000 <_start>: } return 0; } int TestFunction(int x1, int x2) { 0: b0000000 imm 0 4: b8080050 brai 80 // 50 <_start1> Disassembly of section .vectors.sw_exception: 00000008 <_vector_sw_exception>: 8: b0000000 imm 0 c: b808095c brai 2396 // 95c <_exception_handler> Disassembly of section .vectors.interrupt: 00000010 <_vector_interrupt>: 10: b0000000 imm 0 return x1 + x2; 14: b80809d0 brai 2512 // 9d0 <__interrupt_handler> Disassembly of section .vectors.hw_exception: 00000020 <_vector_hw_exception>: } 20: b0000000 imm 0 24: b80802f0 brai 752 // 2f0 <_hw_exception_handler> Disassembly of section .text:

если убрать разрешение Enable garbage collector, то всё сразу круто (за исключением размера бинарника)

Disassembly of section .vectors.reset: 00000000 <_start>: 0: b0000000 imm 0 4: b8080050 brai 80 // 50 <_start1> Disassembly of section .vectors.sw_exception: 00000008 <_vector_sw_exception>: 8: b0000000 imm 0 c: b808099c brai 2460 // 99c <_exception_handler> Disassembly of section .vectors.interrupt: 00000010 <_vector_interrupt>: 10: b0000000 imm 0 14: b8080a00 brai 2560 // a00 <__interrupt_handler> Disassembly of section .vectors.hw_exception: 00000020 <_vector_hw_exception>: 20: b0000000 imm 0 24: b8080330 brai 816 // 330 <_hw_exception_handler> Disassembly of section .text:

Криво сформированный elf-файл и приводит к тому, что SDK (если в Debug Configurations поставить галку Stop at program entry) отображает выполнение кода, который не должен был выполняться (реально выполняется startup sequence crt0.S).

Как исправить - вопрос открытый.

-

-

12 hours ago, Strob said:

А если в настройках Debug configuration поставить галочку Reset entire system, результат какой будет?

Не меняется ничего.

-

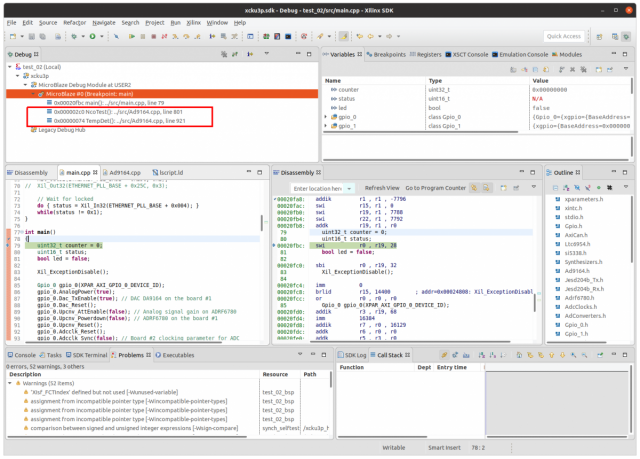

Приветствую.

При старте программы MicroBlaze и остановке на main() наблюдаю непонятное содержимое в стеке вызовов. Может кто сталкивался с подобным поведением и с чем оно связано?

Думал это связано с С++ проектом, но нашёл аналогичную проблему и для проекта на С тут.

Использую Vivado/SDK 2018.2, думал ситуация изменится при использовании Vitis 2020.1, но не помогло.

-

Приветствую.

Не могу найти в какой доке можно почитать про атрибуты для памяти, которые устанавливает:

void Xil_SetTlbAttributes(UINTPTR Addr, u64 attrib);

1. Хочу выделить некэшируемую область памяти.

2. Хочу ограничить возможность записи в определённые области памяти.

-

1 hour ago, Dvorkin said:

Все это хорошо было в Zynq. А вот в ZynqMP Ultrascale размер FSBL ограничен, часть OCM отдана под FSBL, часть под ATF. Сильно не разгуляешься...

Так для анализа состояния пина много кода и не потребуется.

-

Спасибо, попробую. По старту синтеза наверное будет правильнее чем по открытию проекта.

-

для hook_open_project добавил cd $prj_dir, дальше получилось стартануть скрипт

спасибо

-

12 minutes ago, RobFPGA said:

Прикольно - мне ваши логи отсюда виднее чем вам

И видно мне что относительный путь для синтеза немного не тот что вам из проекта кажется.

И видно мне что относительный путь для синтеза немного не тот что вам из проекта кажется.

Можно пример, как стартануть скрипт из папки проекта по нажатию кнопки синтеза

Такое

set_property STEPS.SYNTH_DESIGN.TCL.PRE {C:/Data/report.tcl} [get_runs synth_1]

не предлагать, спасибо.

-

25 minutes ago, RobFPGA said:

Проще всего указать скрипт в STEPS.SYNTH_DESIGN.TCL.PRE, а в самом скрипте привязываться к его же расположению в дереве проекта как я приводил выше.

Попробовал так

set_property STEPS.SYNTH_DESIGN.TCL.PRE "version/pre_synth.tcl" [get_runs synth_1]

синтез погнал, реакции ноль, если явно указать полный путь через гуи - работает.

-

Как из настроек проекта теперь достучаться к ::env(PWD), чтоб стартануть свой скрипт из папки проекта?

-

7 minutes ago, Nick_K said:

Там есть непечатный символ - я уже попадался на этом скрипте от уважаемого Роба

Так он же целых пять минут сочинялся)

set_param xicom.use_bitstream_version_check false puts "Script is processing" ### proc hook_proc {name hook_name} { if {[llength [namespace which {${name}_}]]==0} { rename ::${name} ::${name}_ rename ${hook_name} ::${name} } } ### proc hook_open_project args { puts "Hook of open_project" # processing input options for {set i 0} {$i < [llength $args]} {incr i} { set option [string trim [lindex $args $i]] switch -regexp -- $option { "-part" { incr i } "-read_only" { } "-quiet" { } "-verbose" { } default { # is incorrect switch specified? if { [regexp {^-} $option] } { send_msg_id Vivado-projutils-001 ERROR "Unknown option '$option', please type 'open_project -help' for usage info.\n" return } set prj_file [file normalize $option] } } } set prj_dir [file dirname $prj_file] set ::env(PWD) $prj_dir uplevel 1 ::open_project_ $args puts "Script is done!!!" } hook_proc "open_project" "hook_open_project"

Пытаюсь разобраться, как оно работает, получаю лог

*** Running vivado with args -log xczu9eg.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source xczu9eg.tcl ****** Vivado v2018.2 (64-bit) **** SW Build 2258646 on Thu Jun 14 20:02:38 MDT 2018 **** IP Build 2256618 on Thu Jun 14 22:10:49 MDT 2018 ** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved. Sourcing tcl script '/home/andrei/Programs/Xilinx/Vivado/2018.2/scripts/Vivado_init.tcl' Script is processing source xczu9eg.tcl -notrace WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {11} -id {[BD 41-1271]} -suppress '. The existing rule will be replaced. WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {10} -id {[BD 41-1306]} -suppress '. The existing rule will be replaced. WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {3} -id {[BD 41-1271]} -suppress '. The existing rule will be replaced. WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {4} -id {[BD 41-1306]} -suppress '. The existing rule will be replaced. WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {5} -id {[BD 41-1271]} -suppress '. The existing rule will be replaced. WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {7} -id {[BD 41-1271]} -suppress '. The existing rule will be replaced. WARNING: [Common 17-1361] You have specified a new message control rule that is equivalent to an existing rule with attributes ' -ruleid {6} -id {[BD 41-1306]} -suppress '. The existing rule will be replaced. add_files: Time (s): cpu = 00:00:07 ; elapsed = 00:00:07 . Memory (MB): peak = 2551.223 ; gain = 920.449 ; free physical = 1915 ; free virtual = 11697 Command: synth_design -top xczu9eg -part xczu9eg-ffvb1156-2-i Starting synth_design Attempting to get a license for feature 'Synthesis' and/or device 'xczu9eg' INFO: [Common 17-349] Got license for feature 'Synthesis' and/or device 'xczu9eg' INFO: Launching helper process for spawning children vivado processes INFO: Helper process launched with PID 1454

Что-то не так? hook_proc не вызывался

15 minutes ago, RobFPGA said:В контексте Vivado переменная PWD есть так как она добавлена после копирования enviroment из запускающего процесса.

посмотрите в TCL консоле - parray ::env

Да, есть такое, спасибо.

-

Форматирование какое-то видно было неправильное, ещё раз скопировал - не ругается.

Но значение pwd не изменилось, на дефолтную директорию ссылается.

-

56 minutes ago, RobFPGA said:

например

Оно должно работать? Выдаёт ошибки.

-

4 minutes ago, RobFPGA said:

Когда именно вы хотите запускать скрипт? При выполнении какого действия?

Перед стартом синтеза, скрипт должен сгенерить константы для контроля версии.

4 minutes ago, RobFPGA said:Вы можете добавить любые свои процедуры и хуки в Vivado_init.tcl

Я попробовал добавить, но всё не так просто)

cd [get_property directory [current_project]]

-

-

Приветствую.

Возможно ли при открытии проекта в Vivado запустить TCL скрипт.

Хочу, чтоб при при открытии проекта переменная PWD указывала на директорию проекта (без привязки к конкретной директории и ПК).

-

On 1/9/2020 at 8:24 AM, Opex said:

У нас в обычном Цинке сделано так: сначала идет рабочая прошивка, затем аварийная. Какой-то встроенный загрузчик ищет волшебную комбинацию байтов, если находит, грузит прошивку. При обновлении, сначала стираются волшебные числа, записывается прошивка, если все записалось хорошо, записываются числа.

Сделал аналогично.

On 1/25/2020 at 4:58 PM, toshas said:Это "классический" подход для мультибут по xapp1081, я тоже посоветовал бы сделать по нему

Не сразу нашёл эту доку, больше смотрел по ZynqMP, а там предлагают из FSBL делать переброс на рабочую прошивку, работает, но не понял зачем такие сложности, если можно просто поменять их местами.

On 2/11/2020 at 3:44 PM, Dvorkin said:Кроме ошибки обновления прошивки могут быть и глюки в рабочей программе (app_a53_X.elf). По самым разным причинам, человеческий фактор никто не отменял, увы. Или повреждения рабочей прошивки в процессе работы.

Могу предложить такой алгоритм:

1) Рабочая программа после успешного запуска сбрасывает счетчик загрузок.

2) Стартует сначала резервная прошивка, в FSBL делается проверка счетчика загрузок, если он меньше N, то:

2.1) счетчик инкрементируется, в MultiBootReg записывается адрес рабочей прошивки (ну, или просто инкремент), делается soft reset, грузится рабочая прошивка.

2.2) иначе ничего не делается, продолжается загрузка резервной прошивки.

Счетчик может храниться в специально выделенном разделе FLASH.

В моём случае самая обидная ситуация - залить прошивку с нерабочим Ethernet. Используется FreeRTOS и при обновлении hdf-файла настройки bsp всё время сбрасываются. Если не проконтролировать, высока вероятность получить нерабочее устройство. Хороший вариант со счётчиком загрузок, вообще думали в новой версии железа вытащить порт процессора, по которому загрузчик определял бы рабочий или аварийный режим запуска.

-

7 minutes ago, haker_fox said:

Плохо, помню, но в LwIP 1.4.x делал низкоприоритетную задачу с поллингом в 500 мс. Она стучалась к фитеру, и запрашивала статус кабеля. Раз так сделал, то, видимо, не нашёл событя.

Спасибо, с этим понятно. Думал так делать, но пока пытаюсь понять. есть ли стандартная опция/возможность.

8 minutes ago, haker_fox said:Хотя, стоп! А стэк, вроде и не должен такое событие давать. Ведь о кабеле только PHY может сказать. А у неё прерываний нет... Или вы не о включенном/отключенном кабеле?

Если кабель дёргать то сообщения в stdout кидает (если не ошибаюсь), поэтому решил, что оно само мониторит состояние сети и возможно есть какая-то возможность привязаться к данному событию.

//netif.h #if LWIP_NETIF_LINK_CALLBACK /** This function is called when the netif link is set to up or down */ netif_status_callback_fn link_callback; #endif /* LWIP_NETIF_LINK_CALLBACK */ #if LWIP_NETIF_LINK_CALLBACK void netif_set_link_callback(struct netif *netif, netif_status_callback_fn link_callback); #endif /* LWIP_NETIF_LINK_CALLBACK */

Такое вот нахожу

-

Приветствую.

Есть ли какое-то событие/семафор/др. при срабатывании link up/down?

Хочу сделать, чтобы задача спала, пока нет линка или засыпала, когда пропал.

-

12 hours ago, doom13 said:

Смотрю, что умеет стартануть более свежую прошиву, которая лежит во flash.

Что-то не могу повторить полученный ранее результат. Вопрос где хранится timestamp образа и как его туда поместить?

Для формирования boot.bin используется bif-файл с содержимым:

//arch = zynqmp; split = false; format = BIN the_ROM_image: { [pskfile]/home/user/workspace/xczu9eg/boot/psk0.pem [sskfile]/home/user/workspace/xczu9eg/boot/ssk0.pem [auth_params]spk_id = 0x00000000; ppk_select = 0 [fsbl_config]a53_x64, bh_auth_enable [bootloader, authentication = rsa]/home/user/workspace/xczu9eg/xczu9eg.sdk/fsbl/Debug/fsbl.elf [pmufw_image]/home/user/workspace/xczu9eg/xczu9eg.sdk/pmufw/Debug/pmufw.elf [authentication = rsa, destination_device = pl]/home/user/workspace/xczu9eg/xczu9eg.runs/impl_1/xczu9eg.bit [authentication = rsa, destination_cpu = a53-0, exception_level = el-3]/home/user/workspace/xczu9eg/xczu9eg.sdk/app_a53_0/Debug/app_a53_0.elf [authentication = rsa, destination_cpu = a53-1, exception_level = el-3]/home/user/workspace/xczu9eg/xczu9eg.sdk/app_a53_1/Debug/app_a53_1.elf }

Zynq7000 Запись данных из PL в ddr через dma

в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Опубликовано · Пожаловаться

Это событие как часто происходит? Размер данных для отправки на ПК какой?

Ещё можете в сторону AXI DataMover посмотреть.