evg123

-

Постов

350 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные evg123

-

-

Общ. замечания:

Почему не посчитать фильтр в ADS. Там и FEM нормальный и моменты есть. AXEIM - вообще замечательный инструмент. Он, будучи методом моментов - сделан оч. качественно.

Всё что мы не считали в FEMе для ADS очень хорошо совпадало с AXEIM-ом. Вы делали деембеддинг разъёма? Может он вам портит картину?

-

В ADS есть чудный инструмент impedance matching.

-

Завод имени Пупкинда :blink: Да реально никто...

Есть производители. Даже не далеко от того места где мы располагаемся. Просто в интернете их нет. Да и резистор сильно специфический - такие особо никому не нужны кроме сильно страждущих (типо меня) :laughing: .

-

...ADS не та среда которая заточена

для подобного дизайна. С таким же успехом Asoft, Genesys, и прочие. Как бы там не увидишь

Realized Gain и всякие КПД, плюс распределение токов и много чего еще, втч в ближней зоне и пр.

Эт. вопрос спорный...

-

По ходу работ возник ещё вопрос: нужны СВЧ thin-film - резисторы 0402. Пока нашли двух поставщиков только:

http://www.vishay.com/docs/53014/ch.pdf

и

http://www.koaproducts.com/shdr_en.php#08

Нам нужны номиналы 100, 50 и ~90 Ом. (Несимметричный микрополосковый делитель требует нестандартного сопротивления ~90 Ом, ближайший из рядя Е12 - 82 Ома), а такие у этих ребят под заказ.

Причём Vishay в нашем диапазоне (20ГГц и выше) предлагает лучшие частотные характеристики чем KOA.

Вопрос: какие ещё производители кроме Vishay и KOA производят СВЧ 0402 thin-film - резисторы?

-

Я не много не понял про ядра...

Про ядра: (рис 1. б - наша конфигурация)

http://www.pcbtech.ru/pages/view_page/116

Снизу полоски, сверху резонаторы, в середине - препрег. "Ядро" - это просто другое название ламината. Ro4350b - это как раз ядро. Ro4450b - препрег.

Допуск на протравы - то что мне сказал производитель - 1 толщина фольги - т.е. 35 микрон.

Про прессование - всего два препрега - их (со слов производителя) особенно то и не спрессуешь.

Моделировал разброс параметров по препрегу (толстый и тонкий) - это влияет на характеристики резонатора - в общем удовлетворительно. (Лучше толстый чем тонкий).

Про КМПП - пока не нашёл адекватную модель. Может у кого-то что-то есть? (То, что предлагает аналист - не очень-то устраивает.)

На разъёме (на ките) припоя оч. мало.

Режим эксплуатации - малые мощности (сотни милливатт).

Спасибо за SowthWest и Джурджинского.

-

Может пойти от простого...

Что мешает сделать измерительную перемычку с двумя такими соединителями на концах? Только плату и дорожки посторайтесь сделать как у Вас в проекте.

А потом зная полную матрицу S-параметров по принципу симметричности сделать экстракцию "полуперемычки". Или вообще Вашего соединителя зная параметры микрополоска. Мне кажется, что опорную плоскость лучше сместить на некорорую длинну от места пайки. Как я понимаю основная цель сделать с минимальным КСВ и знать электрическую длинну. А остальное не так важно

Вот например всех уж тыкаем в SouthWest. Делают при помощи TimeDomain исследования вариантов подключения к МПП.

Вот кстати говоря день это обдумываю. В точности, то что вы озвучили. :rolleyes:

-

Материалы:

Два ядра Ro4350b. Склеены двумя препрегами Ro4450B.

Одно ядро (0.254) - для питающих микрополосков.

Второе ядро (0.508) - для резонаторов.

Препреги - 0.101 - две штуки.

КМПП:

http://www.fairviewmicrowave.com/sma-femal...r-sc3060-p.aspx

Хотим такой или подобный.

Вопрос в том, что их S-параметры не указаны. Как сделать деембеддинг (чтобы выйти на реальные параметры) - пока не знаю, разбираюсь.

Есть ли что-то лучше, чем такой наплатный разъём в плане вносимой неоднородности?

Изготовитель:

Плату делает наш местный подрядчик. Имеет оборудование в Китае. Минимальный отверстие под механическое сверление - 0.2 мм.

Обратное сверление - не делает. Вполне достойный. (Впрочем - посмотрим). Поверхность будем порывать иммерсионным золотом.

Моделировали(FEM) в ADS, потом в Analyst-е. Результаты отличаются где-то на 10%. Общий вывод - респект и уважение ADS-у. У него всё как-то пошустрее.

Т.к. на таких частотах межслойные отверстия могут внести сильные искажения в характеристики антенны.Выбирали размеры антенных резонаторов, чтобы на нашу частоту они входили в резонанс, далее запитывали резонатор через полосок и переходное отверстие,

и выводили параметры микрополоска, чтобы S11 давал хорошие результаты. Моделировали как единую электромагнитную структуру.

-

В чем проблемма!? На выход генератора повесить 3дб аттенюатор.

Согласен. Но это вопросов ни разу не снимает. В готовом устройстве (стенд - это макетная стадия) антенна должна быть тщательно вылизана. Суть стенда как раз, чтобы отработать топологию.

Расcчитали её в ADS, проверили в каком-нибудь другом САПРе. Сделали стенд.

А дальше вопрос не в том, чтобы запустить стенд, а в том, чтобы довести антенну до удовлетворительного состояния, чтобы она могла без проблем работать с MMIC в готовом устройстве.

Сейчас мы имеем ряд китов, на которых можно макетировать, а далее это всё надо упаковывать в один конструктив на одной плате.

-

Преамбула:

Проектирую патч антенну. Она представляет собой несколько сфазированных резонаторов на одной стороне и платы, и питающие микрополоски - на другой стороне. На плате SMA - разъём, к которому подводится мощность, которая по микрополскам через межслойные перемычки попадает на резонаторы. Буду собирать стенд: генератор, СВЧ-кабель, антенна. Основной вопрос в КСВН. На частоте 20ГГц, тот генератор, что буду использовать - требует КСВН <= 2.0 . Т.е. изготовленная плата (с антенной и питающими микрополсками), припаянным к ней SMA-разъёмом и прикрученным к ней (конечно же динамометрическим ключём) СВЧ кабелем в сумме должны дать КСВН меньше двойки.

Вопрос:

Как этого добиться с минимально возможным числом итераций производственного цикла?

Возможное рещение:

1)Очевидно, что для расчёта использую САПР (ADS), рассчитываю топологию.

2)Изготавливаю пробный вариант платы по расчёту.

3)Припаиваю разъём (board edge connector). Для измерения КСВН подключаю через кабель VNA и строю диаграмму Смита. (Калибрую VNA так, чтобы убрать неоднородность, вносимую кабелем). Постороил.

4)Далее - использую процедуру деембеддинга неоднородности, вносимой SMA-разъёмом. В результате нахожу диаграмму Смита но уже без разъёма.

5)По этим эксперементальным данным рассчитываю согласующий микрополосок, чтобы идеально согласовать вход платы (сразу после разъёма) на 50 Ом.

6)Изготавливаю второй вариант. И готово!

Но:

Вопрос №1: есть ли такая процедура деембеддинга моего SMA разъёма по эксперементальным данным?

Вопрос №2: насколько можно верить результатам моделирования? Не получится ли так, что изготовленная плата настолько уплывёт по параметрам от ожидаемых (даже от ADS при всём к нему уважении), что согласующий микрополосок (на 5-ом шаге) будет сделать невозможно?

Вопрос №3: Что я сказал не так, как всё это можно оптимизировать?

-

Приложил три проекта.

Исходные условия такие:

1. Имеется круглая патч-антенна. Материал Ro4350b (в данном случае), Er = 3.55 . Диаметр антенны - 3.4 мм. Толщина подложки - 0.5 мм.

2. Антенна возбуждается в точке, отстоящей от центра круга на половину длины радиуса. (В центре, естественно, она возбуждаться не может, так как тогда не будет излучать.) Частоты анализа - 24ГГц - 25ГГц с шагом в 100 МГц.

3. В данный момент интересует параметр S11 - его изображение на диаграмме Смита.

4. Проведено три варианта моделирования:

4.1. Первый вариант - Axiem. Название проекта - CirclePatchAntenna_Axiem. Бесконечная проводящая подложка, в месте возбужения антенны наложена маленькая заплатка, к которой подсоединён edge-port. Порт имеет "безусловный референс" к подложке. Результат моделирования - рис. №1. Время моделирования - 15 сек.

4.2. Второй вариант - опять Axiem. Название проекта CirclePatchAntenna_Axiem_2. В данном случае бесконечная проводящая подложка заменена на конечную, размером 50 х 50 мм. Патч антенна располагается в центе этой вируальной земли. От точки возбуждения к виртуальной земле опущена перемычка (via) точно такого же вида, как и патч в первом варианте. В виртуальной земле там куда приходит перемычка (via) - выполнено прямоугольное отверстие, чтобы via не замыкалась на землю. Между via и виртуальной землёй вставлен дифференциальный порт, через который вводится возбуждение на антенну. Моделирование длится больше часа (64 система, 8 ядер, 4 ГБ). Результат моделирования показан на рис.2 .

Рисунки 1 и 2 почти совпадают. Разница едва заметна.

4.3. Третий вариант - берём EmSight. Название проекта CirclePatchAntenna_EmSight. Размер короба устанавливаем 50 x 50 мм.

Дно - совершенный проводник (как и в п.п. 4.1 и 4.2). Высота подложки 0.5 мм, как в предыдущих моделях. Боковые стенки возвышаются над диэлектриком на 0.1 мм (т.е. слой воздуха очень тонкий - 0.1 мм и боковых стенок можно сказать - нет). Верхняя часть короба - открыта. Антена помещена в центр короба. Возбуждение антенны осуществляется через via-port. Вид и размер этого via-порта - точно такой же как в п. 4.2. То есть электромагнитная структура 4.3 практически точно совпадает с электромагнитной структурой 4.2. Моделирование длится несколько мин. Диаграмма смита приведена на третьем рисунке. Она ни разу не совпадает со второй.

Вопрос почему? Что я сделал не так? Кто может объяснить? Прилагаю сами проекты.

-

By the way, Rogers substrates are quite temperature stable. I have heated one of my filters up to 100 deg and had no visible frequency shift (that was a narrowband split ring resonator).

Оч. ценно.

А на какой вы частоте его делали? с каким материалом? (если не секрет, конечно).

-

Спасибо за реплики. То есть делаем E_design.

для VitaliyZ вопрос:

You would get more certain answer from Rogers directly. Write them an email.I usually use "E_design", but almost always get a frequency shift.

Вы пишите что был сдвиг по частоте. Для модели это понятно, а вот соответствовала ли потом ваша модель реалиям, когда уже плата изготовлена? То есть получили ли вы то что хотели,

или потребовался откат к меньшей диэлектрической проницаемости?

Для depoff вопрос:

Для Ro4003 всегда использовал E_design = 3.55 вместо E_process = 3.38. Моделирую в Микровэйв. Параметры рассчитнанного фильтра ушли вверх по частоте... Всре же использую E_design = 3.55, а фильтры больше не делаю)Не совсем понятно, что вы хотите сказать. Моделируете, изготавливаете, тестируете и что? Можно поподробнее?

Пробовать разные варианты - чесно говоря не хочется, это не дёшево. Хотелось бы воспользоваться советом опытных.

Ещё вопрос: как Ro4350B ведёт себя на 25 ГГц? Какой у него тангенс угла потерь? По даташиту - дан 0.0037 для 10 ГГц. Что можно ожидать на 24?

-

Например, для Ro4350 (который мы собираемся использовать) даны в datasheet-е две диэлектрические проницаемости E_process = 3,48 и

E_design = 3,66

Мужичок из Роджерса:

http://blog.rogerscorp.com/tag/dielectric-constant/

рассказывает, в чём разница. Суть в том что везде при моделировании надо использовать E_design, а не E_process.

Но тогда непонятно почему в установках по умолчанию, когда я выбираю не "пользовательский" материал, а Роджерс Ro4350, выпрыгивает как раз диэлектрическая проницаемость E_process,

а не E_design.

Для нас вопрос - существенный, так как размеры микрополосков - значительно меняются, если перейти от E_design к E_process. Опять же мужичок из ролика.

-

Прикручено всё небось на стойках к отверстиям, которые на плате являются землей. То есть что есть оргстекло, что его нету - никакой разницы. Проще загубить плату, если предварительно её заземлить и начать пальцами лапать микросхемы, при этом пошаркивая резиновой обувью по коврам и т.д.. Вот тогда статика и потечёт через все нутро микросхем на землю.

Или надеть заземляющий браслет и шаркая оргстеклом по обычному столу лапать те же микросхемы. С оргстекла через землю на плате всё потечёт на палец и заземляющий браслет. В обоих случаях всё вылетит из строя, и виновато в этом не оргстекло, а наличие пути, по которому потечёт ток....

Нет, там на плате нет на стойках земли. Отверстия изолированы. (Мы у себя такой собрали с этими платами). Платы уж больно дорогие. Проблема-то в чём? Собрали мы у себя - как на ролике. Потом потерлись локтём и видим, что стекло электризуется. (В общем, и так было понятно, что что-то такое будет). Обернули его по периметру алюминевой фольгой и её заземлили. Теперь трись-не-трись - заряда нет. Плюс заземлённые источники питания. Плюс браслеты.

Спасибо большое всем, кто участвовал. Было полезно узнать разные мнения.

-

Не знаю как у них, но если кто боится статики, то может взять пластики с небольшой проводимостью.

Меня это и интересует. Что за пластики? Где о них можно почитать?

А в чём проблема? Правильно собранная схема статики не боится. Боятся статики компоненты до впаивания на плату. Да и то уже далеко не так, как раньше...А как же испытания на пробой (при сертификации)?

-

А вот еще есть технологии напыления серебра на стекло http://www.lzsk.ru/documents/nizkoemis_steklo.html

С таким напылением статики не будет :)

Это любопытно.

прозрачная прямоугольная пластина из видео не обязана быть оргстеклом.Они должны быть извращенцами, чтобы сверлить дырки в обычном стекле. Всё остальное - варианты оргстекла.

-

Смотрю ролики на сайте TI, где они демонстрируют свои комплекты разработчиков быстродействующих ADC и DAC.

Например:

http://www.ti.com/tool/TSW2200EVM

Там внизу странички есть два видео-ролика.

Они все свои стенды собирают на орг-стекле. Монтируют на нём кучу дорогущих плат.

Не понимаю, как они не боятся электростатики? Как они защищаются?

Одна плата стоит, например, 1500$ по их каталогу. Как-то жалко её убить электростатическим разрядом!

Кто может что-то вразумительное сказать по этому поводу?

-

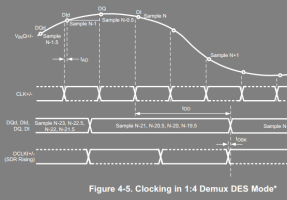

Использую ADC12D500RF. Цифрую сигнал на частоте 375МГц (может быть также 187 МГц).

Тактовый сигнал 500 МГц. Используется так называемый DES - dual edge sampling.

То есть преобразование происходит как по переднему фронту так и по заднему.

Форма сигнала - несимметричная (последующая обработка требует этого). То есть: по фронту - первое преобразование,

через 3/8 такта - спад - второе преобразование, далее - 5/8 такта - перерыв и всё повторяется сначала.

Полученные данные делятся на два потока (чётный и нечётный) и затем обрабатываются алгоритмами, напоминающими те, что обрабатывают квадратурные потоки.

Вопрос: Как сделать высокостабильный тактовый генератор с такой формой сигнала? Требования по дрожанию фронтов обсуждаются, но ясно, что они должны быть не хуже чем 14 пикосекунд.

Можно ли использовать для этого DDS-ы типа AD9914, и можно ли потом использовать clock distribution ic, чтобы потом запитать таким размноженным клоком несколько таких АЦП?

-

Вы попробуйте развести один и тот же проект (с напряжными времянками естественно) под V6 и под A7. И сразу всё поймёте. Я вот тоже недавно хотел сэкономить и перетащить свой проект с K7C325T на A7200T.

И сразу понял почему один чип стОит 1500 енотов, а другой - всего 400. В общем, чудес не бывает.

Я про то же (насчёт чудес). Можно поподробней про проблемы, что у вас были с переносом?

-

Но в A7 есть ещё возможность пользоваться HLS (high level synthesis) - давать описания на C/C++. У V6 такого нет.

Впрочем, по user I/O pins V6 eval board выигрывает. Там есть два FMC (HPC и LPC). Но засада в том, что если один коннектор задействуешь, то другой уже бесполезен - конструктивно туда уже ничего не воткнётся.

Возможно, подводный камень в том, что качество разводки приложения на V6 может быть выше чем на A7 из-за стэковой тенологии? V6 это, можно сказать, монолит, а 7-мая серия построена по другой технологии? (Stacked Silicon Interconnect (SSI) Technology)

-

По цене:

EVAL BOARD для Virtex6 - 1800$ ( http://www.xilinx.com/products/boards-and-...-V6-ML605-G.htm )

EVAL BOARD для Artix7 - 1300$ ( http://www.xilinx.com/products/boards-and-...-A7-AC701-G.htm )

Если сравнивать характеристики V6 и A7 то по всем позициям

A7 (200T) сильнее V6 (195T). (По количеству слайсов, памяти, dsp-слайсов и т.д.)

+A7 выигырвает по технологии - то есть по тактовой частоте.

Почему же цена на A7 меньше чем на V6? (V6-195T на digikey-е 1200$), на A7 цена ещё не выставлена, но ожидается порядка 800$.

Вопрос возник потому, что хотим покупать eval board, и в затруднении, какой выбрать - первый или второй.

-

По поводу статей как програмировать на кубиках - устанавливаете матлаб, берёте кит TMS320F28335 и прогоняете все примеры. Там их море. С каждым разбираетесь. 1-2 месяца и вы будете плавать как рыба в воде. Это будет получше, чем статьи. Заодно и всю периферию процессора освоите.

Так ведь так оно и есть! Чтобы иметь такую точку зрения, достаточно поиметь опыть разработки все этих частей иерархии девайса. И тогда сразу становится все на свои места - сколько времени и сил уходит на низкий уровень (если не транзисторный, то хотя бы гейтовый при разработке ИМС в схемотехнике, и низкоуровневый в программировании на уровне оптимизации под архитектуру) - работа с готовыми и отлаженными блоками близка к отдыху на любимом курорте по сравнению с рутиной разработки самих блоков. Поэтому очень даже корректно будет сказать - что девайс сделали те, что сделал сами "кубики", а не тот, кто их соединил между собой. И деление заработанных средств "по понятиям" было бы правильным - 90% тем, кто делал блоки, и 10 тому, кто их соединил.Да я, собственно, с этим не спорю. Кубики конечно сделали они. И примеры дали они. Но их, извините, в MathWorks Inc - 2500 программистов в 14 странах (данные по прошлому году). Как мне одному с ними тягаться? Собственно, в целях экономии времени пришлось освоить технологию, т.к. начальство стояло над душой. Как всегда, требовался результат. До того я писал на 5509a в DSP/BIOS и, сравнивая, скажу, что чтобы глубоко освоить технологию матлаба - т.е. понять как генерируется код, и, далее, как его сгенерировать так, как ты хочешь - требуется больше усилий, чем для освоения и DSP/BIOS и CCS (для написания несложных многопоточных приложений с очередями, семафорами и др. функционалом этой оси). Зато после понимаешь, что время потратил не зря. Писать-то надо по-минимому. Однако, согласитесь, что одному человеку разобраться в том, что нагородили 2500 программистов (ну пусть даже не 2500, а всего каких-то пару десятков, вовлеченных в интеграцию с Техасом), и далее на этом сделать законченную работающую вещь - это не мало.

В конце концов, все мы используем готовые компиляторы, готовую CCS-среду, CSL-библиотеки, DSP/BIOS (попробуйте его написать сами), готовые FPGA - коры; далее мы пишем программы, делаем прибор, в итоге, говорим, что вот - мы сделали девайс! То что в этом девайсе нашего-то - не более 5% - мы об этом скромно умалчиваем. Я сделал то же, и сказал - вот - законченная вещь. Не вижу никакой разницы между разработчиком из-под матлаба и любым другим разработчиком, который использует готовые среды, готовый компилятор, готовые библиотеки, готовые стэки протоколов, готовый ISE или Квартус с библиотеками программных коров и наборами аппаратных ядер внутри плисов, готовый Modelsim для оценки результатов своей работы, готовый expedition для разводки плат. Мы (и вы и я) - живём-то на всём готовом :rolleyes:.

И наше участие (и ваше и моё) в конечном устройстве - минимально. Согласитесь. То, что у кого-то есть опыт разработки разных уровней от ассемблера и VHDL до C++ и матлаба: так что с того? И у меня он есть.

Но компиляторы и среды мы-то с вами не писали? А только пользовались всем готовым.

По поводу сил, которые уходят на низкий уровень скажу, что сил много на низкий уровень не уходит... Чтобы прийти к более-менее конечному результату - уходит много времени, а не сил.

(Все мы нормальные люди, работаем по 8 часов в день с выходными и праздниками. Если есть другие - то не это надолго, потом тоже скоро становятся нормальными :rolleyes: ). Инженер на каждом уровне программирования (высоком или низком) - решает задачи (сложные или простые). Если кто-то за вас уже написал хороший компилятор, создал хорошую библиотеку коров, написал хороший FPGA - симулятор, то вы по-просту решаете другие вопросы, которые за вас ещё не сделали. И всё. Никогда нельзя сказать, что задачи низкого уровня сложнее задач высокого уровня. Всякая задача (ИМХО) становится простой (или очень простой), если её грамотно дефрагментировать. Независимо от того, это множество конечных автоматов, взаимодействующих между собой внутри ПЛИСы или программа разводчика печатной платы.

Далее по теме:

Мне пришлось самому сделать только несколько кубиков: первый кубик реализовывал интрефейс с датчиком ЛИР (абсолютный датчик положения), в этот кубик была записана S-функция, которая запускала один из УАРТов в пакетном режиме (там хитрый УАРТ: он может работать в аппаратном пакетном режиме) и в процессе работы получала от него данные. Такого кубика не было в стандартной библиотеке - пришлось реализовывать самому.

Второй кубик - вызывал стандартную техасовскую библиотеку FIR-фильтра. Этот кубик значительно быстрее работал, чем если бы делать FIR-фильтр из стандартных кубиков simulink-а. Прежде чем его сделать пришлось конкретно по-потеть.

Достаточно сложной была подсистема определения скорости ротора, особенно на малых скоростях. Датчика скорости не было, был только датчик положения. Дифференцирование данных от датчика положения - задача, как известно математически некорректная. Пришлось делать кубик осуществляющий калмановскую фильтрацию.

А всё остальное: стандартный УАРТ для онлайновой регистрации графиков работы устройства на экране ПК, стандартный CAN для получения уставок позиционирования со стороны управляющего ПК, стандартные два АЦП для оцифровки данных от датчиков токов фаз, различные ПИД регуляторы и нелинейные звенья - всё было взято из стандартной библиотеки матлаба для F28335.

В итоге программа задействовала след. периферию: 2 АЦП, 1 CAN, 2 UART-а, 3 сдвоенных PWM-а, одна trip-зона.

На разработку ушло где-то два месяца. По моим оценкам - такая же разработка без матлаба - полгода.

-

Я извиняюсь что немного в сторону от хода диалога. Зато по сути вопроса.

Я год назад подсел на матлаб и генерирую код TMS320F28335 исключительно из квадратиков симулинка.

Сделал на F28335 позиционный регулятор на безколлекторном двигателе. Работа в ручную (по моим оценкам) заняла бы 6 мес., работа на матлабе - меньше двух. Качество генерироуемого кода (я бы сказал) изумительное. Гибкость очень большая (вплоть до того, что можно желаемый квадратик поместить в желаемую секцию и соответственно в ОЗУ или во флэшь). Программа - это симулинковская модель с подсистемами. Использую также матлабовский профайлер и на лету вижу в виде диаграмм какое прерывание у меня когда кого перехватило и т.д. Удобство. Осцилограф подключать не надо.

Только надо всё равно разбираться в деталях, что он нагенерировал. Но генерирует славно! проверять за кем то это ведь не самому писать.

ЗЫ На DSP/BIOS писал раньше под 5509а. Надо сказать вещь достойнейшая.

Дикие потери RO4003C (Ni-5мкм Au-0.1мкм) из-за чего?

в RF & Microwave Design

Опубликовано · Пожаловаться

У нас на 24 ГГц разъём меняет реальную картину S-параметров до неузнаваемости. Специально для этого делаем тестовые платки холостого, короткого замыкания и нагрузки на длинную согласованную линию, чтобы полноценно определить S-параметры разъёма для деембеддинга. У вас он может быть плохо припаян. Лишний припой и т.д., и т.п. Возможно сам разъём на вашей частоте резонирует (у нас такое было - в плату не поступал сигнал, пропадал в разъёме). Вы не думали об этом? Можете выложить фотки реального устройства?

Мы пользовались Ro4350b - тоже грешили на качество ламината, полосков и т.п.- потом сделали рентген, посмотрели в микроскоп и поняли что всё оч. даже качественно, дело было в резонансе разъёма и ещё в качестве припоя.

AXIEM - великолепное средство расчёта полосков, я в этом тоже убедился.