URIK-ZZZ

-

Постов

34 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные URIK-ZZZ

-

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

1 hour ago, Alekc said:В CAM350 v.14. Все нормально.

То есть получается софт глючит?

Может посоветуете что нибудь. У меня 10.7 под XP.

Просто когда я его удаляю, удаляется пол платы, ну вся связанная зелёнка.

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

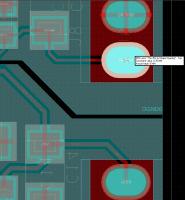

Здравствуйте!

Гербер сделал в аллеро. Плата будет самопал. На прозрачную плёнку печатается негатив, через которую контактным способом засвечивается плёночный фоторезист на плате. Негатив получил через экспорт и опять импортировал в CAM. Но на негативе откуда-то взялся отросток. Подскжите пожалуйста как его удалить или сделать, что бы он не появлялся.

Файлы: BOTTOM.art - из аллегры, Layer_1.art - негатив. Ну и что показывает.

Зы: давно на форуме не был интерфейс подзабыл.

ЗЫЫ: всю тему просмотрел, что то ничего не нашёл.

-

12 hours ago, Uree said:

Вообще не там ищите, это настройки, а не объекты дизайна... Setup -> User Preferences и там есть строка, в которой можно вписывать то, что нужно найти.

Спасибо! Получилось!

-

-

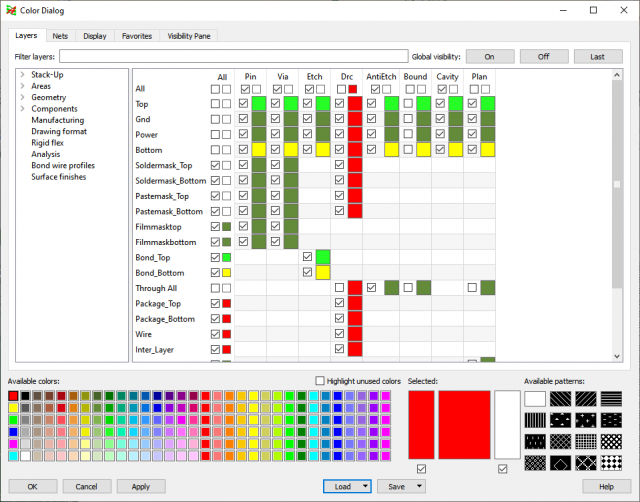

Нашлось слава богу, какой же я не внимательный, искал в Shape_fill а надо было в Opengl.

Может ещё кому-то понадобиться в 16.6

Setup - User Preferences - Display - Opengl - static_shapes_fill_solid.

-

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

7 hours ago, Flood said:Есть настройка, что-то вроде static shape solid fill (точно не помню, поиск по solid) - она включает отображение статических шейпов аналогично динамическим - сплошной заливкой.

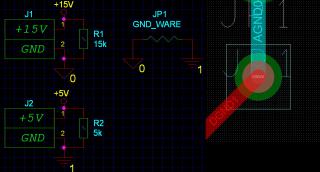

А не сможете вспомнить поточнее, у меня было всё настроено, затем переставил Аллегру и теперь никак не могу вспомнить и найти, что крутил. было вот так...

ЗЫ Просто я любитель и работаю в Cadence не регулярно

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

-

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

Вроде всё на месте.

и как пишут бесплатный:

With the release of CCSv7 all previous v4, v5 and v6 releases are free of charge.На скришноте адрес видно, там всё написано и ссылки есть.

ЗЫ

Чтобы не набирать.

-

а для вырезов в шейпах рисую шейпы на соответствующем слое route keepout - в итоге и редактировать его можно и медь вырезана.

Спасибо за совет!

Попробовал - круто!!!

-

Спасибо!!! Помогло!

Я честно говоря про эту утилиту раньше и не знал.

В вырезах собого смысла и нет. Просто там будут паяться клемники, типа такого:

и у меня как-то было, что под ним подкорачивало. Плата будет самопал без метализации,

по этому топ никак не паяется под ним и соответственно там ничего не надо. Контактную площадку не стал переделывать, просто удалю с топа в гербере.

-

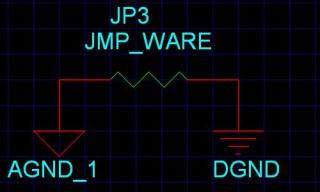

Здравствуйте!!!

На плате имеется две гальванически развязанных земли, которыми заливаются обе стороны.

На одной земле void в заливке вырезается без ошибок, а на другой откуда-то появляется КЗ с тру пинами.

Никак не могу понять, где косяк.

Ну вот собственно и сама плата...

-

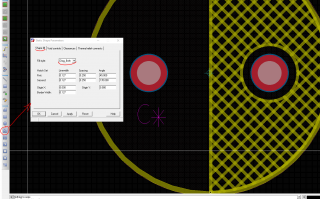

Попробовал!

Нормально всё рпботает. Немного напрягает, что футпринт с ошибкой, которая убирается уже на плате.

Интересно, а если вот так сделать - это корректно?

Попробовал сделать проект, вроде не ругается, типа обманул DRC.

Конечно надо, чтобы на плате было больше одного слоя.

Вроде всё, что надо залил.

-

Посмотрите эту тему https://electronix.ru/forum/index.php?showtopic=132629

Спасибо!

В принципе в статье выше решение тоже самое, что и в обсуждении по ссылке - затыкание пасти DRC-у свойством NET_SHORT(ну или как указал PCBtech свойством NODRC_SYM_SAME_PIN), что бы не мешал, но реализация в статье начинается с Capture, подходит для 17.2. В 16.6 с Capture заморачиваться не надо, а всё делать в редакторах плат и футпринтов, как я понял.

Буду пробовать.

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

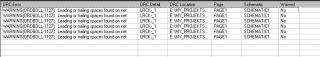

Что-то не получается. Возможно я не правильно понял(с английским не очень).

Вот это место:

On each pin on the net short (SP1) you will need to Edit Property (Double click the pin) and add the net namesthat you wish to short separated by a colon. In this example the nets are DGND:AGND:SGND. It is recommended

that for each pin the primary net is first (i.e. pin 1 the NET_SHORT would equal SGND:AGND:DGND. You also need

to ensure that you also have a PCB footprint defined for the netshort part.

Я так понял в схеме клацаю на пине и в редакторе свойств в Net Name через двоеточие добавляю имя второй земли.

Но он вообще не даёт Net Name редактировать в свойствах пина.

Ещё в примере, как я понял версия 17.2, а у меня 16.6. Может тут собака порылась?

-

В Оркаде делают так: http://www.parallel-systems.co.uk/images/P..._Definition.pdf

Спасибо!

Сижу разбираюсь потихоньку.

-

Опубликовано · Изменено пользователем URIK-ZZZ · Пожаловаться

Здравствуйте!

Подскажите пожалуйста как на практике реализуется такой компонент? Иногда просто избражают резистор с нулевым сопротивлением на схеме,

а как выглядит компонент под это дело?

В голову приходит только нарисовать обычный компонент(например резистор) и вместо него впаять перемычку, но хотелось бы как-то обойтись без пайки.

-

Спасибо!!! Разобрался.

У именя на вкладке Shape fill выскакивало solid, без параметров естественно и я думал, что попал не туда.

-

-

Ну вообще-то DRC, а не DRS, а так похоже где-то в схеме еще есть цепи/порты с таким именем. Прогоняли еще раз проверку DRC после поправок или нет? Потому как Оркад не отслеживает ошибки в схеме онлайн, только пакетная проверка через меню и маркеры висят до следующей проверки.

Да вы правы DRC, проморгал. Проверку я не запускал вообще, я честно говоря и не знал, что такая есть.

Сейчас прочитав ваш пост, поискал, запустил.

Спасибо!!! Помогло. Всё чисто.

Uree, ещё один вопросик, по другой теме.

Вы мне когда-то показывали как рисовать конденсатор, вот этот:

https://electronix.ru/forum/index.php?act=a...st&id=95284

и у меня много позже возник вопрос, как вы изменили шаг штриховки на шейпе?

Никак не могу найти.

-

Здравствуйте!

В конце имени порта был паразитный пробел, по всей видимости случайно зацепил.

Вылезли два DRS маркера.

Пробел в имени удалил но маркеры остались и почему-то в браузере DRS маркеров показывает аж шесть предупреждений.

Хотелось бы от этого избавиться, но что-то ничего не удаётся сделать.

Версия OrCAD Capture16.6-p005(v16-6-112D)

-

Если я правильно понимаю идеологию аллегро, то то, что Вы предлагаете - в корне не верно.

Гербер на то и гербер, чтобы там были слои.

Неужели так сложно сделать слои и сверловку, а потом в каком-нибудь cam-редакторе вывести на печать как надо?

Зачем такие извращения? Ради ускорения процесса?

Я не профессионал в разводке плат.

Для себя платы делал следующим образом:

Разводил в layout, делал гербер, где все слои в одном файле с открытыми центрами.

Открывал в GerbTool и из него печатал только TOP отраженный и BOTTOM прямо. Остальные слои мне были не нужны,

по этому мой опыт работы с гебером никакой, наверно придётся осваивать, но после того как немного освоюсь с Allegro.

Если говорить о "зачем", то я изначально не понимаю, зачем использовать аллегро для плат, которые потом "сверлить вручную". Как-то у меня одно с другим слабо стыкуется...Да, знаю, недвано уже это обсуждалось, но непонимание остается.

Ещё раз я не профессионал в разводке плат считайте, что для меня allegro просто игрушка. Пока делаю одновременно в Layout и Allegro - сравниваю, в allegro пока дольше, но красивее и вообще приятней. Узнал много нового.

До этого несколько раз начинал осваивать allegro, ещё с 15.7 версии, но бросал, не хватало времени и наверное терпения. В этот раз стало что-то получаться, но вот упёрся в герберы.

для лазерно-утюговой технологии:включить нужные слои, распечатать plot сначала в черно-белый pdf для проверки, подобрать цвета в color view, - и потом на принтер.

делать герберы для ЛУТ - это лишнее.

Лут не использую. Мне повезло разжиться плёночным фоторезистом давно просроченный, но 0.3-0.4мм дорожки получаются . По этому с герберов печатаю негативы на плёнке, фоторезист на медь, сверху негатив ну и соответственно затем засвечиваюю. Далее химия по очереди - двууглекислый натрий, хлорное железо, щёлочь натривая или калливая, какая у химиков есть, всё равно, и затем свелить по протравленным точкам.

-

То есть оффициально никак - жаль.

Извиняюсь, если сморозил глупость, я только начал осваивать Allegro.

А может быть можно нарисовать эти точки в допустим в виде шейпов при рисовании компонента, а не на падстеке, и потом как-нибудь в гербер?

А как в CAM350 сделать следующее...

в Разрабатываем ПП в САПР - PCB development

Опубликовано · Пожаловаться

Спасибо огромное. Сработали оба варианта.

На всякий случай, мож кому пригодится: полигон на котором возник артефакт это область свободная от меди разделяющая две гальванически развязанных зоны. Когда я её делал шириной 1мм, проблем не возникало. В этот раз сделал 2мм, получил артефакт. Статистики нет, но факт имеет место быть.