valerony

-

Постов

20 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные valerony

-

-

4 hours ago, Aner said:

Поясните что будете проверять, тестить в этой функциональной проверке для DDR3?

хотелось бы записывать/считывать данные в блоках памяти (ее наличие как таковой и способность запоминать ))...), как написал aaarrr, можно выключить режим DLL, тогда частоту можно снижать, вплоть до частоты обновления. Пока буду пробовать на CycloneIII, надеюсь что-нибудь получится...

-

6 minutes ago, aaarrr said:

А в чем смысл? Не хватает быстродействия - так есть SDR, DDR, DDR2. Зачем именно 3?

Если бы это было для конкретного проекта, то я бы естественно поставил хоть SRAM, но стоит задача в функциональной проверке именно DDR3

-

50 minutes ago, Aner said:

Это врядли, да и не нужно оно. В JEDEC спецификации все расписано - это же целый большой автомат с кучей настроек, подстроек и тд, одна его часть аппаратная в DDR3, другая должна быть чипе FPGA, SoC и тп. В CycloneIII нет этой второй части модуля аппаратной поддерки DDR3. Почему не получится реализовать - недостаточно ресурсов. Ну и посмотрите с каких минимальных частот работают DDR3, 50МГц это далеко не то что нужно.

Спасибо за ответ. Т.е. минимальная работа DDR3 на частоте 300МГц. У меня задача состоит в том, чтобы хоть как-то проверить функциональность этой памяти. Поддерживаются DDR3 начиная с CycloneV, отладочные платы с ними есть, но там выведены только GPIO, и память туда не подключить. Придется делать свою многослойную печатную плату, паять BGA корпус...

-

Товарищи, у меня тоже вопрос по DDR3. Можно ли запустить работу DDR3 памяти на CycloneIII, хотя бы на пониженной частоте, например 50МГц? В квартусе контроллеры DDR3 для 3-го циклона не доступны, и вопрос как раз в том, по какой причине. Или это физически невозможно, или просто 3-й циклон не тянет те частоты, тогда контроллер можно написать самому, хотя бы для запуска памяти на низкой частоте.

-

Все, разобрался... необходимо чтобы в системе (в диспетчере устройств) был хотя бы 1 COM порт, иначе программа не обнаружив ни одного COM порта выдает такую ошибку.

После подключения программатора работающего по виртуальному COM порту, все заработало

-

Опубликовано · Изменено пользователем valerony · Пожаловаться

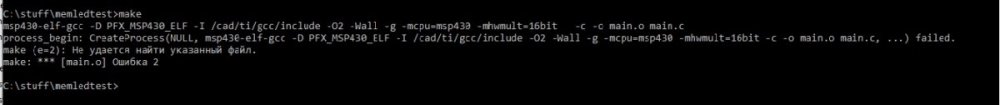

Помогите понять в чем может быть проблема, на некоторых ПК openmsp430-minidebug.tcl запускается без проблем, на других выходит ошибка:

Точнее пробовал на двух ПК (на каких была возмножность) на работе, все запускается, даже непосредственно с флешки (Windows8, Windows10). А дома на нетбуке (Windows7), и на ПК (Windows10) выходит такая ошибка, как будто проблема с портами uart...

-

Опубликовано · Изменено пользователем valerony · Пожаловаться

Все! получилось запустить! Пишу и запускаю команды на компиляцию в notepad++, загружаю и отлаживаю в minidebuger. Оказалось можно обойтись и без MinGW, я использовал make от AVR Studio4 который был установлен, наверняка можно и от какого либо другого тулчейна на gcc. В планах переделать "под себя" rtl, сделать несколько версий: полную, среднюю, и минимальную. Возможно получится его уменьшить в размере, впереди много интересного...

-

В intrinsics.h написано

/* Insert an eint instruction. This enables maskable interrupts, such as those from peripheral devices. */ void __eint (void);т.е. нужно написать эту функцию самому. Странно что они сами ее не написали, вроде для всех msp430 она должна быть одинаковой.

-

On 4/24/2019 at 2:18 PM, valerony said:

in430.h

in430.h присутствует в старых компиляторах, в некоторых он заменяется intrinsics.h, в общем с этим понятно, но теперь компилятор не понимает функцию __eint() , т.е. непонятно то ли файла не хватает, то ли в ручную прописывать что-то нужно

-

Когда запускаю компиляцию утилитой make, сообщает что отсутствует файл in430.h

И действительно, такого файла нигде нет ни в компиляторе mspgcc, ни в RedHat версии. Подскажите какой компилятор взять?

-

20 minutes ago, dvlwork said:

Скорее всего это глобальные буферы от Altera. После них сигнал выходит на глобальное дерево. Легко можно заменить на assign

Спасибо, похоже на то... Я в своем проекте просто их закомментировал, и вообще модуль pll не включил. Похоже это для увеличения "fanout". Короче проект с имеющимся .mif с мигающим портом работает. Огромное спасибо автору особенно за этот mif т.к. позволил оценить функциональность.

По поводу makefile разбираюсь..., пока нашел литературу по утилите make, как с ней работать и в таком духе...

-

Остановился на этапе конвертирования в формат mif. Поставил MinGW, mspgcc отсюда: https://sourceforge.net/projects/mspgcc/files/latest/download, прописал в переменную Path расположение их /bin (от MinGW и mspgcc).

В командной строке захожу в папку с проектом memledtest, ввожу "make" и получаю ошибку:

MinGW вроде как отдельно работает- компилирует. Может mspgcc не подходит, (не подходящая версия), хотя пробовал и другие, и такой же результат был. Или в MinGW не хватает какого-то пакета, в чем может быть проблема? Что необходимо устанавливать в MinGW чтобы было достаточно для нормальной работы?

-

Помогите разобраться пожалуйста. В файле OpenMSP430_fpga.v две строчки:

global gbuf_clk_sys (.in( oc25m ), .out( clk_sys ) ); global gbuf_reset_n (.in( ~oRst ), .out( reset_n ) );Выглядит как установка двух экзепляров модулей "global", но таких модулей в проекте я не нашел. Кто подскажет может это какие-то стандартные блоки veriloga типа "and"? Где можно увидеть их описание?

-

Спасибо, теперь понятно, не внимательно смотрел )

-

Здравствуйте, в файле в исходниках от openmsp430 - omsp_gpio.v есть следующее:

// Register base address (must be aligned to decoder bit width) parameter [14:0] BASE_ADDR = 15'h0000; // Decoder bit width (defines how many bits are considered for address decoding) parameter DEC_WD = 6; // Register addresses offset parameter [DEC_WD-1:0] P1IN = 'h20, // Port 1 P1OUT = 'h21, P1DIR = 'h22, P1IFG = 'h23, P1IES = 'h24, P1IE = 'h25, P1SEL = 'h26, P2IN = 'h28, // Port 2 P2OUT = 'h29, P2DIR = 'h2A, P2IFG = 'h2B, P2IES = 'h2C, P2IE = 'h2D, P2SEL = 'h2E, P3IN = 'h18, // Port 3 P3OUT = 'h19, P3DIR = 'h1A, P3SEL = 'h1B, P4IN = 'h1C, // Port 4 P4OUT = 'h1D, P4DIR = 'h1E, P4SEL = 'h1F, P5IN = 'h30, // Port 5 P5OUT = 'h31, P5DIR = 'h32, P5SEL = 'h33, P6IN = 'h34, // Port 6 P6OUT = 'h35, P6DIR = 'h36, P6SEL = 'h37; // Register one-hot decoder utilities parameter DEC_SZ = (1 << DEC_WD); parameter [DEC_SZ-1:0] BASE_REG = {{DEC_SZ-1{1'b0}}, 1'b1}; // Register one-hot decoder parameter [DEC_SZ-1:0] P1IN_D = (BASE_REG << P1IN), // Port 1 P1OUT_D = (BASE_REG << P1OUT), P1DIR_D = (BASE_REG << P1DIR), P1IFG_D = (BASE_REG << P1IFG), P1IES_D = (BASE_REG << P1IES), P1IE_D = (BASE_REG << P1IE), P1SEL_D = (BASE_REG << P1SEL), P2IN_D = (BASE_REG << P2IN), // Port 2 P2OUT_D = (BASE_REG << P2OUT), P2DIR_D = (BASE_REG << P2DIR), P2IFG_D = (BASE_REG << P2IFG), P2IES_D = (BASE_REG << P2IES), P2IE_D = (BASE_REG << P2IE), P2SEL_D = (BASE_REG << P2SEL), P3IN_D = (BASE_REG << P3IN), // Port 3 P3OUT_D = (BASE_REG << P3OUT), P3DIR_D = (BASE_REG << P3DIR), P3SEL_D = (BASE_REG << P3SEL), P4IN_D = (BASE_REG << P4IN), // Port 4 P4OUT_D = (BASE_REG << P4OUT), P4DIR_D = (BASE_REG << P4DIR), P4SEL_D = (BASE_REG << P4SEL), P5IN_D = (BASE_REG << P5IN), // Port 5 P5OUT_D = (BASE_REG << P5OUT), P5DIR_D = (BASE_REG << P5DIR), P5SEL_D = (BASE_REG << P5SEL), P6IN_D = (BASE_REG << P6IN), // Port 6 P6OUT_D = (BASE_REG << P6OUT), P6DIR_D = (BASE_REG << P6DIR), P6SEL_D = (BASE_REG << P6SEL);т.е. 6-битной шине P1IN_D присваивается BASE_REG смещенный влево на 32:

parameter [DEC_SZ-1:0] P1IN_D = (BASE_REG << P1IN)

Помогите разобраться как такое может быть в чем смысл такого смещения?

-

BSP посмотрите (bsp/drivers/inc), для каждого ядра есть соответствующие макросы, типа IOWR_ALTERA_AVALON_PIO_SET/CLEAR_BITS()

Спасибо большое, определенно по ядру JTAG UART регистров установки/очистки я не нашел, зато в altera_avalon_pio_regs.h есть макросы установки/очистки бит, я так понял это универсальные макросы:

IOWR_ALTERA_AVALON_PIO_SET_BITS(base, data)

тогда чтобы установить младший бит в регистре control

IOWR_ALTERA_AVALON_PIO_SET_BITS(адрес control, 0x00000001)

Будет время попробую

В догонку - при создании PIO нужно разрешить побитовое управление.Да, по поводы портов ввода/вывода знаю, меня больше интересуют регистры например JTAG UART, там как таковых отдельных регистров установки бит нет, и нет галочек по их включению в модуль

-

Ребята, кто знает как правильно делать установку/очистку отдельного бита в регистре. Например в ядре JTAG UART регистр control содержит биты AC, WE, RE, и нужно установить WE, RE не "трогая" AC.

У AVR это можно было сделать накладывая маску, в NIOS обращение к регистрам идет с помощью макросов IORD(...), IOWR(...), т.е. способ в "лоб" это:

1-завести переменную в 32 бита (temp)

2-провести IORD(...) регистра control в переменную temp

3-провести IOWR(...) переменной temp с маской в регистр control

Есть ли более быстрый способ устанавливать биты отдельно? Я уже листал юзер гайды и мануалы, но почему-то примеров на C так и не нашел :(

-

На fpgacpu.org есть исходники на verilog и хорошее описание процессора xr16, а самое главное С компилятор. По характеристикам очень понравился, продуманной системой команд и малым размером. Автор писал что собирал xr16 под старую модель Xilinx (для альтер рекомендовал ниос, но ниоса для ACEX уже нет). Пробовал кто-нибудь собрать его на Altera ACEX или Cyclone? Нужно ли при этом редактировать сам компилятор?

-

если вам без разницы ядро почему бы не взять xsoc16 http://www.fpgacpu.org/ проект давно вылизан, есть си компилятор. При этом проц затачивался под фпга

Здесь на форуме https://www.embeddedrelated.com/showthread/...-cpu/1381-1.php автор пишет что данный проц затачивался под Xilinx семейство XC4000E, и не рекомендует использовать его в альтерах. Пробовал кто-нибудь запускать их в циклонах например?

NIOS для начинающих

в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Опубликовано · Пожаловаться

помогите с вопросом по созданию собственных компонентов в Qsys, а именно:

как указать конкретный путь сохранения итоговой оболочки- файла _hw.tcl? проблема в том что имея готовые файлы описания-HDL, запуская Quartus без открытия проекта, и запустив там Qsys (для создания компонента) он без ведома установит по пути c:/altera, а мне нужно как положено в папку ip (как и все остальные компоненты лежат). Если оставить так получится неразбериха, плюс могут возникнуть проблемы с использованием данного компонента, т.к. Qsys его не обнаружит.

Единственный выход который на данный момент я нашел, это для будущего компонента в нужной папке специально собирать проект для данного модуля, и только тогда _hw.tcl файл сохранится в нужной папке.

Может быть есть какой то более правильный и легкий способ добавления собственного компонента?