Suicide

Участник-

Постов

18 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Suicide

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

Доброго времени суток, форумчане! Прошу подсказки. Генерируем ядро передатчика Jesd204B TX в Vivado: - 1 линия - 1 фрейм 17 октетов = мультифрейм Формируется Example Design, в тестбенче которого все равно всё написано для дефолтных настроек типа 2 октета 32 фрейма. Но это ладно, само ядро то формируется как положено, а тестбенч правится руками. Период SYSREF 68 клоков (длина мультифрейма * 4 - так в тестбенче подсказывают в комментарии). Запускаем в Questa Sim, добавляем блок tx, и внутри самого блока получается, на линии данных, конфигурация начинается с 4 октета. Должно быть типа "1c 01 02 03 04 05 06 07 08 09 ... 7c", а по факту после запятых (BC которые), конфигурация появляется вот так "04 05 06 07 08 09 ... 7с". Скорее всего я что-то недоправил в тестбенче. Никто не сталкивался с такой проблемой? Нет ли у кого-то случайно лишнего часа времени сгенерить и попробовать? Простите что скринов не добавляю, под рукой нет сейчас, а информация нужна. Если нужна какая-то еще инфа о происходящем, скажите, дополню. Если что большое спасибо сразу!

-

Спасибо! Сейчас ознакомлюсь. Вот как раз прикол в том, что у моего и альтеровского энкодера RD совпадают, а альтеровский энкодер иногда зачем-то инвертирует код. Я вот и не могу понять этот механизм, зачем он это делает. У меня просто LUT из которого выдирается код соответствующий текущему RD, а вот альтеровский зачем-то еще в некоторых случаях инвертирует. Для меня за недостатком опыта и информации, пока что это загадка.

-

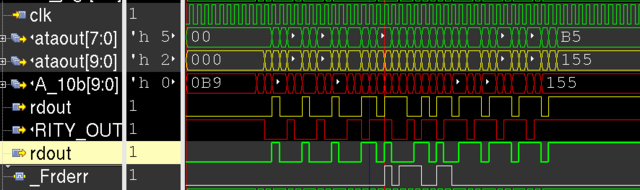

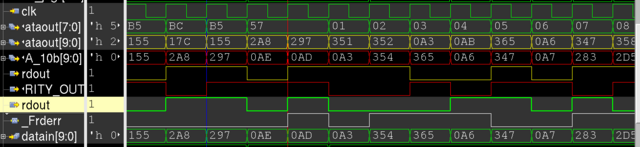

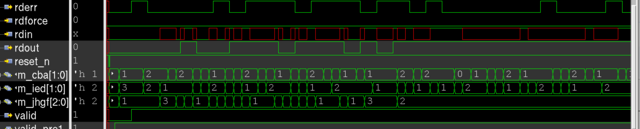

Большое спасибо! Я подключил свой энкодер в этом тестбенче, и всё стало почти хорошо. На представленных изображениях, сигналы моего энкодера обозначены красным цветом, энкодера из тестбенча желтым цветом, а декодера зеленым цветом. Running disparity (далее RD) у моего энкодера и энкодера из тестбенча совпадают, НО! есть нюанс. Когда в тестбенче подряд передаются символы 1,2,3 и т.д., декодер выплёвывает ошибки Frderr. После изучения временных диаграм, я заметил что после символов 2A8. 297, энкодер из тестбенча начинает выдавать символы противоположного RD, нежели у моего энкодера (при этом RD по сути совпадает). Вероятно это происходит здесь - Но я не до конца понимаю механику выбора кода таким образом. Почему при совпадающем RD код получается разным на каком-то участке (где 1,2,3 и т.д)? Причем дальше всё снова становится нормально. Ознакомление вот с этим документом - https://www.intel.com/programmable/technical-pdfs/654488.pdf - ничего к сожалению не дало(

-

Что-то я походу конкретно не так делаю, а у вас случайно нет тестбенча где вот эти энкодер и декодер друг друга вкручены? Я подключаю напрямую, а у меня чушь какая-то, как будто что-то отрабатывать не успевает. Буду благодарен за тб или подсказку.

-

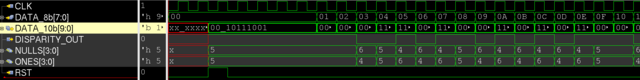

Здравствуйте еще раз! Если не затруднит, взгляните пожалуйста на временную диаграмму энкодера моего. CLK - клок; DATA_8b - входные 8 битные слова; DATA_10b - кодированные слова; DISPARITY_OUT - соответственно текущий running disparity; NULLS/ONES - количество нулей и единиц в текущем 10-битном слове; RST - ресет. Есть ощущение что всё правильно, но может running disparity должен быть сдвинут вперед или вроде того?

-

А нет, пардон, кажется я рано радуюсь

-

Большое спасибо за замечание! Вы оказались правы! Декодер в приложении я пересадил на клок (он по умолчанию срабатывал на любое изменение входного сигнала), и завел в него клок который в 2 раза медленнее того которым тактируется энкодер. В итоге фронт стал приходиться на середину каждого слова в потоке, и все ошибки пропали, при том что декодер верно показывает на своем выходе то, что собственно было на входе энкодера. Спасибо еще раз! Отсюда буду думать, и анализировать, как это по итогу должно будет выглядеть.

-

Диспаритет -1 да. У меня вот тотал диспаритет мелькает 1,3 где ошибка, тогда видимо что-то там страшное происходит. Пойду разбираться, спасибо)

-

Здравствуйте! Не могу до конца понять как работает disparity_error в 8b10b декодере во вложении, достался в наследство откуда-то из интернета вроде. Ошибка привязана к выходу out_disperr. В тестбенче подключено так - jesd204_8b10b_decoder i_dec (.in_char(DATA_10b),.in_disparity(disp),.out_disparity(disp),.out_char(OUT_CHAR)); Энкодер который я туда подсовываю на длинной дистанции выдает 50% нулей и 50% единиц, коды правильные, в энкодер прям таблица зашита с ними, а выход out_disperr дрыгается туда сюда там где 0 и 1 соответственно 6 и 4, или 4 и 6, и total_disparity показывает 1 и 3. Буду благодарен, если кто-нибудь подскажет, потому что для меня сейчас не совсем понятно как понять наличие ошибки, должно ли в total_disparity всегда быть 0 или 2. jesd204_8b10b_decoder.v

-

Спасибо! Буду ознакамливаться. Я вот еще немного не понял, как распространяется сигнал SYSREF к приёмнику и передатчику, если они располагаются на разных устройствах. Есть вероятность что вопрос глупый, тапками не бейте сильно, пожалуйста.

-

Здравствуйте! Чирикаю ручкам JESD204B. Осилил энкодер сделать 8b10b, пока завис на этапе синхронизации, ILAS и т.д. В частности пытаюсь понять концепцию LMFC. В JESD204B Survival Guide написано что эта штука просто считает бесконечно до числа равного "Кол-ву октетов на фрейм Х На Кол-во фреймов в мультифрейме - 1.". Сигнал SYSREF ресетит все LMFC как в передатчике, так и в приёмнике, за счёт чего клоки во всей системе оказываются выровнены. Где я немного залип и зациклился, это в понимании как и где формируется Frame Clock, прямо в LMFC тупо счётчиком? Не могу найти временных диаграмм с пояснениями как в JESD204B клоки расфасованы и как LMFC работает. В гугле не забанили, имею JESD204B Survival Guide, стандарт JEDEC, почитанные но не совсем понятые. Отсюда и вопросы полезли. Помогите пожалуйста дураку кто чем сможет!

-

Про ядра интересно, надо поискать! Да) цифра) Всем огромное спасибо что откликнулись! Перевариваю пока информацию

-

Здравствуйте уважаемые форумчане! Изучаю систему Cadence, в частности NC-Verilog и Genus Синтезирую под библиотеку Silterra 180nm CL180G Вот модуль 8-бит умножителя, который хорошо работает на частоте 130 Mhz module multik (clk, A, B, out, reset); input clk; input reset; input [7:0] A; input [7:0] B; output [15:0] out; reg [7:0] Ar,Br; reg [15:0] out_r; reg [7:0] helpers16 [40:0]; reg [15:0] helpers31 [40:0]; integer i; always @ (posedge clk) begin Ar<=A; Br<=B; helpers31[0]<=Ar*Br; for(i=1; i<10; i=i+1) helpers31 [i] <= helpers31[i-1]; end assign out=helpers31[i-1]; endmodule Вот код умножителя на 16-бит, который "захлебывается", т.е. периодически показывает неверные значения на частоте 130 Mhz. Во вложении скрин, там где желтые значения. module multik (clk, A, B, out, reset); input clk; input reset; input [15:0] A; input [15:0] B; output [31:0] out; reg [15:0] Ar,Br; reg [31:0] out_r; reg [15:0] helpers16 [40:0]; reg [31:0] helpers31 [40:0]; integer i; always @ (posedge clk) begin Ar<=A; Br<=B; helpers31[0]<=Ar*Br; for(i=1; i<10; i=i+1) helpers31 [i] <= helpers31[i-1]; end assign out=helpers31[i-1]; endmodule Пробовал retime -prepare retime -min_delay в надежде что генус раскидает регистры, и все заработает, но не вышло. Отсюда возникает 2 вопроса - какая существует тактика для перемножения больших чисел на больших частотах? - как пользоваться командой генуса - retime? Заранее спасибо за любые рекомендации!

-

XAUI - помогите найти схему

Suicide ответил Suicide тема в В помощь начинающему

Подскажите - FIFO для XAUI нужен сингл-клоковый, или с разными клоками? -

XAUI - помогите найти схему

Suicide ответил Suicide тема в В помощь начинающему

Можно ли рассмотреть что в принципе входит в XAUI? Допустим - FIFO, конвертер параллельно-последовательный и т.д.