-

Постов

304 -

Зарегистрирован

-

Посещение

-

Quartus оптимизация

КонстантинТ опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день, есть проект на Verilog, SDRх2 применики + Bandscope x 2 Версия quartus - 15.1 FPGA - Cyclone IV Занято почти 94% кристалла. Добавил еще один небольшой блок, заняло почти 99% Теперь после компиляции, то один .то другой SDR перестает работать. Можно, как нибудь в квартусе запретить оптимизацию отдельных блоков? -

Спасибо, это оно! Однажды уже так делал на 7.9.4. вспомнил

-

-

Пока схема схемотехник+тополог. Какой лучше вариант обмена использовать? Спасибо заранее. По идее, если разместить на расшаренном диске (посредством Дропбокса), то на той стороне проект откроется в Read only только, если на другой машине его открыли для работы

-

Я пробовал переносить архивы проектов с одной на другую машину, ICDB ругается но потом открывает проект, потерь еще не было. Разговаривал с коллегами, у них проекты тоже шарились на сетевых папках, RSCM поднят не был, ICDB - не ругался. По RSCM - банальная нехватка времени. У вас был опыт проброса RSСM через инет? Сколько портов надо открывать, только двух достаточно - как в руководстве? Может проще VPN поднять? Какая скорость? Когда то пробовали EDM по инету (в 7.9.4) - скорость синхронизации была очень низкой.

-

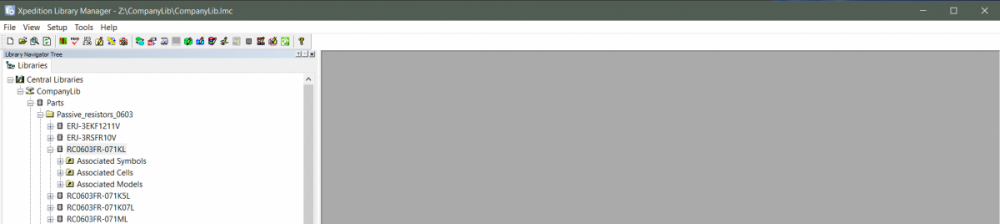

Добрый день, возникла необходимость настройки удаленной работы двух сотрудников (не используя EDM), не находящихся в локальной сети и имеющих выход в инет. На обоих местах есть Дропбокс. Начали с размещения библиотек по одному пути в системе: 1. Расшарили папку в дропбоксе с центральной либой на оба аккаунта дропбокса 2. Расшарили на каждой машине дропбоксовскую папку по сети и подключили ее как сетевую папку. Lib manager открыл и позволяет с либо работать. На обоих машинах либа находится по одному пути 3. Расположили проекты на обоих машинах по одному пути C:/Mentor/Company/xxx 4. В настройках проекта указали путь к центральной библиотеке Z:\CompanyLib\xxx Вроде бы работает (тьфу-тьфу). Покритикуйте такой подход? Какие подводные камни? Как лучше синхронизировать проекты - просто шарить архивы и копировать на компе в свою рабочую папку?

-

Спасибо, но по ссылке ничего нет. Не могли бы прикрепить в аттаче, если не сложно?

-

Никто не сможет поделиться не подписанным драйвером для sau510usb iso plus Windows 10. На сайте архива нет :-( Заранее спасибо

-

- У меня нет никаких претензий к ксайлинксу - Мне достаточно CLG400 корпуса, о чем и указал в названии темы - Не думаю, чтобы они создавали библиотечный символ с нуля, как обычно - передрали с оригинальной схемы. Если плата работает и продается- в чем могут быть претензии? - Обязательно посмотрю, но позже. Пока схем в PDF достаточно

-

Ошибка в названии темы, уже исправил. Нужны 7000, двухъядерные. 010 и 020 pin-to-pin. В приведенном архиве есть оркадовская либа, уже создал компонент под VX2 Можно двигаться дальше. Хотелось бы уйти на шесть слоев вместо восьми.

-

Вот кое что нашел https://rwth-aachen.sciebo.de/index.php/s/MCzrMyyzyvRlRce

-

Добрый день, решил спроектировать свою плату на этом процессоре. Попытался скачать оригинальны схемы китов с официального сайта. Зарегистрировался - облом, ксайлинкс не дает скачивать эти файлы из-за экспортных ограничений. Может у кого есть в формате DSN (оркад) или где можно скачать. Хотя бы символы чипа сконвертил в свою библиотеку.

-

Заметил, что это проиcходит с компонентом после того, когда в локальной ЦБ отредактировал и поменял padstack Нашел workaround - ECO replace cell на другой и обратно. Вроде бы помогло

-

Отправил в личку

-

Добрый день, Делаю большой проект на VX2.2 (8 слоеd HDI) Возникал такая проблема (впервые): 1. Делаю Replace Component в схеме - меняю 0402 на 0201 резистор (RefDesign сохраняю) 2. В Xpedition Layout компонент меняется на 0201 - все правильно 3. Пытаюсь перенести компонент на другой слой (F5) 4. Получаю ошибку "Push component failed" Раньше, на небольших проектах такого не было