files

Участник-

Постов

21 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о files

-

Звание

Участник

Посетители профиля

957 просмотров профиля

-

Спасибо за ответы. Хорошо, регистр, настраивающий LUT, является частью конфигурационной памяти. А как, собственно, организована конфигурационная память? По адресному принципу или она представляет собой сдвиговый регистр?

-

Всем добрый день. Возвращаясь к первоначальному вопросу темы. Меня интересует, как устроена конфигурационная память FPGA. Толком никаких подробностей найти не получается (по крайней мере, в документации Altera). Простой вопрос. Вот, например, 4-входовой LUT конфигурируется 16-разрядным двоичным словом на выполнение конкретной функции. Где хранится это слово? Реально в структуре FPGA существует 16-разрядный регистр, хранящий эти 16 разрядов и закрепленный за конкретным LUT-ом? Этот регистр, это часть конфигурационной памяти? Или этот регистр отделен от конфиг. памяти, и значения копируются в него в процессе конфигурирования из конфиг. памяти? Спасибо за ответы?

-

Спасибо за ответы. Я всегда считал (поправьте, если это не так), что конфигурационная память в FPGA устроена вроде длинного сдвигового регистра, в который вдвигается битрстрим. Если это так, то как физически возможно прочитать битстрим из этого регистра не останавливая устройство?

-

Всем добрый день. Возник такой вопрос. Можно ли в принципе считать из FPGA конфигурационный код (bitstream) в процессе работы устройства? Именно в процессе работы, не останавливая функционирование устройства. Спасибо за ответы.

-

Fmax и Restricted Fmax в Quartus

files опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте, уважаемые специалисты по нюансам работы Quartus-а. Quartus оценивает максимальную частоту для проекта в виде двух величин Fmax и Restricted Fmax. Для некоторых проектов эти величины близки, а для некоторых различаются в разы. Посмотрел документацию Altera, почитал альтеровский форум. И там и там есть объяснение, в чем разница между этими величинами. Но все эти объяснения уж очень невнятные и непонятные. Уважаемые знатоки Quartus-а, может кто-нибудь нормально / доступно объяснить разницу между Fmax и Restricted Fmax? В каких случаях какую из этих величин следует использовать для оценки скоростных характеристик проекта? -

Имеют ли FPGA функцию throttling?

files опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Мне недавно показали один странный эксперимент на Altera Cyclone II. Там довольно простая схема – 8-разрядный накапливающий умножитель. Схема тактируется от внешнего генератора 50MHz, частота которого умножается на PLL. Так вот если держать частоту тактирования в допустимых приделах (до 250 MHz), то схема работает без ошибок. Если же начинать увеличивать частоту тактирования выше допустимой (оговоренной в документации микросхемы), то схема, естественно, начинает давать ошибочные результаты. Но, если поднять частоту выше определенного порога, схема перестает сбоить и снова начинает считать правильные результаты. Выглядит это примерно так: 0….250 MHz – правильные результаты 251…800 MHz – неправильные результаты больше 800 MHz – снова правильные результаты В связи с этим возникает вопрос, как объяснить такое явление? Нет ли у FPGA функции throttling (душения, дросселированния) сигнала тактирования? Возможно ли, что при повышении частоты тактирования схемы выше некоторого порога, FPGA сама опускает частоту до нормативного значения и из-за этого схема начинает считать корректно? -

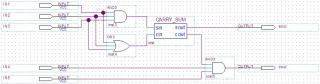

Как я опции не крутил, все равно при синтезе этой схемы выдает сообщение «Ignored 1 CARRY_SUM primitive» и Quartus 13.0 и Quartus 8.1. Может, у кого есть мысли, что не так?

-

Спасибо за комментарий. Я вот сделал такую примитивную схему. Ожидалось, что: – верхний элемент И (inst3) и элемент ИЛИ (inst4) упакуются в один LUT элемента, находящегося в арифметическом режиме; – второй элемент И (inst5) примет данные из этого LUT-а через цепь переноса; – всего для реализации этой схемы будет задействовано 2 LUT-а. У меня были правильные ожидания относительно этой схемы, или я что-то делаю не так? Реально же схема размещается в 3-х LE (каждый логический элемент в отдельном LUT), все LE в нормальном режиме, цепь переноса не задействована. Среда разработки – Quartus 13.0. Опции игнорирования CARRY вроде нет

-

Огромное спасибо за комментарии. Однако относительно примитива CARRY_SUM не все понятно. Я правильно понимаю принцип работы этого примитива: сигналы, которые я подаю на входы sin, cin разведуться на выходы суммы и переноса логического элемента LE FPGA? У меня такой разводки при помощи примитива CARRY_SUM добиться не удалось. Оба выхода LUT-а подключаются к выходам суммы, а цепь переноса оказывается не задействована. Или я неправильно понял, как работает примитив?

-

FPGA Altera Cyclone до 4-го поколения включительно имеют в составе LE 4-входовой LUT. В арифметическом режиме этот LUT фактически интерпретируется как два 3-входовых LUT-а, один из которых реализует функцию суммирования, а другой переноса. Причем оба эти 3-входовых LUT-а имеют каждый свой отдельный выход. Вопрос к знающим людям: есть ли возможность реализовать на арифметической конфигурации LE (с двумя 3-входовыми LUT-ами) две произвольные логические функции от трех общих переменных?

-

Емкость конденсатора ячейки DDR SDRAM

files опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Ячейка динамической памяти построены на основе конденсатора и полевого транзистора. Очень нужно узнать, хотя бы приблизительно: - какова емкость конденсатора ячейки современной оперативной памяти (например, DDR3 SDRAM)? - каково сопротивление сток-исток полевого транзистора такой ячейки? Нигде не могу найти эту информацию. Может, кто может дать ссылку, где посмотреть -

Решил, что для быстрого решения моей задачи (считывание и модификация значений LUT Mask) наиболее подходит первый способ рекомендованный jks: Однако, не могу разобраться с TCL командами Quartus Chip Planner: http://quartushelp.altera.com/current/merg...ner_ver_2.0.htm Да, есть команда get_node_info, позволяющая получить LUT Mask. Есть команда set_node_info, позволяющая установить LUT Mask. Но как мне позиционироваться на нужные мне LUT-ы? Единственная команда, которая содержит параметр location, это команда add_new_cell. С ее помощью я могу создать новую ячейку и при этом задать ее координаты в FPGA, после чего применять к ячейке get_node_info и set_node_info. Но как мне спозиционироватся (задать location) на уже существующую ячейку? Чтобы для нее применить команды get_node_info и set_node_info. Помогите. Все альтеровские рекомендации перерыл. Примеры, которые дал jks тоже не дают нужного результата. Не могу найти ответа

-

Спасибо всем, кто написал советы. Буду пытаться пробовать этот способ. Этот вариант мне приходил в голову. Но для его реализации нужно знать формат POF/SOF файлов. Насколько мне известно, Альтера не афиширует эти форматы. Мне не удалось их найти. jks, Вы не знаете где их можно посмотреть?

-

Неужели невозможно? Вручную можно менять содержимое LUT, а программно нельзя? Мне нужно по уже готовым проектам пройтись, там логика уже в LUT-ах.

-

Вопрос знатокам тонкостей Quartus-а Через Resource Property Editor, который вызывается из Chip Planer можно просмотреть логическое уравнение LUT (SUM/Carry Equation) и соответствующую этому уравнению LUT Mask. В этом же редакторе имеется возможность изменять уравнение или маску. Короче, можно просматривать и менять содержимое LUT-ов. Мне нужно проделать аналогичную процедуру (считывание / изменение LUT Mask) но не вручную. Моя программа должна пройтись по проекту, считать LUT-маски и по определенному принципу изменить их. Вопрос: может, кто знает, где Quartus хранит LUT-маски или как получить к ним доступ?