Поиск

Показаны результаты для тегов 'qpsk'.

-

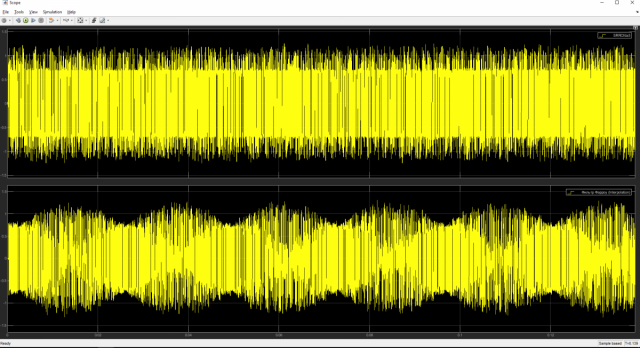

Опишу проблему Как понятно из заголовка пытаюсь сделать символьную синхронизацию для QPSK системы Основываясь на информации из книги "Michael Rice - Digital Communications: A Discrete-Time Approach", символьную синхронизацию делал по принципу: 1) Interpolator - Piecewise структура фильтра Фарроу 2) Timing Error Detector - Детектор Гарднера 3) Loop Filter 4) Interpolation Control - структура "Modulo-1 Counter" В чем проблема ? Проблема в том, что система символьной синхронизации одновременно работает и нет, то есть периодически повторяется следующий процесс: 1) Система находит оптимальный момент выборки (максимального раскрытия глазка) 2) Система теряет оптимальный момент выборки На осциллограмме input и output фильтра Фарроу наблюдается картина как на скриншоте ниже

-

Отклик SRRC в QPSK демодуляторе

Zalman_ опубликовал тема в Алгоритмы ЦОС (DSP)

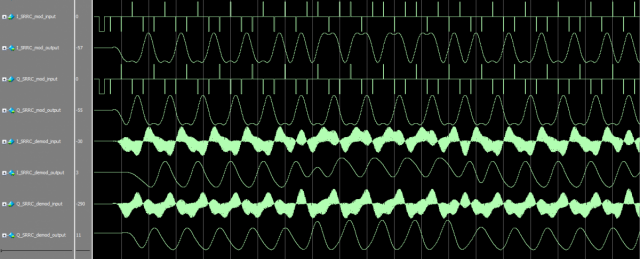

Добрый день, столкнулся с такой проблемой. Делаю демодулятор QPSK на FPGA Есть QPSK модулятор и соответственно QPSK демодулятор. В модуляторе используется SRRC, что автоматически добавляет такой же SRRC на сторону приемника. В процессе модуляции все происходит корректно и передается на приемник. Замечу, что так как проект сделан на ПЛИС (на данный момент только в коде, то как таковой задержки в чем-либо между модулятором и демодулятором нет). Также отмечу, что SRRC, NCO и частоты идентичны друг другу. По идее, на приемной стороне с выхода SRRC на синфазной и на квадратурной составляющей я должен видеть примерно ту же "картину", что и на выходе SRRC, который стоит в модуляторе. Однако при идентичности параметров и фильтров на приемной стороне SRRC выдает специфичный сигнал, который вроде бы и похож, но тем не менее не соответствует сигналу, получаемому из SRRC в модуляторе. Скрин приложил Скрин из программы ModelSim На скрине входы и выходы SRRC на I и Q в модуляторе и демодуляторе.