ezk13

Участник-

Постов

25 -

Зарегистрирован

-

Посещение

Весь контент ezk13

-

Добрый день! Подскажите, уже голову сломал не могу найти где косяк: Есть плата US+, на PL-части по AXI-Stream передаются пакеты от 16 Б до 96 Б в DataMover (DM настроен на бёрст 16Б, при шине 128 бит) далее, через интерконнект шина идёт на S_AXI_HPC0_FPD и затем на PS-DDR. На baremetal PS-части по прерыванию пытаюсь писать данные из DDR в буфер: for (uint32_t valid_addr = last_addr; valid_addr < next_addr; valid_addr += 8) { payload[it] = Xil_In64(PS_DDR_BASEADDR + valid_addr); it++; } Пытался перед записью в буфер инвалидировать кэш, разными способами: Xil_DCacheInvalidateRange((UINTPTR)cacheline_addr, cacheline_len); Результат один - после N-го количества запросов виснет цинк в Xil_SyncAbortHandler() Но, при этом данные идут корректные, пока не зависнет. Комментировал код выше и оно всё равно зависает т.е. похоже дело в какой-то рассинхронизации. Что делал ещё: Активировал в DataMover кэши (AxCACHE, AxUSER) и пробросил их в цинк: /* Setting up caches for DataMover * AxCACHE[3:0] Attribute * ------------------------------------------------------------------------------------------- * | WA | RA | C | B | Description | Comments * |----|----|---|---|------------------------------------------------------------------------ * | 0 | 0 | 0 | 0 | Non-cacheable, non-bufferable | 0x0 , * | 0 | 0 | 0 | 1 | Bufferable only | 0x1 , * | 0 | 0 | 1 | 0 | Cacheable but do not allocate | 0x2 , * | 0 | 0 | 1 | 1 | Cacheable and bufferable, do not allocate | 0x3 , * | 0 | 1 | 1 | 0 | Cacheable write-through, allocate on read | 0x6 , * | 0 | 1 | 1 | 1 | Cacheable write-back, allocate on read | 0x7 , * | 1 | 0 | 1 | 0 | Cacheable write-through, allocate on write | 0xA , * | 1 | 0 | 1 | 1 | Cacheable write-back, allocate on write | 0xB , * | 1 | 1 | 1 | 0 | Cacheable write-through, allocate on both read and write | 0xE , * | 1 | 1 | 1 | 1 | Cacheable write-back, allocate on both read and write | 0xF , * * AxUSER[1:0] Attribute * 0x0 Non Shareable * 0x1 Inner Shareable * 0x2 Outer Shareable */ Пробовал разные комбинации совместно с тем, что прописано в xil_cache.h. При некоторых комбинациях проц. не зависает, но и данные не пишутся в память. Читал и делал как в AR69446 - Zynq UltraScale+ MPSoC Example Design - Use AXI HPC port to perform coherent transfers Подскажите, как-нибудь можно заставить работать подобную схему? Как правильно настроить кэширование или работать без него, если в нем проблема? Проверял на чипскопе шину S_AXI_HPC0_FPD SLVERR при записи нет.

-

Спасибо, учту!

-

Спасибо, буду копать в этом направлении

-

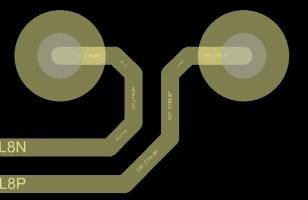

Подскажите, как убрать мелкие фрагменты кусков трасс при дифференциальной трассировке (и не только)? Вместо того, что бы создать прямые линии под 45 градусов лейаут накручивает кучу ненужных изгибов. Хотелось бы: А так сейчас:

-

А если выделить контактные площадки(КП), создать фаноуты, то между КП и переходным отверстием трасса будет шириной, указанной в пользовательской схеме или по схеме мастера?

-

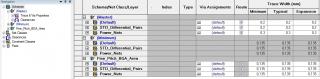

Никак не могу победить Rule Area заданную в CES. Делаю всё стандартно, по гайдам и мануалам, но что-то не выходит. Задача тривиальная: сделать область правил для BGA. Создаю схему в CES, меняю в ней, скажем, толщину трасс, далее импорт в топологию. Затем рисую область и BGA Fanouts ... В итоге, он всё равно рисует трассу от шарика до переходного отверстия такой толщины, которая задана в Schemes -> Master, а должен Schemes -> Fine_Pitch_BGA_Area Подскажите, где косяк? версия VX.2.1

-

-

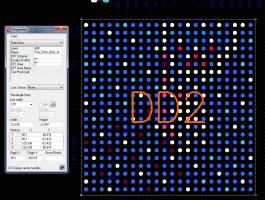

fill, подскажите пожалуйста: есть готовая электрическая схема с ПЛИС, хочу распутать цепи приходящие от ПЛИС к шинам ЦАП и АЦП в xDx I/O Designer перед трассировкой. Возможен ли маршрут xDx Designer -> экспорт в xDx I/O Designer -> оптимизация, экспорт обратно xDx Designer -> xPCB и т.д. без использования HDL & XDC файлов, чисто импорт сигналов из дизайнера? Поковырял Import в I/O, ни в какую. Похоже, что он может импортировать путём import -> constraint manager costraints, но пишет в консоле что всё импортировано, но на деле сигналов никаких нет. # importdesign -idx -toplevel 2M-DES_r0 -mapfile 2MDES_r0 -oatfile 2M-DES_r0 -cddbfile 2M-DES_r0 -refdes DD2 -vendor xilinx -tool {vivado 2016.2} -family artix-7 -device 7a200t -package fbg484 -import_only_assignments -wizard путь/проект.prj {{} {} pcb signals_from_nets default_lib} A pin 'A1' is connected to the electrical net 'ADC_DQd_N0' in the Constraint Manager, but has no equivalent signal in the xDX I/O Designer. A pin 'A11' is connected to the electrical net 'GND' in the Constraint Manager, but has no equivalent signal in the xDX I/O Designer. ... The constraints has been successfully imported. При синхронизации пишет, что всё у него Match и никаких изменений. В чём может быть дело и как правильно делать экспорт в IOD из xDxD?

-

Да, в ЦБ. Спасибо, fill!

-

Подскажите пожалуйста, сделал себе рамку A1 для сборочного чертежа путём импорта dxf-файла автокада в cell editor, присвоил пользовательский слой Fab_titleblock1. Но в редакторе топологии моего проекта этой рамки нет, собственно я сделал ради эксперимента импорт рамки из тренинга, но и этой рамки тоже не оказалось в проекте. Что я упускаю? Я помню, что мне это как-то удавалось, но к сожалению я потёр старый файлы с компьютера :twak:

-

Класс! Спасибо!

-

чёрная магия, благодарю Вас!

-

А можно поподробней, чего-то не работает. Пробовал двумя способами: вручную, через Tools > Types Compatibility и через консоль: changetypescompatibilities -set GND AnalogGND и assign_special GND K9. В строке пин K9 нет сигнала GND.

-

Вопрос: а можно ли, в xDX I/O Designer комбинировать сигналы ПЛИС c типом CONFIG, например с питанием. Или питание разных частей ПЛИС между собой, то же самое относится и к земле. Пример 1: мне нужно закоротить конфигурационный пин, скажем M0 на землю (GND). Я могу это сделать через последовательный резистор, и тогда вопросов нет, как эта часть (от ПЛИС к резистору) обзовётся меня не волнует. А вот что бы напрямую подключить пин к земле, мне нужно объявить его сигналом GND. Но я не могу этого сделать из-за конфликта. Или для этого предусмотрен какой-то более простой способ? Пример 2: У меня есть цепи питание ПЛИС, которые мне бы хотелось объединить между собой, например питание трансиверов MGTAVСС и питание ядра ПЛИС VCCINT от +1 В. Но в один сигнал они ну никак не хотят впихиваться. Аналогично земле, зачем создавать разные сигналы для земли, например для встроенного АЦП, если я его не использую и т.д. Я так понимаю для питания надо редактировать настройку PCB Signal Generation? Из чистого любопытства я переименовал землю АЦП AnalogGND в просто GND, но она по прежнему не хочет добавляться в общий сигнал GND

-

Помогло, спасибо!

-

Дело в том, что у меня уже есть готовый компонент ПЛИС, который уже задействован в проекте. В этом компоненте, есть символ ПЛИС, который я создал из CSV-файла Xilinx. Мне бы хотелось использовать именно свой символ, т.к. я уже создал связи в проекте и мне не хочется заново выравнивать, редактировать УГО, а потом опять соединять его в схеме. Может стоит добавить какие-то дополнительные переменные в символ? У вас он видится из xDX IO Designer'а? В Символах? Хотелось бы пользоваться этой функцией раз она доступна из IO Desiigner'а. Попробую!

-

Спасибо, вроде работает! Ещё вопросик: Хочу импортировать символ ПЛИС, из собственной библиотеки, в xDx IO Designer (через Import -> Symbols from Central Library). Выбираю партишн, после этого пишет ошибку, при этом символа для выбора нет, но видно, что он распознал ПЛИС. После закрытия error: ЛОГ: importlmcsymbol -wizard # logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_A.1 # unrecognized construction at line 37 # |TVRNT 2 508000 2286000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_B.1 # unrecognized construction at line 32 # |TVRNT 2 4826000 1016000 2 2 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_C.1 # unrecognized construction at line 31 # |TVRNT 2 508000 2540000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_D.1 # unrecognized construction at line 31 # |TVRNT 2 508000 1270000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_E.1 # unrecognized construction at line 36 # |TVRNT 2 508000 6096000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_F.1 # unrecognized construction at line 42 # |TVRNT 2 508000 2794000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_G.1 # unrecognized construction at line 31 # |TVRNT 2 4826000 1778000 2 2 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_H.1 # unrecognized construction at line 31 # |TVRNT 2 508000 1270000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_I.1 # unrecognized construction at line 27 # |TVRNT 2 508000 11684000 2 8 logic error in file E:\Dropbox\_projects\MentorGraphics\libraries\mentorlib_v2\SymbolLibs\FPGA\sym\XC7A100TFGG484_J.1 # unrecognized construction at line 26 # |TVRNT 2 3048000 5080000 2 2 Можно как-то решить проблему? sym.rar

-

Уважаемые, подскажите пожалуйста! При заполнении поля Name символов Link, Power или Ground это поле автоматически становится видимым - хорошо, но его постоянно приходится выравнивать. Плюс к этому автоматически становятся видимым и Name цепи, к которой подключён символ, а поскольку названия у них одни и те же, то смысла в этом нет. Что хотелось бы: 1) Найти поле Name в Редакторе символов и сделать выравнивание один раз и навсегда, как это происходит со всеми элементами схемы. 2) Сделать невидимым Name цепи автоматически, а не каждый раз убирать галочку на каждом отрезке цепи...

-

Благодарю! Разобрался, теперь всё хорошо, кроме пробелов: ..SI ...UNIT "micro" ....DISPLAY "мк" ....CASE_SENSITIVE NO ....EXPONENT_VALUE -6 ...UNIT "milli" ....DISPLAY " м" ....CASE_SENSITIVE YES ....EXPONENT_VALUE -3 ...UNIT "none" ....DISPLAY "Ом" ....CASE_SENSITIVE NO ....EXPONENT_VALUE 0 ...UNIT "kilo" ....DISPLAY " к" ....CASE_SENSITIVE NO ....EXPONENT_VALUE 3 ...UNIT "mega" ....DISPLAY " М" ....CASE_SENSITIVE YES ....EXPONENT_VALUE 6 При такой конфигурации получается: Нули и Омы сливаются. Если я ставлю пробел перед Омами: ... ...UNIT "none" ....DISPLAY " Ом" ....CASE_SENSITIVE NO ....EXPONENT_VALUE 0 ... Получается, что программа расставляет пробелы и перед приставками: "4,7 к Ом", что тоже не очень красиво. Можно конечно подобрать шрифт, где нули и буквы "О" разные... Если есть какой-то хитрый трюк или специальный символ, подскажите Спасибо!

-

Здравствуйте! А подскажите пожалуйста, на принципиальной схеме сделанной в xDx Designer в номинальных значениях (Value), скажем резисторов, Ментор сам подставляет Ohms, Kohms и т.д. Когда я убираю омы при следующем заходе он выставляет их снова. Вопрос, можно ли самим редактировать обозначения, например "100 кОм" или просто "100к", без приписки Ohms?

-

Да уж, кто бы мог подумать... Спасибо большое!

-

По ключевым словам "symbol editor" и "xdm library" не нашёл. Если Вам не сложно, ткните носом

-

Благодарю! Подскажите, начал создавать элемент (symbol -> padstack -> cell) всё нормально, но перезашёл в xDM Library и теперь, когда я хочу отредактировать символ мне открывается xDx Designer, вместо Symbol Editor. Вроде настройки связанные с выбором редактора не менял. Как вернуть обратно?

-

Спасибо! Еще вопрос: в Symbol Editor при создании нового символа в окне Pins, столбец Pin Type. При выборе любого из вариантов (IN ... TERM) в графическом окне Symbol при перетаскивании пина программа пририсовывает разные дополнительные символы(Analog - это два треугольника и т.д.). Вопрос: а можно ли отредактировать эти символы или вообще убрать. Например, я хочу сохранить свойство ANALOG для последующего DRC-чека, но мне не нужно графическое отображение этого пина, я хочу просто палку, номер пина и его имя. Спасибо!

-

Привет всем! Подскажите пожалуйста, пересел с Альтиума на Xpedition Enterprise и немного был удивлён. Что-то как-то мало библиотек в открытом доступе. Погуглил, понял что большинство контор сидит на сетевых платных библиотеках или отдельно каждый конструктор рисует всё сам. Но я не сдался, прикрутил PartQuest в связке с DIGIKEYем, но там почти нет символов и футпринтов для шестых, седьмых серий ПЛИС XILINX. Но это меня не остановило, посмотрев ролики от Ментора, я запустил IO Designer, он накачал обновлений и затем я выбрал нужную мне ПЛИСину, генерирую символ, но он идёт без футпринта. Вопрос: можно ли прикрутить в IO Designer схематический символ + футпринт к нему? Ведь как-то он разводит. Извиняюсь за дурацкий вопрос, но после Альтиума как-то непривычно без множества библиотек.