Ezhen

Участник-

Постов

31 -

Зарегистрирован

-

Посещение

Весь контент Ezhen

-

На сайте нашел раздел с package files, в них есть название цепей, пины, принадлежность к банкам и т.д., но нет колонок с задержками, к сожалению. Спасибо за помощь!

-

Коллеги, возникла небольшая проблема с трассировкой DRAM для Zynq-a. Мне надо учесть задержки в корпусе для правильного выравнивания линий в шинах, а достать эти задержки можно только из Vivado. Проблема в том, что чип XC7Z045 не поддерживается в бесплатной версии Vivado и сгенерить на него файл с задержками не получается. На XC7Z030 и ниже получается, а на XC7Z045 и выше - нет. Может кто-нибудь у кого нет таких глупых ограничений сгенерировать и запостить такой файл? Вот инструкции с форума Xilinx, как это сделать в гуи и в TCL консоле: 1) Open any design in Vivado, either RTL, Netlist or Implemented. Then select Export > I/O Ports > CSV. You will see all of the min and max package delays for each pin. The min/max trace delays are also displayed in the Package Pins window for every package pin within two separate columns. Similarly you can select File->Export I/O ports to get a CSV type spreadsheet with the delays included. 2) If there is no project you can use the following Tcl commands: link_design -part <part_number> write_csv <file_name> Для моего случая это по идее будет: link_design -part xc7z045ffg900-2 write_csv flight_time Спасибо за помощь!

-

Ну, народ выше дает и положительные отзывы. Неделю назад оставил заявку на их сайте, пока игнорят. Написал еще в Московский офис Авнет. Подписание NDA небось еще занимает кучу времени, а сроки, как обычно, горят. :laughing:

-

Слишком он избыточный, большой и прожорливый. Доку нашел быстро, но 2004 года. Взял бы более современные чипы Marvell, если бы не NDA. Вроде неплохой чип, но доставаемость похоже не очень. О, вот это нормальный вариант. Точнее даже KSZ9031RNX. Дешевый, доступный, без NDA, простой корпус QFN48, поддерживает 1.8В со стороны RGMII, поддерживает Wake-On-LAN (в отличие от 88e1111) - все что надо. И кушает умеренно. Его наверное и возьму. :santa2: Всем спасибо за наводки!

-

Посоветуйте PHY на 1G без NDA

Ezhen опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Коллеги, посоветуйте PHY на 1G под RGMII и без NDA. Желательно что-нибудь попроще и поменьше, с доступной документацией и нормально доставаемое в штучных партиях. -

Просмотрщик FastStone. Freeware. У него там, в частности, есть набор функций для подрисовывания к имеющимся изображениям.

-

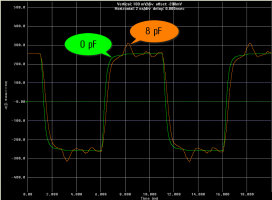

Ну я об этом и говорил. Меандр полезен для проверки линии на конкретной рабочей частоте. А качество согласования линии самой по себе лучше видно на переходном процессе. Да, виноваты паразиты. Изменил входную емкость приемника в ИБИС-модели до нуля и все стало идеально. На рисунке приведены варианты с входной емкостью LVDS приемника 8 пФ (исходная) и 0 пФ. Спасибо, что помогли разобраться!

-

На приемной стороне тоже не совсем все хорошо. Выброс более 10%. Для практики может и нормально, но не понятно откуда взялось. Почему появилось отражение, если все согласовано? Те же LVCMOS ведь согласуются идеально Не могли бы Вы пояснить, почему качество линии лучше выявляется при подаче меандра, а не единичного скачка? Я думал наоборот - проверяя линию по фронту мы, грубо говоря, получаем переходную характеристику линии, в которой увидим до конца весь переходный процесс (все отражения). Это и показывает нам качество всех согласований. А подавать такт полезно, когда надо проверить, как отражения сложатся при конкретной рабочей частоте. Так или иначе, результат для фронта, такта и глазковой диаграммы примерно совпадает. Приложенные графики построены для приемника при той же схеме.

-

Я делал несвязную диф.линию - 50 Ом линии без связи по боковой стороне, т.е. то, о чем Вы говорите. Результат аналогичный.

-

Попытался тут сгенерить IBIS модель в ISE и обнаружил, что LVDS приемники в модель не попадают. LVDS драйверы и всякие LVCMOSы при этом транслируются нормально. Это кривые руки или кривой ISE? Или есть какая-то хитрость? ISE 12.3, Spartan-6. Потом накидал простую схемку в Hyperlynx. LVDS передатчик (модель для Virtex-4) + диф.линия 100 Ом + нагрузка 100 Ом и такой же LVDS приемник (см. рисунок) . Вроде все должно быть согласовано, однако возникают вполне ощутимые отражения. В чем подвох?

-

Понял, спасибо! Вопрос закрыт.

-

Вот, что нашел в документации. Смущают ссылки на SPI и сноска 1 о зависимости от DAP алгоритма. Помогите осмыслить, что все это значит! Нужен ответ на простой вопрос - может ли входной DDR-регистр принимать поток 1024 Мбит/с, а внутренние регистры - работать потом с полученными потоками 512 Мбит/с (хотя бы разделить потоки еще на два, чтобы комфортно было дальше обрабатывать)? Вот эту строчку я и искал. Только ISERDES, все-таки. Значит DDR + ISERDES + аккуратная разводка и будет счастье? Спасибо за быстрый ответ!

-

Virtex-6. Входные DDR регистры.

Ezhen опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую! Есть многоразрядная шина данных. Каждый разряд - 1024 Мбит/с. Есть сопровождающий такт 512 МГц. Данные меняются по обоим фронтам такта (DDR). Всё в LVDS. Можно ли будет напрямую загнать такую шину в Virtex-6 через его DDR-регистры? Не сконфузится ли, так сказать, регистр на такой частоте? :unsure: В документации я убедительного ответа не нашел. Если все-таки можно, то на каждом выходе DDR-регистров будут сигналы по 512 Мбит/с. Получится ли потом распараллелить на такой частоте выходы регистров еще на два используя обычную логику, чтобы в итоге на каждый вход 1024 Мбит/с получить 4 выхода по 256 Мбит/с в каждом? Или в этом случае надо использовать встроенный десериалайзер? Поделитесь соображениями, коллеги! -

Нужна библиотека Virtex 4

Ezhen ответил maxics тема в Библиотеки компонентов

Вот здесь есть. Часть 1. Часть 2. Xilinx_Virtex_4.part01.rar Xilinx_Virtex_4.part02.rar -

Огромное спасибо за совет! Проработаю этот вариант.

-

Да, я так понимаю надо еще привинтить к встроенному трансиверу такое ядро (в случае Xilinx). Тогда внешний PHY уже не нужен и можно сразу с ПЛИС заводить, например, на SFP+ и в оптику.

-

А не помните какое количество вы обещали купить при запросе?

-

В чем для производителя заключается перспективность, если не в количестве? Мы делаем оборудование для специфических научных задач, т.е. всего в нескольких экземплярах. Ну, скажем, нам понадобится 8 таких микрух. Получается, что никто с нами связываться не будет и можно спокойно курить в сторонке? Возможно, все же есть конторы, не требующие NDA на 10G PHY, но я пока не нашел. Кстати, тот же Xilinx дает документацию на ПЛИСины с 10Г трансиверами даже без регистрации на сайте, но сами микрухи дорогущие. Надеюсь, скоро появятся бюджетные Kintex-7 и проблема снимется.

-

10 Gigabit Ethernet PHY

Ezhen опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Всем здравствуйте! Требуется связать ПЛИС с миром по 10G Ethernet (по оптике). ПЛИС со встроенными 10Г трансиверами пока слишком дорогие, поэтому хочу использовать Spartan-6 со встроенными трансиверами на 3.125Гбит и внешний PHY. Соответственно, нужен PHY, где на входе XAUI, а на выходе 10G, уходящий в SFP+. Проблема в том, что производители PHY требуют подписания NDA для доступа к документации и не очень-то торопятся ей делиться, особенно если партия маленькая. Связывался с Vitesse , Applied Micro, PMC Sierra, Broadcom, NetLogic, Marvell. В ответ либо молчание, либо обещания, что со мной свяжутся местные представители (и пока молчание), либо прямой отказ (партия в 10 штук не интересует). Только Марвел обещал прислать NDA, но это может затянуться на несколько недель. :cranky: Поэтому вопрос. Использовал кто-нибудь подобные PHY? Известны ли общественности другие производители PHY на 10GE, кроме перечисленных? А может кто-нибудь и спецификацией поделится (в личку)? И еще вопрос. Стоит ли вводить производителя в заблуждение относительно размера партии при запросе NDA? от скольки штук (или баксов) буржуи заинтересуются? -

Нужна библиотека Virtex 4

Ezhen ответил maxics тема в Библиотеки компонентов

Подойдет? XILINX_SPARTAN_3.rar -

Библиотека Xilix Spartan-6

Ezhen ответил G_A_S тема в Библиотеки компонентов

Вот оно, если еще актуально. Xilinx_Spartan_6.rar -

Нужна библиотека Virtex 4

Ezhen ответил maxics тема в Библиотеки компонентов

Еще актуально? Для какой программы нужна библиотека? -

Взглянуть бы на доки к такой платке. Разрешило бы все споры. Посмотрел специально распиновку на Pentium Core2. Да, там все удобно и с нужной стороны. Чуть ли не больше половины ног отдано под питание и землю. Два внутренних ряда - целиком. Но тем не менее есть стороны процессора, с которых еще 6 рядов отданы не под питание. Я, конечно, не разбирался как там что, но если все 6 рядов надо будет вывести наружу, то в двух слоях сделать это проблематично.

-

Честно говоря, вы меня озадачили. Пойду обдумаю, как развести процессор на несколько сот ножек имея два слоя под сигналы....

-

Я использовал f=0.5/t. Тут вопрос философский, что взять за частоту среза спектра, после которой его амплитуда уже не оказывает влияния. Вряд ли на роджерсе, влетело бы в копеечку. Но не факт, что на простом FR4. Сейчас существует множество ВЧ-материалов, которые обычно используют при проектировании устройств со скоростными последовательными интерфейсами. Повторяю, ВСТРЕЧАЮТСЯ чисто цифровые платы, выполненные на роджерсе и прочих ВЧ-материалах. Это не ширпотреб, это дорогие изделия, где нужно получить высокие характеристики. Посмотрите из чего сделаны оценочные платы для ПЛИС с MGT от фирмы Xilinx или Altera. Можно привести множество других примеров. Почитайте об этом, например, здесь: www.altera.com/literature/an/an528.pdf или просто наберите в поисковике что-нить типа "PCB dielectric materials for high-speed applications" А вы знаете ТОЧНО, на чем сделаны современные материнки? одно с другим связано. Но корректнее, наверное, говорить о полях. Спасибо за поправку! Вы передаете не синус, поэтому вам важна не частота основной гармоники, а ширина всего спектра, зависящая, как мы выяснили, от скорости нарастания фронта. Посчитайте верхнюю частоту спектра и именно по ней оценивайте какая у вас линия - длинная или нет. Кстати, очень полезно на всякий случай посчитать, не создано ли у вас условий для синфазного резонанса в диф.линии. Если время задержки распространения сигнала от передатчика до приемника составит четверть тактового периода, то лучше либо укоротить, либо удлинить линию, а то можно получить резонанс по синфазной помехе. Маловероятно, конечно, но вдруг. Именно так. Но про микрополосковую структуру сразу можно сказать, что на практике обеспечить стоомность линии приблизив дорожки друг r другу и подняв их над опорой настолько, чтобы связь между дорожками была сильнее, чем связь между каждой из дорожек с опорой - достаточно сложно, если вообще возможно. можно даже рассчитать условия, но надо тратить на это время. Попробуйте поиграться с калькуляторами импеданса, которые показывают коэффициент связи дорожек, и найти стоомную конфигурацию, при которой связь будет хотя бы больше 50%. Еще раз спасибо всем участникам дискуссии! К сожалению, вопрос с трансформатором так и повис неразрешенным. Уж скоро я все проверю на практите. :)