confflex

Участник-

Постов

29 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о confflex

-

Звание

Участник

Посетители профиля

696 просмотров профиля

-

Проблема решилась (скорее всего временно), путем создание своего Linker script'а на базе того, который генерируется автоматически (назначением нового диапазона адресов для секций памяти stack и heap). С увеличением объема программы глюки при передаче пакетов через ethernet повторились, но уже и при загрузке через JTAG. Начал исследовать то, как линкер создает "карту" памяти и нашел в nios2-gnutools утилиту nios2-elf-ld, которая выдала следующее (memorymap.png): а утилита nios2-elf-objdump (objdump.png): Каким образом можно избежать перекрытия секций памяти? и есть ли они в моем случае?

-

Под времянками понимается Fmax после разводки (здесь всё вроде нормально) и констрейны для SDRAM (здесь нет 100% понимания, но я всегда пытался "грешить" на SDRAM, но ни разу не нашёл подтверждения этому, тесты SDRAM проходили, были попытки "зацепится" за что то путём тупой переразводки в Квартусе после незначительных изменений в проекте, переразводка ни на что не и разу не повлияла.)? Про фокусы с кэшем можно подробней? так когда с EPCS гружу как JTAG (printf) использовать?

-

Плата самодельная, ещё с теми извратами не по моей вине. :( В том то и дело что у меня всё стабильно. Стабильно через JTAG работает как надо, и стабильно из EPCS работает не верно. Неправильность заключается в том, что обмен пакетами через Ethernet прекращается стабильно с 3-й попытки. Т.е. если бы при переедёргивании питания каждый раз было бы по-разному, грешил бы на питание.

-

XP SP3 32bit

-

лог после nios2-flash-programmer --verify --epcs --base=адрес имя_файла.flash Using cable "USB-Blaster [uSB-0]", device 1, instance 0x00 Restetting and pausing target processor: OK Verified 91KB in 2.6s <35 KB/s> Leaving target processor paused Как я понимаю все нормально !? До этого я пытался сливать файл командой nios2-flash-programmer --read и сравнивать файлы по содержимому. Ничего не получалось. Как тогда могут по разному работать проекты из EPCS и через JTAG? Ещё вопрос по максимальному размеру программы для НИОСа, кот. можно загрузить в EPCS16. EPCS16 имеет размер памяти 16777216 бит, EP1C12 имеет максимальный размер загрузочного файла - 2323249 бит, т.е для программы ниоса остается 14453967 бит (~ 1.7МБ). Это теоретически, а как практически?

-

Привет всем! Прошу помощи! Сделал проект Cyclone EP1C12, EPCS16, память программы - SDRAM. Пока размер программы был небольшой, проблем не возникало т.е программу отлаживал чераз JTAG и грузил в EPCS. Различий в выполнении программы по JTAG и из EPCS по включению питания не наблюдалось. Программа увеличилась в размерах, в итоге был получен вариант, нормально работающий при загрузке через JTAG (т.е. из квартуса грузил sof - файл, из эклипса - программу для ниоса). После прошивки EPCS16 и передергивания питания проект работает, но наблюдаются баги. При повторной загрузки программы для ниоса через эклипс - все ок. Баги связанны с пересылкой пакетов через ethernet. Версия квартуса 9.0 (при установке sp2 - результат тотже). Не понятно в какую сторону "копать": то ли это некорректный программный код или проект для квартуса, то ли неадекватная запись/чтение из/в EPCS? ЧИтал дамп EPCS, но не смог сравнить с исходным (размер слитого флеш файла ~4.8Мб, а исходного ~270Кб). Как понять адекватность загрузки в EPCS через flash programmer. И еще одно: при программировании через flash programmer получен следущий лог (привожу часть) # Creating .flash file for the FPGA configuration "$SOPC_KIT_NIOS2/bin/sof2flash" --epcs --input="xxx.sof" --output="xxx.flash" Info: ******************************************************************* Info: Running Quartus II Convert_programming_file Info: Command: quartus_cpf --no_banner --convert --device=EPCS128 --option=xxx .opt xxx.sof xxx.pof Почему EPCS128? Будут у кого какие соображения?

-

Спасибо за ссылку, симтомы очень похожи на указанные в теме. Reduce device drivers и Small C Library действительно использую, когда в on-chip RAM код пихаю. Но при работе с SDRAM снимал соответствующие галки, чуть ли не все варианты перебрал :) . Хотя завтра обязательно ещё попробую.

-

Какими таймингами? Расскажите подробней, пожалуйста. Требования к значению тактовой частоты выполняется. С настройками и констрейнами для SDRAM не уверен, но тестировал записью-чтением, а потом даже пробовал вместо SDRAM использовать on-chip RAM.

-

vadimuzzz Спасибо за ответ. DMA пока не использую. А ссылки нельзя на темы, где народ на глюки софта жаловался?

-

Зависание Nios

confflex опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Приветствую Всех! Прошу помощи, может кто встречал подобное? Имею самопальную плату с Cyclone. Сконфигурирован NIOS\f, SDRAM 16 bit, On-Chip RAM, jtag uart, PIO, Timer, пара своих контроллеров. Quartus 9.0. Зависание Nios при изменении программы. То есть, например, всё правильно работало, выводило на печать сообщения или значения какой-нибудь переменной в консоль через JTAG. Добавляю ещё printf.., причём в конце или начале основной программы, т.е. логически никак не должно связано с основной программой, и.. происходит либо зависание NIOS (выводит часть сообщений на консоль, другие не выводит, при пошаговом выполнении вижу, что зависает), либо происходят неправильные вычисления (неправильное значение получается одно и то же, т.е. не случайно, а жёстко фиксировано), хотя до ввода printf, всё было Ок. Первым делом стал винить SDRAM, но вставленный код для тестирования большого сегмента данных всегда проходил без ошибок, попробовал использовть on chip RAM, то же самое. Ни какие манипуляции по переразводке в Квартусе или переконфигурировании системы в SOPC при зафиксированном неправильно выполняемом СИшном коде, не приводят ни к каким результатам. Убирал PLL, снижал частоту системы, без изменений. Коментирую некую строку с printf, всё нормально. -

да

-

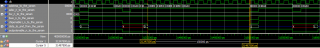

Я, как и ROMЫ4, создавший эту тему, "удивился,что скорость маленькая". К сожелению понятных ответов я не увидел, может ROMЫ4 спрашивал как то не так? Спрошу тогда я по-своему, может кто знает? Отсимулировал я проект работы с SSRAM, который выложил vadimuzzz, и получил при тактовой частоте 80 MHz следующее Также отсимулировал сборку NIOSa-fast, кот. меня ещё больше интересует: тактовая 50МГц, память программ и данных в SDRAM 16-бит, обмен с асинхронной SRAM, обмен для примера происходит так: while (1) { IOWR_32DIRECT(SRAM_0_BASE, 0, 9); IOWR_32DIRECT(SRAM_0_BASE, 4, 10); IOWR_32DIRECT(SRAM_0_BASE, 8, 11); IOWR_32DIRECT(SRAM_0_BASE, 12, 12); IORD_32DIRECT(SRAM_0_BASE, 0); IORD_32DIRECT(SRAM_0_BASE, 4); IORD_32DIRECT(SRAM_0_BASE, 8); IORD_32DIRECT(SRAM_0_BASE, 12); } Получил следующие результаты: В связи с этим вопросы: 1) Можно как-то ускорить обмен с SRAM без DMA? Понимаю, что больше всего обмен тормозит 16-бит память программ и данных, думал, что кэширование инструкций как-то эффективней будет работать. Может что не так делаю? 2) Как работать с ДМА? Пробовал пример из Quartusa 9.0 memtest.c, что то не заработало. Может кто покажет, как надо сделать программу отдельно для записи в SRAM и отдельный пример для чтения из SRAM.

-

Altera DE1(2)

confflex опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую Всех! Прошу заранее извинить, если не очень в тему. Мне нужна отладочная плата на Cyclone 1, 2, 3 с SRAM и SDRAM (не DDR). Подходит Altera DE1(2), но не нашёл, где купить в Москве (собираюсь приехать для покупки за наличные). Вроде бы эти платы устарели? Может кто подскажет альтернативную плату или кто-то уже наигрался, и сможет продать? -

Может кто наигрался? Забыл... в Москве. Пишите в личку.

-

Вы использовали "правленный" picoblaze в асиках? Может выложите исходники, а мы для Альтеры попробуем.