nkie

Участник-

Постов

33 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о nkie

-

Звание

Участник

- День рождения 08.03.1984

Контакты

-

Сайт

Array

-

ICQ

Array

-

FEC на ПЛИС

nkie ответил des00 тема в Языки проектирования на ПЛИС (FPGA)

Возможно мой вопрос покажется глупым, но я пытаюсь разобраться в SystemVerilog и тестбенчах. Пример из обсуждаемого здесь проекта: rs_enc #( .n ( n ) , .check ( check ) , .m ( m ) , .irrpol ( irrpol ) , .genstart ( used_genstart ) ) uut_enc ( .iclk ( iclk ) , .iclkena ( iclkena ) , .ireset ( ireset ) , // .isop ( isop ) , .ieop ( ieop ) , .ieof ( ieof ) , .ival ( ival ) , .idat ( idat ) , // .osop ( enc__osop ) , .oval ( enc__oval ) , .oeop ( enc__oeop ) , .odat ( enc__odat ) ); Взято из файла тест бенча rs_eras_enc_dec_tb.v Что означает rs_enc #( .n ( n ) , .check ( check ) , .m ( m ) , .irrpol ( irrpol ) , .genstart ( used_genstart ) ) Понятно что uut_enc - наследник или копия модуля rs_enc, но за что отвечает здесь #(...)? все разобрался, передача параметров... -

Уважаемый des00, а не могли бы вы у себя в блоге, как будет время немножко свободного, набросать небольшую статейку о полном цикле разработки модели. Т.е. от разработки RTL-модели, написания тестбенча, проведения моделирования и верификации на примере всем известного БЧХ-декодера. Не обязательно подробно, хватило бы даже коротко остановиться на основных вехах. С помощью каких утилит и инструментов выполнялось то или иное действие, основные подводные камни, поджидающие разработчика на том или ином этапе. Для новичков такое описание очень бы помогло.

-

хм... да действительно. А не посоветует кто-нибудь какого нибудь ресурса, где можно по-подробнее почитать от начала до конца от процесса создания RTL-модели до его верификации, на каком-нибудь примере желательно. В идеале на русском, но сойдет и на английском.

-

[Тихо сам с собой виду беседу] Все, решил проблему, с компилятором все нормально, были синтаксические ошибки в коде. По ходу ознакомления с кодом des00 возникло очередное недопонимание. В файле bch_enc_dec_tb.v описывается класс class data_trans; А Quartus 9.1 говорит что он класы не поддерживает Значит они обманывают, и классы все таки поддерживаются?

-

Не стал создавать новую тему, вопрос в сущности в том же самом. Пытаюсь ввести в свою профессиональную жизнь такой интересный язык как SystemVerilog, со всеми его плюшками. Установлен Quartus II 9.1 без SP-ов. В настройках проекта во вкладке Verilog HDL Input стоит выбор на SystemVerilog-2005. Расширение файла проекта *.sv (пробывал и *.v). В проекте пробывал использовать различные конструкции SystemVerilog-а, структуры типа: struct { int a; byte b; bit [7:0] c; } my_data_struct; my_data_struct.a = 123; интерфейсы... и т.д. Короче на все это Quartus ругается таким же образом, типа Error (10170): Verilog HDL syntax error at my_sv.sv(14) near text "="; expecting ".", or "(" Error (10170): Verilog HDL syntax error at my_sv.sv(23) near text "interface"; expecting "endmodule" Складывается впечатление, что не удается подключить SystemVerilog-овский компилятор. Не подскажет кто нибудь, может еще какие-то настройки нужно изменить или проверить наличие каких-нибудь библиотечных файлов, может быть SP нужно установить... Заранее спасибо...

-

Спасибо большое за помощь. Значит будем переразводить.

-

Тоесть заставить микросхему работать без этого питания невозможно, даже если я не использую PLL?

-

цифровое питание PLL в Cyclone III

nkie опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте, господа форумчане. У меня следующая проблема. На плате используется плисина CYCLONE III EP3C40F780C8. Это 780-ножечная микросхема в MBGA-корпусе. Во время разводки была допущена ощибка. Цифровое питание PLL (пины VCCD_PLL[1..4]- Y9,J20,J9,Y20) были посажены на землю (по даташиту должно быть 1.2В). В связи с этим плисина не функционирует. Загрузка прошивки проходит нормально, выставляет все соответствующие биты, но программа не работает. Вопрос в том, можно ли каким-нибудь образом заставить микросхему работать без использования PLL. Возможно где-нибудь в настройках Quartus это отключается. В хэндбуке не нашлось ничего, кроме того, что это питание необходимо подключать даже если вы не собираетесь использовать PLL. ЗЫ: проблема точно в PLL, т.к. была проведена проверка на другой плате с рабочей микросхемой в TQFP-корпусе. Та же ножка поднята и посажена на землю, симптомы повторились. Заранее спасибо. -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

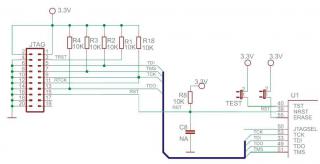

Добрый день. Перепаял процессор, в системе он определяться не начал. Винда все также не может инициализировать девайс. Кое-какие подвижки с JTAG-ом все-же появились. В Кейле по команде "Erase chip" выдает "Full Chip Erase Done", правда через раз:(. Прошить же вообще не выходит, выдает ошибку(рис.2). Схема JTAG-a выглядит так(рис.1). Проц на этот раз должен быть живой, паял не сам, отдавал профессионалам. Что-же все это может значить? И как правильно все-таки поступить с сигналом JTAG_SEL? В даташите советуют либо на землю вешать, либо оставлять в воздухе. НА некоторых схемах его притягивают к питанию... -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

Ну с МК то точно проблема, но то что SAM-BA вылетает никак не может быть связано с контроллером И это уже другая проблема... -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

Например чем? Вот с этим как раз у меня проблемы. Поставил SAM-BA, а она при запуске вылитает с ошибкой от Microsoft Visual C++. Кто-нибудь встречался с такой проблемой? Как побороть? Может снести этот Microsoft Visual C вообще? -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

Кварц пробовал менять, не помогает. Вот решил перепаять проц. Единственная проблема, что остались только AT91SAM7S128, и боюсь что выкладываемые здесь прошивки в него не зальются. Другой размер страницы флеша. AT91SAM7S64 - 64 кбайт, 512 страниц по 128 байт AT91SAM7S128 - 128 кбайт, 512 страниц по 256 байт Или я ошибаюсь? -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

какой из них? Разъем на самой плате, да мы эти разъемы везде ставим. никогда проблем с ними не было... На компе подключал разными кабелями к разным портам. Кстати странная особенность. При включении к новому ЮЗБ порту система видит девайс, подключает его, что-то там делает (рис.2), но потом выводится сообщение о невозможности определения устройства(рис.1). Спаял переходник с 20-пинового ULINK-ого JTAG-а на 8-пиновый. Возникла небольшая проблема, на 20-пиновом 2 ресетных сигнала, подпаивал к каждому поочереди. Попробывал через JTAG прошить пример из Кейла, не выходит. Не могу даже стереть флэш. Такое ощущение что программатор не видит девайс. Так что либо у меня кривые руки, не правильно распаян переходник, либо пациент скорее мертв чем жив... -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

Да вроде все правильно, 55 пин подтягиваю на 1 секунду к питанию, выключаю, подтягиваю 40 пин к питанию, включаю на 20 секунд. Что здесь можно делать не правильно? Да и ULINK-a разъем другой, нужно переходник спаивать. -

China-Link, Вариант отладчика из Китая

nkie ответил krestnick тема в Отладочные платы

Подтянут уже, все равно не работает. Кстати, на некоторых схемах, да и в даташите, D+ подтягивается через 1.5к к PA16. На выкладываемых здесь схемах подтягивается к PA28. Это принципиальный момент или как? Еще этот момент видел через транзистор реализовывается. Еще на кварце нет никакой активности. Висит по 0.5В на обеих ногах и все. А кстати, как-нибудь можно проверить, работоспособный ли проц? Есть программатор ULINK с Кейлом, может через JTAG можно подрубиться, и глянуть что-нибудь?