Viper89

Участник-

Постов

16 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Viper89

-

Звание

Участник

- День рождения 29.03.1989

Контакты

-

Сайт

Array

-

Вопрос про слои МПП

Viper89 ответил Viper89 тема в Работаем с трассировкой

Класс точности скорее всего будет 5-й. Многие дифф пары занимают 3- 4ряды, все первые заняты на 100%( не хотелось бы увеличивать число переходных отверстий при разводке дифф сигнпалов) -

Вопрос про слои МПП

Viper89 ответил Viper89 тема в Работаем с трассировкой

vicnic, Uree спасибо за ответы! To Uree 1.2 В и смешанные 5В вправду можно в одном слое объединить что-то я сразу внимания не обратил, а разбросать думаю придется сообразить (у каждой ПЛИС своя отдельная микросхема питания, получается 6 питаний по 1.2В, и столько же по 2.5В,но все это локально). To vicnic: 1. Больше всего меня волнуют дифф пары) Другие цепи разбросаю по возможности. Внешние слои забыл указать фольга 18мкм+35мкм металлизация. внутренние сигнальные думаю оставлю 35мкм, иначе ядра не симметричные получаются. Вне BGA могу ли я задать для питаний переходные отверстия большего размера? Касательно дифф пар я так понимаю везде как под BGA? -

Вопрос про слои МПП

Viper89 ответил Viper89 тема в Работаем с трассировкой

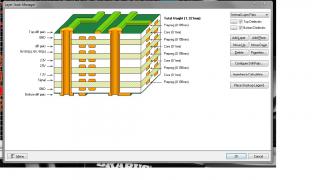

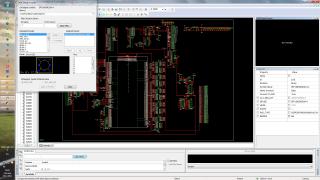

Здравствуйте! Пытаюсь разобраться с структурой ПП и волновым сопротивлением для своего проекта( 6 BGA484 циклон3, имеется BLVDS , почти 80% всех цепей-дифф пары с заданным волновым сопротивлением 100 Ом, 7 сотен резисторов и 3 сотни кондеров). Вроде многое понятно, но все же имеется несколько вопросов. 1. Структура такая. ядра 0.1\35\35, препрег 2116. Или же есть более лучший вариант? 2. Какую толщину H1 указывать для внешнего слоя в калькуляторе Polar. Я так понимаю номинал 0.105мм после прессования изменится. Предварительно указав номинал получил такие результаты для внешних слоев. 3. Где и какие допуска нужно обязательно включать в расчет? 4. Плата будет покрыта маской, вроде в Polar есть coated вариант, только там надо задать значения с1,с2,с3. Какие? 5. При разводке некоторые дифф. пары будут с переходными отверстиями, можно ли использовать стандартные к примеру диаметром отверстия 0.4 или 0.6 или их тоже надо просчитать? Заранее спасибо за помощь! -

Владимир, интересно узнать что Вы имели ввиду под этим "Tool/interactive matclendht difpair"?

-

Здравствуйте! Пришла схема на 6 BGA Altera по 484 ножек, порядка 750 резюков, 260 конденсаторов, ну и 2 десятка микросхем.Размеры платы с лист А4. Основная масса соединений-диф.пары, которые я должен развести с волн сопротивлением 100 Ом. Опыта разводки дифф. пар и BGA у меня нет, поэтому хотелось получить помощь по вопросу настройки Альтиума для разводки соединений с данным волн сопротивлением. Как его настроить, что для этого необходимо? Чем и как вести расчет размеров проводника? Можно ли автоматизировать процесс в Альтиуме и интерактивно развести дифф пары с уже расчитанными параметрами? Сам же наткнулся на impedance calculation, но так и не понял как пользоваться данным инструментарием. Заранее спасибо за помощь!

-

Вопрос про слои МПП

Viper89 ответил Viper89 тема в Работаем с трассировкой

Спасибо всем ответившим...2 vicnic естественно разница в стоимости есть, в этом нет сомнений. Проблема в корпусе ПЛИС..Каким-то образом надо уместить посадочное место неотформованной металлокерамики CQFP240 на плате шириной 41 мм (максимум). Почитав здесь http://www.pcad.ru/forum/61815/ засомневался в применении ее в устройстве...Возможно кто-то работал с 5576ХС1Т, может поделиться своим мнением по этому поводу? Схемотехники хотели по началу пойти на увеличение кол-ва слоев в плате и все же как-то уместить ее на плате, но здесь проблема в том что расстояние от края платы до края контактной площадки очень мало, если сужать посадочное место(чего мне бы делать вообще не хотелось). теперь они думают на схемой, считаю необходимым менять плис. Пока они думают прорабатываются любые варианты... ClayMan, по началу я тоже так предполагал сделать, но мне показалось что 3-х сигнальных слоев будет мало...если сужать посадочное место( хотя маловероятно что это случиться) то все проводники сверху и снизу корпуса уйдут через переходные отверстия под корпусом в слои... А так предыдущий вариант платы был именно 6-ти слойным...разница в том что в нынешнем варианте новая ПЛИС и большее количество микросхем которые с ней связаны. -

Вопрос про слои МПП

Viper89 ответил Viper89 тема в Работаем с трассировкой

в количестве слоев я не ограничен, в отличие от габаритных размеров, а количество связей не мало,что Вы думаете о такой структуре : 1. топ 2. gnd 3. 3.3 v 4. signal 5. 5v 6. gnd 7. 9-12 v 8. signal-bottom или же стоит все сигнал расположить внутри? -

Вопрос про слои МПП

Viper89 опубликовал тема в Работаем с трассировкой

Здравствуйте ! Уважаемые знатоки, прошу помочь определиться с расположением слоев в МПП. Имеется 4 питания: 3.3В, 5В, 9В и 27 В. В составе платы ПЛИС 5576ХС1Т, загр ПЗУ 5576РС1У, Flash AT49BV040-JU, несколько микросхем 1533, 1309 и кренка т.д. Раньше с МПП не сталкивался, платы были проще. Каков будет порядок слоев и как мне быть с GND, нужно ли делить его на землю питания и на цифровую землю(просто в схеме все на одну землю посажено) и в каких случаях она вообще делиться на AGND и DGND? Надеюсь на Вашу помощь, заранее спасибо! ps: плис cqfp240 -

с keyin netlist пока не сталкивался. я имею ввиду написать этот нетлист самому, согласно электрической схеме, чтобы не заниматься рисованием в DXdesigner и начать работу уже непосредственно в Layout.

-

Понятно...Vitan,a есть ли в менторе решение аналогичное файлу .alt P-CAD, может вовсе не обязательно рисовать электрические схемы, а достаточно создать посадочные места и загрузить подобный файл в Layout?

-

Ладно, видимо никто не встречался с этой проблемой...пытаюсь сам разобраться ...и назрел вот такой вопрос -что такое WIR файл и откуда он берется? и каковы могут быть причины того что его нет в положенном месте?

-

ClayMan и vitan благодарю за оперативный ответ) Сегодня попытался создать нетлист и перейти непосредственно к layout, вылезли непонятные 2 ошибки при создании нетлиста... 1)pcb: Warning 5720: Check Schematic1.err for VIEWBASE messages pcb: Error 5709: Could not open schematic Schematic1 pcb: Note 5626: Summary of pcb1.err Status 0, Notes 1, Warnings 1 Errors 1, Failures 0, Fatals 0, Internals 0 2)viewbase: Error 222: Error - Could not find WIR file SCHEMATIC1.1. в Error datashite вот что пишется по поводу первой PCB-5709 Message: Could not find ViewPlace database for [object]. Cause: The ViewPlace database required for the specified object could not be found. Solution: If the object is a board, there is no design.brd file in the brd directory. Use the -CreatePlacementData option in the command line to create a board database. If the object is a shape, the symbol shapes cannot be found in the viewplac.ini search order. Check your viewplac.ini file.( видимо какого-то database не хватает...не ясно какого, попробовал через командную строку проделать-в итоге output пишет что-нет такой команды) Кто-нибудь сталкивался с этим?) что я забыл сделать?) по поводу второй ошибки ничего не нашел...

-

Начал разбираться с Databook...В нарисованной схеме имеются несколько конденсаторов для которых одно УГО и несколько посадочных мест...При назначении одного УГО одним посад. местом остальные кондеры принимают тот же вариант посадочного места( но должен быть другой). Моя попытка разобраться в этом непорядке с Databook оказалась не успешной. меня интересует следующее: 1. правильно ли я понимаю чтобы присвоить посадочные места нужно самому вручную создавать таблицу Microsoft access, где будут прописаны все возможные пары УГО-Посадочное место компонентов необходимые для моего проекта? 2. Или же есть возможность непосредственно в Databook осуществить замену PKG_Type интересующего меня УГО ? ( что-то наподобие нового компонента в таблице с тем же УГО но с др. PKG_Type) 3. А возможен ли вариант просто пройтись по всем УГО на схеме и каждому в Properties задать необходимый PKG_Type ? Не будет ли потом конфликта с Databook при передаче в Layout ? Сколько GUIDE я не читал, но так и не разобрался, надеюсь на вашу помощь! Заранее спасибо!

-

До layout я пока не дошел... Может проблема еще в том что Databook не настроен для проекта...с ним я пока тоже не работал.

-

Здравствуйте! Подскажите пожалуйста почему в DXD когда на схеме выделяется УГО Decal Browser не находит для него посадочное место, если я через симбол эдитор->tools->pads decal browser задал для этого УГО посадочное место. В чем может быть проблема? актуально для WinXP SP3 и WIN7/ весь проект и library лежит на флэхе, программа на С. Было замечено что после переустановки программы все в порядке и все отображается некоторое время а потом снова появляется эта проблема. Есть ли взаимосвязь? Может что-то сам не то сделал. Заранее спасибо!